用于制作NAND存储器装置的分层半导体结构的方法与流程

本公开总体上涉及半导体,更具体地涉及用于对nand存储器中的双重编程错误除错的方法。

背景技术:

1、随着存储器装置缩小到更小的管芯尺寸以降低制造成本并且提高存储密度,平面存储器单元的缩放因工艺技术限制和可靠性问题而面临挑战。三维(3d)存储器架构能够解决平面存储器单元中的密度和性能限制。

2、在3d nand闪速存储器中,可以垂直堆叠设置很多层的存储器单元,从而能够极大地提高单位面积的存储密度。垂直堆叠设置的存储器单元能够形成存储器串,其中,每一存储器串中的存储器单元的沟道被连接起来。每一存储器单元可以通过字线和位线受到寻址。共享同一条字线的整个存储器页中的存储器单元的数据(即,逻辑状态)可以同时受到读取或编程。然而,由于激进的缩放的原因,可靠性会是3d nand闪速存储器的一个顾虑。

技术实现思路

1、在本公开中描述了用于存储器装置中的数据保护的方法和系统的实施例。

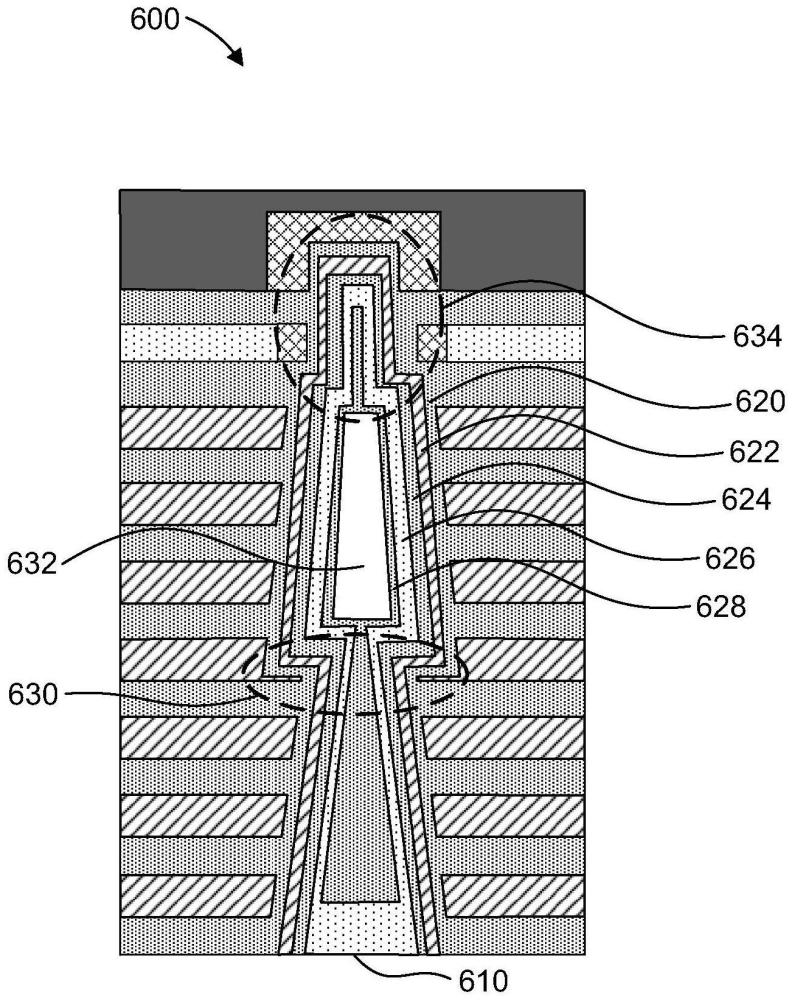

2、在一些实施例中,一种制作方法能够制造用于nand存储器装置的具有提高的可靠性的半导体结构。该方法可以包括形成包括第一层、设置在第一层上的第二层和设置在第二层上的第三层的半导体结构。该方法还可以包括形成沟道结构,其可以包括通过该半导体结构的表面蚀刻第一层、第二层和多晶硅层,以形成开口。可以在该开口处露出第三层的部分。该沟道结构的形成还可以包括氧化第三层的露出部分,从而基于该氧化形成扩大第三层的露出部分的氧化硅。

3、在一些实施例中,该氧化可以包括使用湿法氧化工艺。

4、在一些实施例中,扩大多晶硅层的露出部分可以使该开口的部分变窄。

5、在一些实施例中,该方法还可以包括在该开口处设置第一沟道层。该方法还可以包括在该开口内并且在第一沟道层上设置第二沟道层。第二沟道层可以具有第二硅化合物。该方法还可以包括在该开口内并且在第二沟道层上设置第三沟道层。

6、在一些实施例中,扩大第三层的露出部分使该开口的部分变窄。所述第一、第二或第三沟道层的设置可以阻塞该沟道的窄化部分。

7、在一些实施例中,该方法还可以包括在该沟道结构内设置第四和第五沟道层。

8、在一些实施例中,该方法还可以包括形成沟道末端结构。该形成可以包括在该开口处设置第一沟道层。该形成还可以包括在该开口处并且在第一沟道层上设置第二沟道层。该形成还可以包括在该开口处并且在第二沟道层上设置第三沟道层。所述沟道末端结构可以包括基于第三层的扩大的露出部分的瓶颈截面。

9、在一些实施例中,形成该半导体结构可以包括形成用于第一层的一层氧化硅。

10、在一些实施例中,形成该半导体结构可以包括形成用于第二层的一层氮化硅。

11、在一些实施例中,该氧化可以包括使用具有高于大约600摄氏度并且低于大约800摄氏度的温度的气体执行湿法氧化工艺。

12、在一些实施例中,该氧化可以包括使多晶硅层的露出部分暴露在氢气和氧气下。

13、在一些实施例中,氢气与氧气的比率可以大于大约0.14并且小于大约7.00。

14、在一些实施例中,该氧化还可以包括使多晶硅层的露出部分在长于大约0.5小时并且短于大约12.0小时的持续时间内暴露至氢气和氧气。

15、在一些实施例中,该氧化可以包括使第三层的露出部分暴露至氮气。

16、在一些实施例中,该半导体结构可以包括至少固定至该第一层的牺牲层。所述蚀刻还可以包括蚀刻该牺牲层。

17、在一些实施例中,该方法还可以包括在该沟道结构的开口处设置第一沟道层。第一沟道层的部分可以被设置到该牺牲层的受到蚀刻的部分当中。

18、在一些实施例中,该方法还可以包括将该半导体结构键合至cmos结构。该牺牲层被设置为与该半导体结构和该cmos结构的键合界面相对。

19、在一些实施例中,一种制作方法能够制造用于nand存储器装置的具有提高的可靠性的半导体结构。该方法可以包括将该半导体结构制作为包括牺牲层、第一层、第二层、第三层和沟道结构,该沟道结构被设置为至少与所述第一层、第二层、第三层和牺牲层相交。该沟道结构可以包括空洞和窄化部分。该方法还可以包括去除该牺牲层。牺牲结构的去除可以包括去除沟道结构的被设置为与该牺牲层相交的部分。该方法还可以包括去除第一层,从而露出第三层和沟道结构的窄化部分。基于窄化部分阻塞了通往沟道结构的空洞的通道而防止了因去除该牺牲层而产生的材料进入该空洞。

20、在一些实施例中,该方法还可以包括蚀刻掉第一层和第二层的被设置为接近沟道结构的窄化部分的部分。

21、在一些实施例中,该方法还可以包括将多晶硅设置到该半导体结构上,以形成与该沟道结构的多晶硅结构的接触部。

22、在一些实施例中,牺牲层的去除还可以包括使用化学机械抛光工艺。

23、在一些实施例中,第一层的去除可以包括使用化学机械抛光工艺。

24、在一些实施例中,提供了一种用于nand存储器装置的具有提高的可靠性的半导体结构。该分层半导体结构可以包括多晶硅层、氧化硅层、氮化硅层和沟道结构。沟道结构可以具有被设置为至少与所述多晶硅、氧化硅和氮化硅层相交的长度。沟道结构可以包括具有垂直于该沟道的长度定义的宽度的宽部分。该宽部分可以被设置为至少与所述氮化硅层相交。沟道结构还可以包括具有垂直于该沟道的长度定义的宽度的窄部分。窄部分可以被设置为至少与多晶硅层相交。窄部分的宽度可以小于宽部分的宽度。

25、在一些实施例中,提供了一种具有提高可靠性的分层半导体结构的nand闪速存储器装置。该nand闪速存储器装置可以包括半导体结构。该半导体结构可以包括多晶硅层、氧化硅层、氮化硅层和沟道结构。沟道结构可以具有被设置为至少与所述多晶硅、氧化硅和氮化硅层相交的长度。沟道结构可以包括具有垂直于该沟道的长度定义的宽度的宽部分。该宽部分可以被设置为至少与所述氮化硅层相交。沟道结构还可以包括具有垂直于该沟道的长度定义的宽度的窄部分。窄部分可以被设置为至少与多晶硅层相交。窄部分的宽度可以小于宽部分的宽度。

26、在一些实施例中,提供了一种具有提高可靠性的分层半导体结构的存储器系统。该存储器系统可以包括nand闪速存储器装置。该nand闪速存储器装置可以包括半导体结构。该半导体结构可以包括多晶硅层、氧化硅层、氮化硅层和沟道结构。沟道结构可以具有被设置为至少与所述多晶硅、氧化硅和氮化硅层相交的长度。沟道结构可以包括具有垂直于该沟道的长度定义的宽度的宽部分。该宽部分可以被设置为至少与所述氮化硅层相交。沟道结构还可以包括具有垂直于该沟道的长度定义的宽度的窄部分。窄部分可以被设置为至少与多晶硅层相交。窄部分的宽度可以小于宽部分的宽度。

27、本领域技术人员根据本公开的说明书、权利要求书和附图能够理解本公开的其他方面。

技术特征:

1.一种方法,包括:

2.根据权利要求1所述的方法,其中,所述氧化包括使用湿法氧化工艺。

3.根据权利要求1所述的方法,其中,扩大所述多晶硅层的露出部分使所述开口的部分变窄。

4.根据权利要求1所述的方法,进一步包括:

5.根据权利要求4所述的方法,其中:

6.根据权利要求4所述的方法,进一步包括在所述沟道结构处设置第四沟道层和第五沟道层。

7.根据权利要求1所述的方法,进一步包括形成沟道末端结构,包括:

8.根据权利要求1所述的方法,其中,所述形成所述半导体结构包括形成用于所述第一层的一层氧化硅。

9.根据权利要求1所述的方法,其中,所述形成所述半导体结构包括形成用于所述第二层的一层氮化硅。

10.根据权利要求1所述的方法,其中,所述氧化包括使用具有高于大约600摄氏度并且低于大约800摄氏度的温度的气体执行湿法氧化工艺。

11.根据权利要求1所述的方法,其中,所述氧化包括使所述多晶硅层的露出部分暴露至氢气和氧气。

12.根据权利要求11所述的方法,其中,所述氢气与所述氧气的比率大于大约0.14并且小于大约7.00。

13.根据权利要求11所述的方法,其中,所述氧化进一步包括使所述多晶硅层的露出部分在长于大约0.5小时并且短于大约12.0小时的持续时间内暴露至所述氢气和所述氧气。

14.根据权利要求11所述的方法,其中,所述氧化包括使所述第三层的露出部分暴露至氮气。

15.根据权利要求1所述的方法,其中:

16.根据权利要求15所述的方法,进一步包括在所述开口处设置第一沟道层,其中,所述第一沟道层的部分设置在所述牺牲层的受到蚀刻的部分中。

17.根据权利要求15所述的方法,进一步包括使所述半导体结构键合至cmos结构,其中,所述牺牲层被设置为与所述半导体结构和所述cmos结构的键合界面相对。

18.一种制作半导体结构的方法,所述半导体结构包括牺牲层、第一层、第二层、第三层和沟道结构,所述沟道结构被设置为至少与所述第一层、所述第二层、所述第三层和所述牺牲层相交并且包括空洞和窄化部分,所述方法包括:

19.根据权利要求18所述的方法,进一步包括蚀刻掉所述第一层和所述第二层的被设置为接近所述沟道结构的窄化部分的部分。

20.根据权利要求19所述的方法,进一步包括将多晶硅设置到所述半导体结构上,以形成与所述沟道结构的多晶硅结构的接触部。

21.根据权利要求18所述的方法,其中,所述牺牲层的所述去除进一步包括使用化学机械抛光工艺。

22.根据权利要求18所述的方法,其中,所述第一层的所述去除包括使用化学机械抛光工艺。

23.一种半导体结构,包括:

24.一种nand闪速存储器装置,包括:

25.一种存储器系统,包括:

技术总结

本公开提供了制造用于NAND存储器装置的具有提高的可靠性的半导体结构的制作方法。该方法可以包括形成包括第一层、设置在第一层上的第二层和设置在第二层上的第三层的分层半导体结构。该方法还可以包括形成沟道结构,其可以包括通过该半导体结构的表面蚀刻第一层、第二层和第三层,以形成开口。可以在该开口处露出第三层的部分。该沟道结构的形成还包括氧化第三层的露出部分,从而形成扩大第三层的露出部分的氧化硅。

技术研发人员:李倩,伍术,肖亮,李磊,蒲浩

受保护的技术使用者:长江存储科技有限责任公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!