延迟锁定回路电路的制作方法

本发明大体上涉及一种延迟锁定回路电路,且更具体地说,涉及延迟锁定回路电路可避免发生延迟跳变及无法锁定事件。

背景技术:

1、在常规技术中,延迟锁定回路电路由模拟放大器检测参考时钟信号与反馈时钟信号之间的相位差。放大器始终产生由布局失配、组件不对称以及许多其它原因造成的相位检测错误。此外,由于放大器的灵敏度,相位检测操作不稳定及延迟跳变以及解锁事件经常发生。如此,延迟锁定回路电路的效能减少。

技术实现思路

1、本发明提供可高效地锁定参考时钟信号的相位的延迟锁定回路电路。

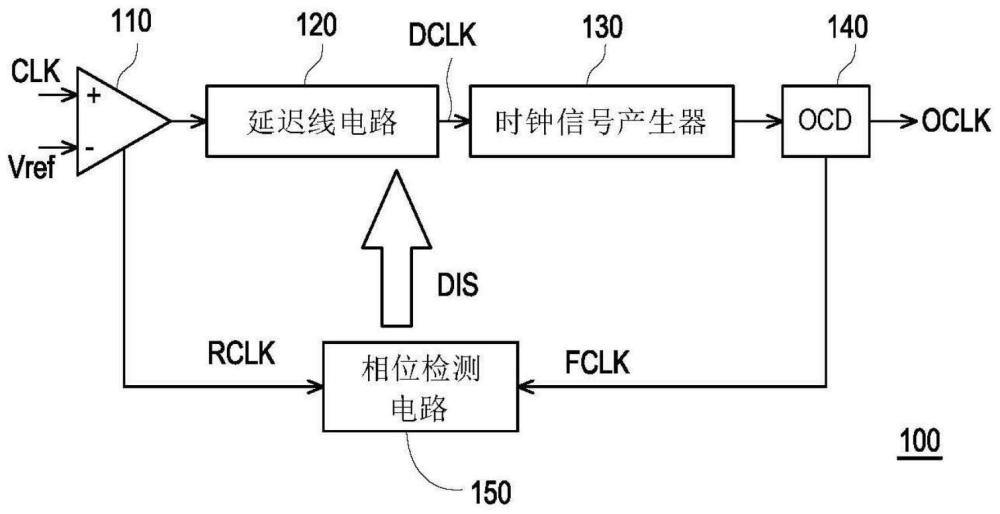

2、延迟锁定回路电路包含接收器、延迟线电路、时钟信号产生器以及相位检测电路。接收器接收时钟信号及参考电压且根据时钟信号及参考电压产生参考时钟信号。延迟线电路耦接到接收器且通过用延迟指示信号延迟参考时钟信号来产生延迟时钟信号。时钟信号产生器耦接到延迟线电路且根据延迟时钟信号产生输出时钟信号。相位检测电路耦接到接收器及时钟信号产生器,通过用由输出时钟信号产生的反馈时钟信号对参考时钟信号进行采样产生检测结果,且根据检测结果的数值产生延迟指示信号。

3、总体来说,本公开呈现的延迟锁定回路电路提供相位检测电路以用反馈时钟信号对参考时钟信号进行采样来获取检测结果。相位检测电路根据检测结果的数值进一步产生延迟指示信号且延迟指示信号可用以指示延迟锁定回路电路的锁定状态。如此,可根据延迟指示信号高效地调整延迟线电路的延迟量,可很好锁定地延迟锁定回路电路且可避免延迟跳变。

4、为了使前述内容更易理解,如下伴随附图详细地描述若干实施例。

技术特征:

1.一种延迟锁定回路电路,包括:

2.根据权利要求1所述的延迟锁定回路电路,其中所述相位检测电路包括:

3.根据权利要求2所述的延迟锁定回路电路,其中所述m个触发器中的每一者包括:

4.根据权利要求3所述的延迟锁定回路电路,其中所述m个触发器中的每一者更包括:

5.根据权利要求2所述的延迟锁定回路电路,其中当所述相位检测电路检测到所述数值等于或大于第一阈值的第一数目的连续次数的数目时,所述相位检测电路产生所述延迟指示信号以减少所述延迟线电路的延迟量。

6.根据权利要求5所述的延迟锁定回路电路,其中当所述相位检测电路检测到所述数值等于或大于第二阈值的第二数目的连续次数的数目时,所述相位检测电路产生所述延迟指示信号以增加所述延迟线电路的所述延迟量。

7.根据权利要求6所述的延迟锁定回路电路,其中所述第一阈值及所述第二阈值相同或不同。

8.根据权利要求6所述的延迟锁定回路电路,其中当所述相位检测电路检测到在第三数目与第四数目之间连续交替变化的所述数值时,所述延迟锁定回路电路处于锁定状态。

9.根据权利要求8所述的延迟锁定回路电路,其中所述相位检测电路更包括:

10.根据权利要求9所述的延迟锁定回路电路,其中所述第一逻辑电路包括:

11.根据权利要求9所述的延迟锁定回路电路,其中所述第二逻辑电路包括:

12.根据权利要求9所述的延迟锁定回路电路,其中所述移位寄存器电路的寄存器的数目大于1。

13.根据权利要求6所述的延迟锁定回路电路,其中所述相位检测电路更包括:

14.根据权利要求13所述的延迟锁定回路电路,其中所述移位寄存器电路的所述寄存器的数量大于1。

15.根据权利要求13所述的延迟锁定回路电路,其中所述相位检测电路根据所述远离锁定标志产生所述延迟指示信号。

16.根据权利要求1所述的延迟锁定回路电路,更包括:

17.根据权利要求1所述的延迟锁定回路电路,其中所述时钟信号产生器包括:

技术总结

本发明提供一种延迟锁定回路电路,包含接收器、延迟线电路、时钟信号产生器以及相位检测电路。接收器接收时钟信号及参考电压且根据时钟信号及参考电压产生参考时钟信号。延迟线电路耦接到接收器且通过用延迟指示信号延迟参考时钟信号来产生延迟时钟信号。时钟信号产生器根据延迟时钟信号产生输出时钟信号。相位检测电路通过用由输出时钟信号产生的反馈时钟信号对参考时钟信号进行采样产生检测结果,且根据检测结果的数值产生延迟指示信号。

技术研发人员:杨吴德

受保护的技术使用者:南亚科技股份有限公司

技术研发日:

技术公布日:2024/2/8

- 还没有人留言评论。精彩留言会获得点赞!