一种神经元器件及其制备方法

本发明涉及半导体器件制备,具体涉及一种神经元器件及其制备方法。

背景技术:

1、近年来,由于忆阻器件在神经形态计算方面具有极大优势而得到了人们的广泛关注。新型忆阻器件如铁电基忆阻器、相变基忆阻器件和磁阻隧穿基忆阻器等与cmos器件相比具有结构简单、功耗低和动态特性丰富等优势已得到报道,从而应用于神经形态计算。

2、基于二维材料的器件由于其可微缩性好、动态特性丰富等优点也被人们用于实现神经形态计算。然而由于二维材料本身的一些接触、缺陷等内在缺点,目前基于二维材料的神经形态器件特别是神经元器件的研究尚未得到充分的开展。

3、因此,开发一种基于二维材料的神经元器件成为新的研究课题。

技术实现思路

1、本发明的目的是克服现有技术的缺点,提供一种神经元器件,该神经元器件基于二维材料沟道层实现神经形态计算,并通过在源漏两端与沟道层的接触区插入功函数层,使接触界面形成非对称的肖特基接触,并结合栅介质层引入的缺陷电荷俘获和释放机制,实现了阻变特性并进一步实现了单器件的lif(leaky-integral-fire,泄漏-积分-激发)神经元器件,即单器件神经元。

2、本发明的另一目的是提供上述神经元器件的制备方法。

3、为了实现以上目的,本发明提供如下技术方案。

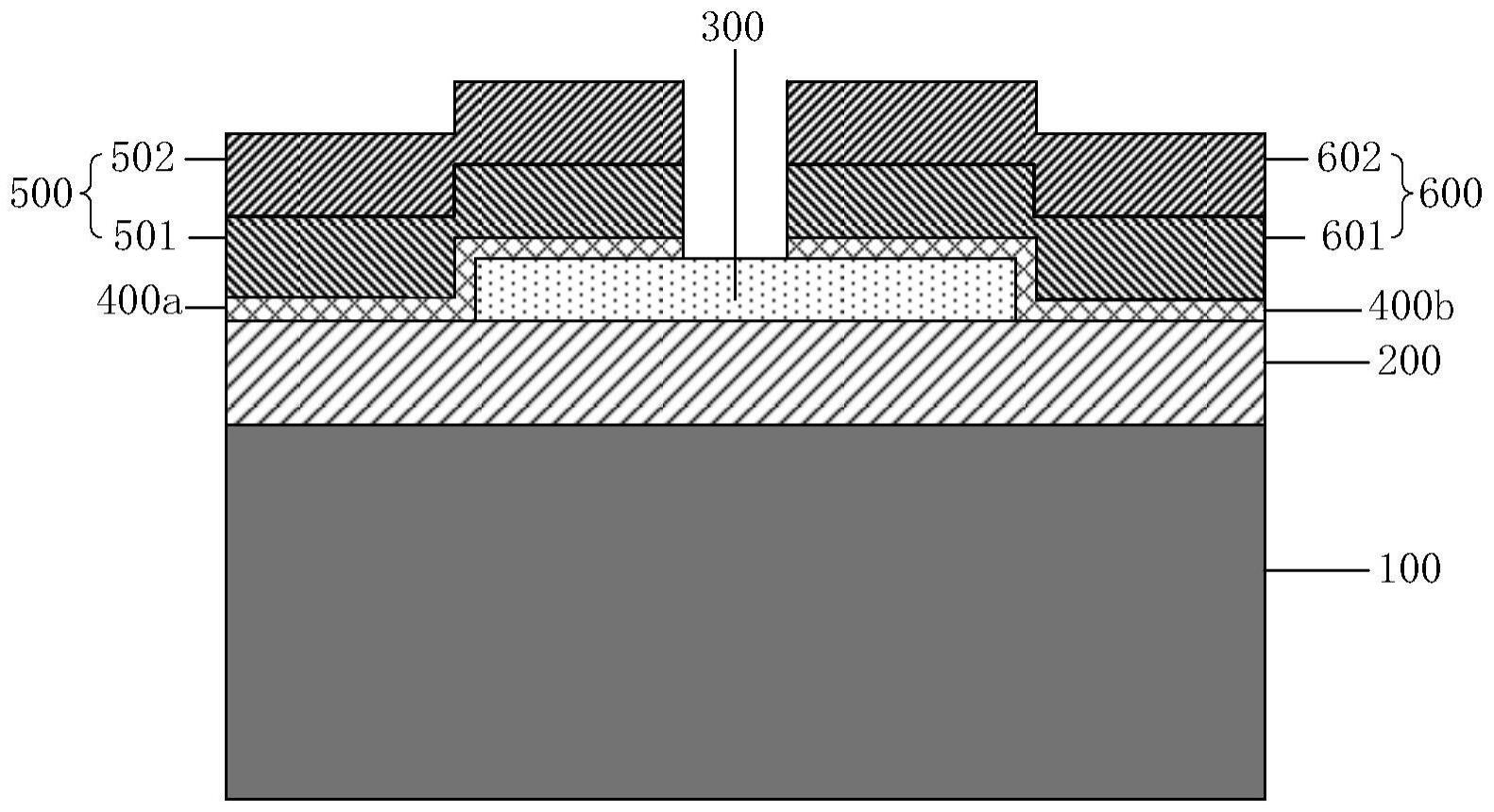

4、一种神经元器件,包括:

5、衬底;

6、栅介质层,所述栅介质层设置在所述衬底上表面;

7、沟道层,所述沟道层覆盖所述栅介质层的部分上表面,并且所述沟道层的材质为二维材料;

8、源极和漏极,所述源极和所述漏极均设置在所述沟道层上方且彼此不接触;

9、第一功函数层,所述第一功函数层设置在所述沟道层和所述源极之间;以及

10、第二功函数层,所述第二功函数层设置在所述沟道层和所述漏极之间,并且所述第二功函数层与所述第一功函数层彼此不接触。

11、一种神经元器件的制备方法,包括以下步骤:

12、提供衬底;

13、在所述衬底上形成栅介质层;

14、在所述栅介质层上形成沟道层,使其覆盖所述栅介质层的部分上表面,并且所述沟道层的材质为二维材料;

15、形成初始功函数层,使其覆盖所述沟道层的表面;

16、光刻所述初始功函数层,形成开口,使所述沟道层的部分上表面裸露,得到第一功函数层和第二功函数层;以及

17、在所述第一功函数层表面形成源极,在所述第二功函数层表面形成漏极。

18、相比现有技术,本发明的有益效果:

19、1、本发明提供了一种神经元器件,该神经元器件基于二维材料沟道层实现神经形态计算,并通过在源/漏两端与沟道层的接触区插入功函数层,使接触界面形成非对称的肖特基接触,并结合栅介质层引入的缺陷电荷俘获和释放机制,实现了阻变特性并进一步实现了单器件的lif(leaky-integral-fire,泄漏-积分-激发)神经元器件。并且本发明的神经元器件因使用二维材料而具有可微缩性好、动态特性丰富等优点。

20、本发明通过功函数层的引入和栅介质层的生长,提供了一种实现神经元器件的新途径,为进一步实现低功耗神经网络计算提供了思路。

21、2、本发明的基于二维材料的神经元器件与硅基工艺兼容,便于集成。

技术特征:

1.一种神经元器件,其特征在于,包括:

2.根据权利要求1所述的神经元器件,其特征在于,所述第一功函数层和所述第二功函数层的材质均为tio2。

3.根据权利要求1或2所述的神经元器件,其特征在于,所述源极设置在所述栅介质层和所述沟道层的上方,并且所述第一功函数层设置在所述沟道层和所述源极之间以及所述栅介质层和所述源极之间。

4.根据权利要求1或2所述的神经元器件,其特征在于,所述漏极设置在所述栅介质层和所述沟道层的上方,并且所述第二功函数层设置在所述沟道层和所述漏极之间以及所述栅介质层和所述漏极之间。

5.根据权利要求1或2所述的神经元器件,其特征在于,

6.根据权利要求1或2所述的神经元器件,其特征在于,

7.一种神经元器件的制备方法,其特征在于,包括以下步骤:

8.根据权利要求7所述的制备方法,其特征在于,在真空环境下,利用电子束蒸发形成所述初始功函数层,所述真空环境的真空度为1x 10-9mbar以上。

9.根据权利要求7或8所述的制备方法,其特征在于,形成所述沟道层包括:

10.根据权利要求7或8所述的制备方法,其特征在于,所述源极和所述漏极同步形成,形成方法包括:

技术总结

本发明涉及一种神经元器件,该神经元器件基于二维材料沟道层实现神经形态计算,并通过在源/漏两端与沟道层的接触区插入功函数层,使接触界面形成非对称的肖特基接触,并结合栅介质层引入的缺陷俘获和释放机制,实现了阻变特性并进一步实现了基于单器件的LIF神经元器件,即单器件神经元。

技术研发人员:吴振华,霍嘉丽,张兆浩,张亚东,殷华湘

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!