一种用于PCB的镀金方法与流程

本发明涉及pcb制备领域,尤其涉及一种用于pcb的镀金方法。

背景技术:

1、电路板行业里对厚金线圈板(金厚超1um的环形面)通常采用的是一根导线镀金,但是这种镀金方案容易导致不同位置的金厚极差较大。在镀金后通常会面临两种问题:(1)、确保整面金厚达标,会导致靠近引线位置的金厚超标,浪费金盐;(2)、出现局部位置金厚不合格。

2、同时在镀金工艺之前芯板已经经过了多个工序,在这些工序中难免存在磕碰,使得芯板中待镀金区域出现划伤,这些划伤在镀金之前的铜芯板中不明显,但是镀金之后光泽度增加,导致铜面划伤比较明显。

技术实现思路

1、本发明旨在至少在一定程度上解决相关技术中的问题之一。为此,本发明的目的在于提供一种用于pcb的镀金方法,能够有效提高镀金均匀性。

2、为了实现上述目的,本申请采用如下技术方案:一种用于pcb的镀金方法,包括:确定镀金区域,在每一个镀金区域的边缘设置m个副引线,沿着m个副引线分别从m个方向对镀金区域进行镀金;m为大于1的整数。

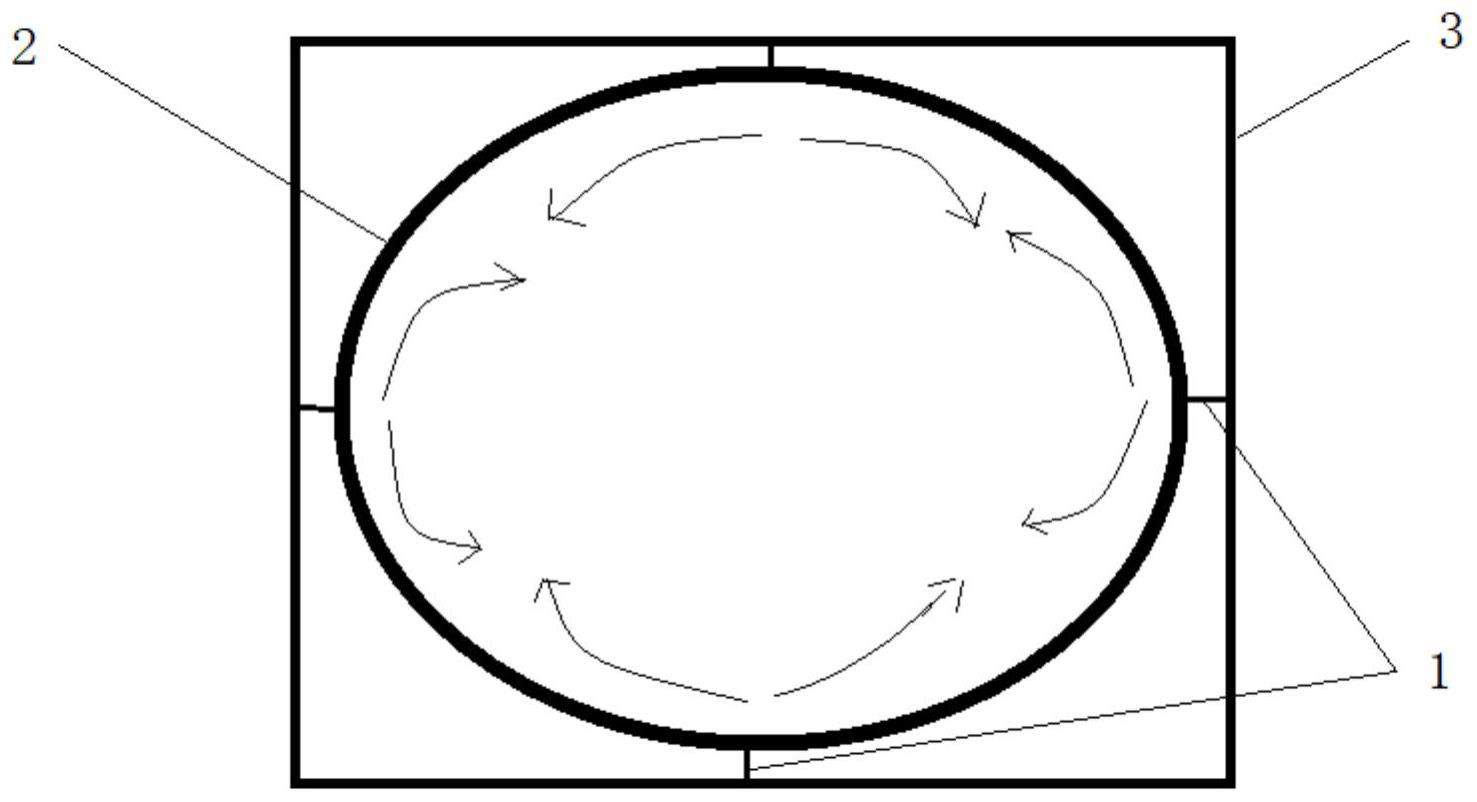

3、进一步的,所述镀金区域为环形,m个副引线均匀且间隙地设置在环形的镀金区域的边缘外侧。

4、进一步的,所述副引线为四个,四个副引线沿着环形镀金区域的圆心对称分布。

5、进一步的,所述镀金区域为多边形,m个副引线均匀且间隙地设置在多边形镀金区域的边缘外侧。

6、进一步的,m个副引线同时连接至主引线。

7、进一步的,所述镀金区域中镀层的厚度大于1微米。

8、进一步的,所述镀金区域为铜芯板。

9、进一步的,镀金之前,对待镀金区域的铜芯板进行减薄。

10、进一步的,当镀金区域中包含有pth孔时,采用干膜掩盖pth孔,再对镀金区域进行减薄。

11、本申请实施例提供的上述技术方案与现有技术相比具有如下优点:本申请确定镀金区域之后,在镀金区域的边缘处设置多个副引线,使得镀金工艺沿着多个副引线同步进行,确保镀金区域中各个位置处的电位电流密度尽量相等,不仅节省了镀金时间,还能够提高镀金均匀性;本申请方法中镀金区域的镀层厚度越厚,越能提升镀金区域的镀层厚度的均匀性。

技术特征:

1.一种用于pcb的镀金方法,其特征在于,包括:确定镀金区域,在每一个镀金区域的边缘设置m个副引线,沿着m个副引线分别从m个方向对镀金区域进行镀金;m为大于1的整数。

2.根据权利要求1所述的一种用于pcb的镀金方法,其特征在于,所述镀金区域为环形,m个副引线均匀且间隙地设置在环形的镀金区域的边缘外侧。

3.根据权利要求2所述的一种用于pcb的镀金方法,其特征在于,所述副引线为四个,四个副引线沿着环形镀金区域的圆心对称分布。

4.根据权利要求1所述的一种用于pcb的镀金方法,其特征在于,所述镀金区域为多边形,m个副引线均匀且间隙地设置在多边形镀金区域的边缘外侧。

5.根据权利要求1所述的一种用于pcb的镀金方法,其特征在于,m个副引线同时连接至主引线。

6.根据权利要求1所述的一种用于pcb的镀金方法,其特征在于,所述镀金区域中镀层的厚度大于1微米。

7.根据权利要求1所述的一种用于pcb的镀金方法,其特征在于,所述镀金区域为铜芯板。

8.根据权利要求7所述的一种用于pcb的镀金方法,其特征在于,镀金之前,对待镀金区域的铜芯板进行减薄。

9.根据权利要求8所述的一种用于pcb的镀金方法,其特征在于,当镀金区域中包含有pth孔时,采用干膜掩盖pth孔,再对镀金区域进行减薄。

技术总结

本发明公开了一种用于PCB的镀金方法,包括:确定镀金区域,在每一个镀金区域的边缘设置M个副引线,沿着M个副引线分别从M个方向对镀金区域进行镀金;M为大于1的整数。本申请确定镀金区域之后,在镀金区域的边缘处设置多个副引线,使得镀金工艺沿着多个副引线同步进行,确保镀金区域中各个位置处的电位电流密度尽量相等,不仅节省了镀金时间,还能够提高镀金均匀性;本申请方法中镀金区域的镀层厚度越厚,越能提升镀金区域的镀层厚度的均匀性。

技术研发人员:陈小娇,向参军,陈梓阳,邱光民

受保护的技术使用者:广州广合科技股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!