闪存器件及其制造方法与流程

本发明涉及集成电路制造,尤其涉及一种闪存器件及其制造方法。

背景技术:

1、闪存器件作为一种非易失性存储器,具有便捷、存储密度高、可靠性强等特点,应用广泛。现有的闪存器件的结构通常包括分栅结构、叠栅结构或其组合,其中,分栅式闪存器件具有编程效率高的特点。

2、随着集成电路制造技术水平的不断进步,闪存器件的尺寸也不断缩小。参阅图1和图2,在刻蚀开口10暴露的控制栅层20过程中可能会出现侧掏现象,导致控制栅层20的靠近开口10一侧的顶角处出现突起a;参阅图3,后续的湿法清洗等工艺会回刻控制栅层20上方的第一侧墙30,从而导致突起a暴露。然而,参阅图4,随着闪存器件尺寸的缩小,闪存器件中各个膜层的厚度减薄,相关的工艺窗口随之减小。由于第一侧墙30和控制栅层20的交界处存在突起a,因此,后续形成于第一侧墙30表面和控制栅21的侧壁上的第二侧墙31容易出现厚度不均匀的情况,严重时第二侧墙31的靠近突起a的部分会发生断裂,并导致控制栅21和字线40之间的介质层(即第一侧墙30、第二侧墙31和第三侧墙33)被击穿。

3、鉴于此,需要一种方法减少或避免第二侧墙出现厚度不均匀或断开的情况,从而避免字线与控制栅之间的介质层被击穿。

技术实现思路

1、本发明的目的在于提供一种闪存器件及其制造方法,减少或避免第二侧墙出现厚度不均匀或断开的情况,从而避免字线与控制栅之间的介质层被击穿。

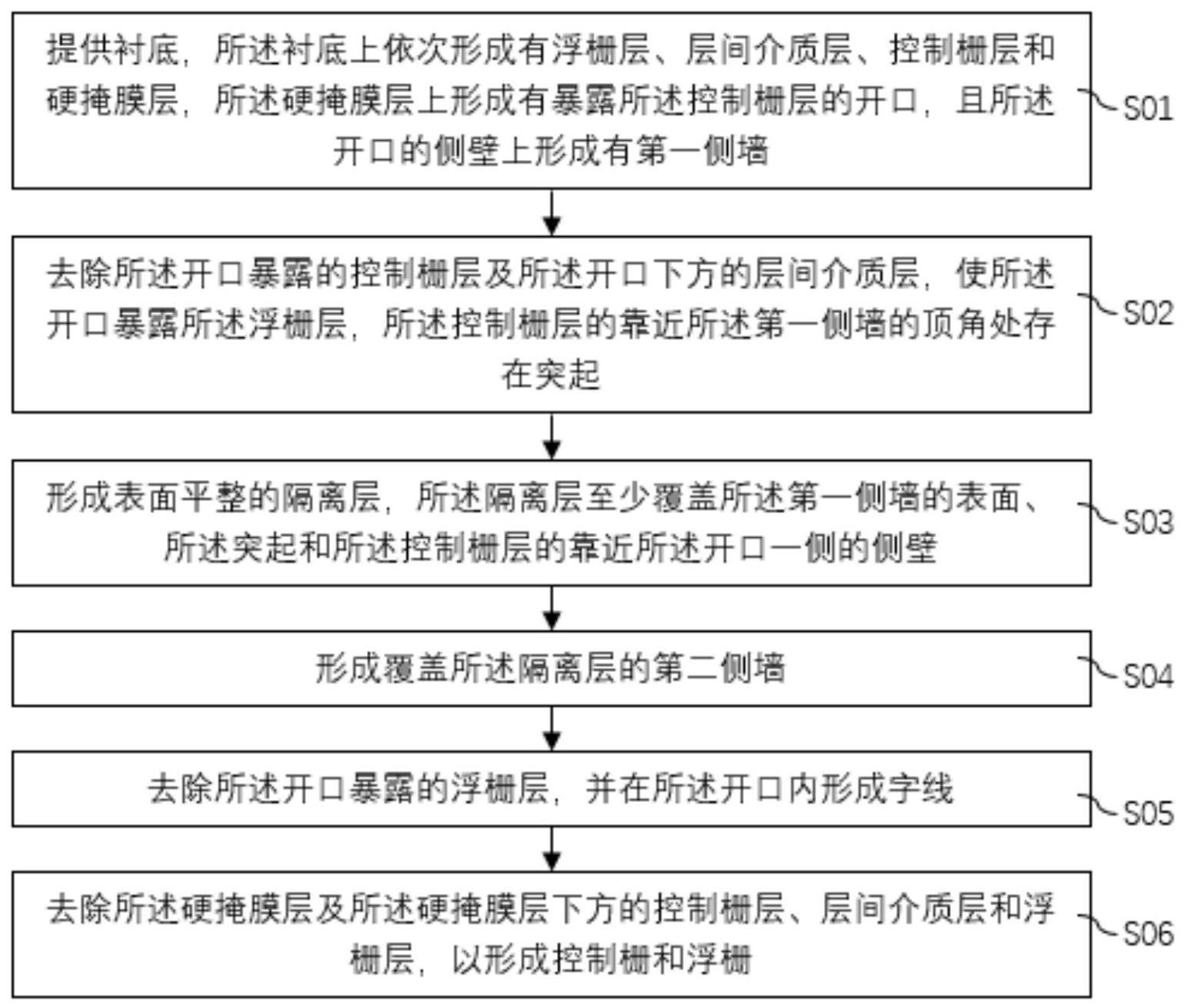

2、为了达到上述目的,本发明提供了一种闪存器件的制造方法,包括:

3、提供衬底,所述衬底上依次形成有浮栅层、层间介质层、控制栅层和硬掩膜层,所述硬掩膜层上形成有暴露所述控制栅层的开口,且所述开口的侧壁上形成有第一侧墙;

4、去除所述开口暴露的控制栅层及所述开口下方的层间介质层,使所述开口暴露所述浮栅层,所述控制栅层的靠近所述第一侧墙的顶角处存在突起;

5、形成表面平整的隔离层,所述隔离层至少覆盖所述第一侧墙的表面、所述突起和所述控制栅层的靠近所述开口一侧的侧壁;

6、形成覆盖所述隔离层的第二侧墙;

7、去除所述开口暴露的浮栅层,并在所述开口内形成字线;以及,

8、去除所述硬掩模层及所述硬掩模层下方的控制栅层、层间介质层和浮栅层,以形成控制栅和浮栅。

9、可选的,形成表面平整的所述隔离层的过程包括:

10、在所述开口的侧壁及底部沉积隔离层,所述隔离层延伸覆盖所述开口两侧的硬掩膜层;

11、图形化所述隔离层,使所述隔离层至少覆盖所述第一侧墙的表面、所述突起和所述控制栅层的靠近所述开口一侧的侧壁,并使所述隔离层的表面平整。

12、可选的,采用各向异性的干法刻蚀工艺图形化所述隔离层。

13、可选的,在图形化所述隔离层之后,还包括:

14、进行灰化工艺及湿法清洗工艺,以去除所述图形化过程中产生的聚合物。

15、可选的,所述隔离层的厚度大于所述突起突出所述控制栅的侧壁的宽度。

16、可选的,所述隔离层的材料与所述第一侧墙或所述第二侧墙的材料相同。

17、可选的,在去除所述开口暴露的浮栅层之后,形成所述字线之前,还包括:

18、在所述开口的侧壁和底壁形成第三侧墙。

19、可选的,所述衬底和所述浮栅层之间还形成有栅氧化层。

20、可选的,所述闪存器件的制造方法用于制造分栅式闪存器件。

21、相应的,本发明还提供一种闪存器件,包括:

22、衬底;

23、字线,设置于所述衬底上;

24、浮栅,设置于所述字线的两侧;

25、控制栅,设置于所述浮栅上,所述控制栅的靠近所述字线一侧的顶角上设置有突起;

26、第一侧墙,设置于所述控制栅上;

27、隔离层,设置于所述第一侧墙的表面和所述控制栅的靠近所述字线一侧的侧壁,所述隔离层覆盖所述突起;

28、第二侧墙,设置于所述隔离层和所述字线之间。

29、综上所述,本发明提供一种闪存器件及其制造方法,在衬底上依次形成浮栅层、层间介质层、控制栅层和具有开口的硬掩膜层,并在开口的侧壁上形成第一侧墙;去除开口暴露的控制栅层及其下方的层间介质层,所述控制栅层的靠近所述第一侧墙的顶角处存在突起;形成表面平整的隔离层,所述隔离层至少覆盖所述第一侧墙的表面、所述突起和所述控制栅层的靠近所述开口一侧的侧壁;形成覆盖所述隔离层的第二侧墙;去除所述开口暴露的浮栅层,并在所述开口内形成字线;以及,去除所述硬掩模层及所述硬掩模层下方的控制栅层、层间介质层和浮栅层,以形成控制栅和浮栅。本发明通过在突起上形成表面平整的隔离层,减少或避免第二侧墙出现厚度不均匀或断开的情况,拓宽了后续工艺的工艺窗口,改善了字线与控制栅之间的击穿电压。

技术特征:

1.一种闪存器件的制造方法,其特征在于,包括:

2.如权利要求1所述的闪存器件的制造方法,其特征在于,形成表面平整的所述隔离层的过程包括:

3.如权利要求2所述的闪存器件的制造方法,其特征在于,采用各向异性的干法刻蚀工艺图形化所述隔离层。

4.如权利要求3所述的闪存器件的制造方法,其特征在于,在图形化所述隔离层之后,还包括:

5.如权利要求1或2所述的闪存器件的制造方法,其特征在于,所述隔离层的厚度大于所述突起突出所述控制栅的侧壁的宽度。

6.如权利要求1所述的闪存器件的制造方法,其特征在于,所述隔离层的材料与所述第一侧墙或所述第二侧墙的材料相同。

7.如权利要求1所述的闪存器件的制造方法,其特征在于,在去除所述开口暴露的浮栅层之后,形成所述字线之前,还包括:

8.如权利要求1所述的闪存器件的制造方法,其特征在于,所述衬底和所述浮栅层之间还形成有栅氧化层。

9.如权利要求1所述的闪存器件的制造方法,其特征在于,所述闪存器件的制造方法用于制造分栅式闪存器件。

10.一种闪存器件,其特征在于,包括:

技术总结

本发明提供了一种闪存器件及其制造方法,在衬底上依次形成浮栅层、层间介质层、控制栅层和具有开口的硬掩膜层,并在开口的侧壁上形成第一侧墙;去除开口暴露的控制栅层及其下方的层间介质层,控制栅层的靠近第一侧墙的顶角处存在突起;形成表面平整的隔离层,所述隔离层至少覆盖第一侧墙表面、突起和控制栅层的靠近开口一侧的侧壁;形成覆盖隔离层的第二侧墙;去除开口暴露的浮栅层,并在开口内形成字线;去除硬掩模层及其下方的控制栅层、层间介质层和浮栅层,以形成控制栅和浮栅。本发明通过在突起上形成表面平整的隔离层,减少或避免第二侧墙出现厚度不均匀或断开的情况,拓宽了后续工艺的工艺窗口,改善了字线与控制栅之间的击穿电压。

技术研发人员:朱景润,沈思杰,刘宪周

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!