一种3D存储器及其制备方法、电子设备与流程

本公开实施例涉及但不限于半导体技术,尤指一种3d存储器及其制备方法、电子设备。

背景技术:

1、随着动态随机存取存储器(dynamic random acess memory,dram)技术步入10纳米(nm)节点,平面的1t1c结构已经趋于极限,为了获取更高的存储电容,更低漏电,更高集成度,dram存储器逐渐向三维(3d)立体结构发展,然而随着3d立体结构的发展会遇到各种各样的问题,随着堆叠层数增加,阵列越大越紧密,不同层间的寄生金属氧化物半导体(metal oxide semiconductor,mos)电容的存在对电容存储电荷的保持力以及器件整体的稳定性产生很大影响。所以在3d dram器件的研发中,在攻克复杂工艺结构的同时,需要充分考虑一些寄生电容的优化甚至消除。

技术实现思路

1、以下是对本文详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、本公开实施例提供了一种3d存储器及其制备方法、电子设备,可以减少寄生电容,提升器件性能。

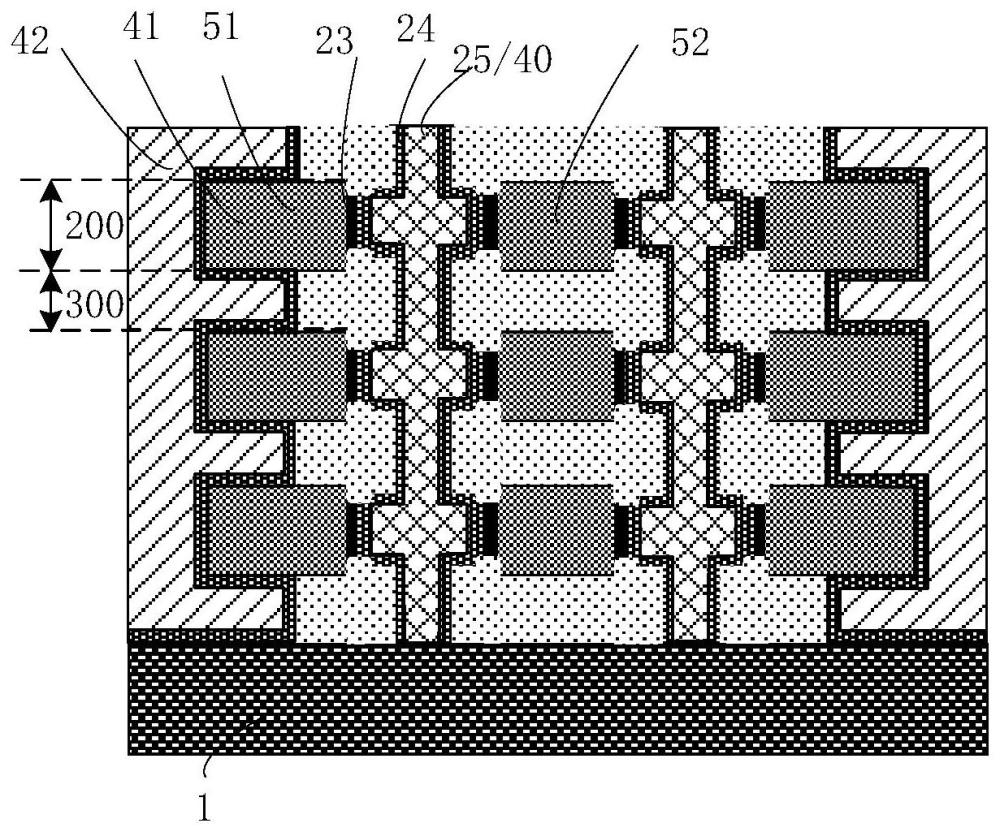

3、本公开实施例提供了一种3d存储器的制备方法,所述3d存储器包括多层沿垂直于衬底的方向堆叠的存储单元,字线,所述存储单元包括:晶体管和电容,所述晶体管包括第一电极、第二电极、沿垂直于所述衬底的方向延伸的栅电极、环绕所述栅电极且与所述栅电极相绝缘的半导体层,所述电容包括第一极板和第二极板,所述3d存储器的制备方法包括:

4、提供衬底,在所述衬底上依次交替沉积牺牲层薄膜和导电薄膜,构图形成堆叠结构,所述堆叠结构包括交替设置的牺牲层和导电层的堆叠,所述导电层包括预设电极图形;

5、形成在垂直于所述衬底的方向上贯穿所述堆叠结构的过孔,所述过孔的侧壁露出每个所述导电层,且所述过孔使得所述预设电极图形形成至少一对彼此分离的第一电极和第二电极;所述过孔包括多个分别位于所述牺牲层的第一子孔和多个分别位于所述导电层的第二子孔,在平行于所述衬底的平面上,所述第一子孔的正投影落入所述第二子孔的正投影内;

6、在所述过孔的侧壁依次沉积半导体薄膜和栅绝缘薄膜,形成多层所述晶体管的半导体层和栅绝缘层,所述半导体层与所述第一电极和所述第二电极接触,同一个晶体管中所述第一电极和所述第二电极之间的沟道为水平沟道;在所述过孔内沉积填充所述过孔的栅电极薄膜形成多层所述晶体管的栅电极,不同层的所述晶体管的所述栅电极为所述字线的一部分;

7、刻蚀去除所述牺牲层以暴露位于所述第一子孔内的所述半导体层,刻蚀去除位于第一子孔内的所述半导体层。

8、在一示例性实施例中,所述构图形成堆叠结构包括:

9、使用干法刻蚀所述牺牲层薄膜和导电薄膜,去除位于预设隔离区域的牺牲层薄膜和导电薄膜,以形成所述交替设置的牺牲层和导电层的堆叠;

10、在所述预设隔离区域沉积第一绝缘薄膜形成第一绝缘层,所述第一绝缘薄膜与所述牺牲层薄膜的材料不同。

11、在一示例性实施例中,构图形成堆叠结构之后,形成在垂直于所述衬底的方向上贯穿所述堆叠结构的过孔前,还包括:

12、刻蚀去除位于预设电容区域的第一绝缘层和牺牲层,以暴露各层所述晶体管的所述第一电极的一端;

13、在所述预设电容区域依次沉积第二绝缘薄膜和导体材料以形成第二绝缘层和所述电容的第二极板,所述第二绝缘层覆盖所述第一电极暴露的区域,所述第二极板通过所述第二绝缘层与所述第一电极隔离。

14、在一示例性实施例中,所述形成在垂直于所述衬底的方向上贯穿所述堆叠结构的过孔包括:

15、刻蚀所述堆叠结构形成在垂直于所述衬底的方向上贯穿所述堆叠结构的初始过孔,所述初始过孔包括所述第一子孔和位于所述导电层的第二初始子孔,朝远离所述初始过孔的方向刻蚀所述导电层以扩大所述第二初始子孔形成所述第二子孔。

16、在一示例性实施例中,所述牺牲层薄膜包括多晶硅。

17、在一示例性实施例中,所述第一绝缘薄膜包括氮化硅。

18、在一示例性实施例中,刻蚀去除位于第一子孔内的所述半导体层后,还包括:刻蚀去除位于所述第一子孔内的至少部分所述栅绝缘层。

19、在一示例性实施例中,所述导电层还包括位线,所述位线连接所述第二电极。

20、本公开实施例提供一种3d存储器,所述3d存储器使用上述任一实施例所述的3d存储器的制备方法制备。

21、本公开实施例提供一种电子设备,包括上述3d存储器。

22、本公开实施例包括一种3d存储器及其制备方法、电子设备,所述3d存储器包括多层沿垂直于衬底的方向堆叠的存储单元,字线,所述存储单元包括:晶体管和电容,所述晶体管包括第一电极、第二电极、沿垂直于所述衬底的方向延伸的栅电极、环绕所述栅电极且与所述栅电极相绝缘的半导体层,所述电容包括第一极板和第二极板,所述3d存储器的制备方法包括:提供衬底,在所述衬底上依次交替沉积牺牲层薄膜和导电薄膜,构图形成堆叠结构,所述堆叠结构包括交替设置的牺牲层和导电层的堆叠,所述导电层包括预设电极图形;形成在垂直于所述衬底的方向上贯穿所述堆叠结构的过孔,所述过孔的侧壁露出每个所述导电层,且所述过孔使得所述预设电极图形形成至少一对彼此分离的第一电极和第二电极;所述过孔包括多个分别位于所述牺牲层的第一子孔和多个分别位于所述导电层的第二子孔,在平行于所述衬底的平面上,所述第一子孔的正投影落入所述第二子孔的正投影内;在所述过孔的侧壁依次沉积半导体薄膜和栅绝缘薄膜,形成多层所述晶体管的半导体层和栅绝缘层,所述半导体层与所述第一电极和所述第二电极接触,同一个晶体管中所述第一电极和所述第二电极之间的沟道为水平沟道;在所述过孔内沉积填充所述过孔的栅电极薄膜形成多层所述晶体管的栅电极,不同层的所述晶体管的所述栅电极为所述字线的一部分;刻蚀去除所述牺牲层以暴露位于所述第一子孔内的所述半导体层,刻蚀去除位于第一子孔内的所述半导体层。本实施例提供的方案,通过在导电层间设置牺牲层,通过刻蚀牺牲层暴露位于导电层间的半导体层,以便刻蚀位于导电层间的半导体层,从而减少不同层的晶体管间的寄生电容,提高器件性能。

23、本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和优点可通过在说明书以及附图中所特别指出的结构来实现和获得。

24、在阅读并理解了附图和详细描述后,可以明白其他方面。

技术特征:

1.一种3d存储器的制备方法,其特征在于,所述3d存储器包括多层沿垂直于衬底的方向堆叠的存储单元,字线,所述存储单元包括:晶体管和电容,所述晶体管包括第一电极、第二电极、沿垂直于所述衬底的方向延伸的栅电极、环绕所述栅电极且与所述栅电极相绝缘的半导体层,所述电容包括第一极板和第二极板,所述3d存储器的制备方法包括:

2.根据权利要求1所述的3d存储器的制备方法,其特征在于,所述构图形成堆叠结构包括:

3.根据权利要求2所述的3d存储器的制备方法,其特征在于,构图形成堆叠结构之后,形成在垂直于所述衬底的方向上贯穿所述堆叠结构的过孔前,还包括:

4.根据权利要求1所述的3d存储器的制备方法,其特征在于,所述形成在垂直于所述衬底的方向上贯穿所述堆叠结构的过孔包括:

5.根据权利要求1所述的3d存储器的制备方法,其特征在于,所述牺牲层薄膜包括多晶硅。

6.根据权利要求2所述的3d存储器的制备方法,其特征在于,所述第一绝缘薄膜包括氮化硅。

7.根据权利要求1所述的3d存储器的制备方法,其特征在于,刻蚀去除位于第一子孔内的所述半导体层后,还包括:刻蚀去除位于所述第一子孔内的至少部分所述栅绝缘层。

8.根据权利要求2所述的3d存储器的制备方法,其特征在于,所述导电层还包括位线,所述位线连接所述第二电极。

9.一种3d存储器,其特征在于,所述3d存储器使用如权利要求1至8任一所述的3d存储器的制备方法制备。

10.一种电子设备,其特征在于,包括如权利要求9所述的3d存储器。

技术总结

一种3D存储器及其制备方法,电子设备,所述3D存储器的制备方法包括:形成包括交替设置的牺牲层和导电层的堆叠的堆叠结构,形成贯穿所述堆叠结构的过孔,所述过孔包括多个分别位于所述牺牲层的第一子孔和多个分别位于所述导电层的第二子孔,在平行于所述衬底的平面上,所述第一子孔的正投影落入所述第二子孔的正投影内;在所述过孔内形成半导体层、栅绝缘层和栅电极,不同层的所述晶体管的所述栅电极为所述字线的一部分;刻蚀去除所述牺牲层以暴露位于所述第一子孔内的所述半导体层,刻蚀去除位于第一子孔内的所述半导体层。本实施例提供的方案,通过在层间设置牺牲层,实现对层间的半导体层的刻蚀,减少寄生电容,提升器件性能。

技术研发人员:桂文华,王祥升,王桂磊,戴瑾,艾学正,毛淑娟

受保护的技术使用者:北京超弦存储器研究院

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!