振荡器以及时钟产生方法与流程

本发明是有关于时钟的产生,尤指一种使用斩波器来抑制电流源的闪烁噪声(flicker noise)的振荡器与相关时钟产生方法。

背景技术:

1、低成本与单芯片系统对于芯片上(on-chip)振荡器有很高的需求,举例来说,针对低功耗操作,弛缓振荡器(relaxation oscillator)经常被采用,弛缓振荡器相较于石英振荡器是更好的选择,主要原因是前者并不需要任何外部元件且可以采用互补金属氧化半导体(complementary metal oxide semiconductor,cmos)技术来低成本地实现,然而,弛缓振荡器容易遭受元件不匹配、闪烁噪声等等的影响,因此,需要一种创新的低功耗高准度振荡器设计。

技术实现思路

1、因此,本发明的目的之一在于提出一种使用斩波器来抑制电流源的闪烁噪声的振荡器与相关时钟产生方法。

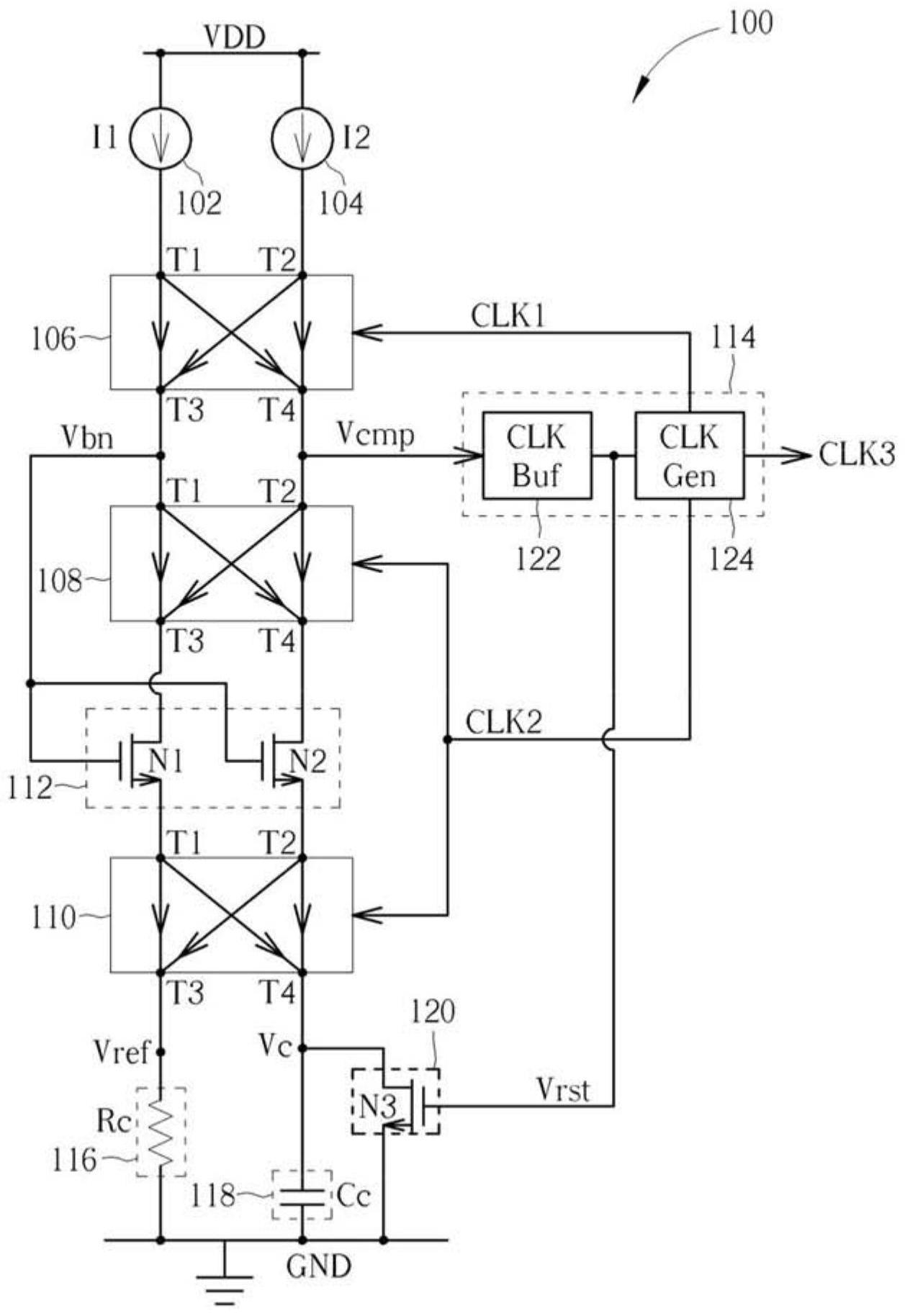

2、在本发明的一个实施例中,揭示一种振荡器。该振荡器包含一第一电流源、一第二电流源、一第一斩波电路、一电阻性元件、一电容性元件以及一处理电路。该第一电流源用以提供一第一电流。该第二电流源用以提供一第二电流。该第一斩波电路包含一第一连接端、一第二连接端、一第三连接端以及一第四连接端。该第一连接端耦接至该第一电流源,用以接收该第一电流。该第二连接端耦接至该第二电流源,以接收该第二电流。该第三连接端耦接至该电阻性元件。该第四连接端耦接至该电容性元件。该处理电路用以对应横跨该电阻性元件的第一电压以及横跨该电容性元件的第二电压,以产生一输出时钟。该第一斩波电路是用以将该第一连接端与该第二连接端分别且交替地耦接至该第三连接端与该第四连接端。该电阻性元件与该电容性元件用以分别且交替地接收该第一电流与该第二电流。

3、在本发明的另一个实施例中,揭示一种时钟产生方法。该时钟产生方法包含:通过一第一电流源来提供一第一电流;通过一第二电流源来提供一第二电流;将一第一斩波电路的第一连接端耦接至该第一电流源,以接收该第一电流;将该第一斩波电路的第二连接端耦接至该第二电流源,以接收该第二电流;将该第一斩波电路的第三连接端耦接至一电阻性元件;将该第一斩波电路的第四连接端耦接至一电容性元件;对应横跨该电阻性元件的第一电压以及横跨该电容性元件的第二电压来产生一输出时钟;以及控制该第一斩波电路来将该第一连接端与该第二连接端分别且交替地耦接至该第三连接端与该第四连接端,其中该电阻性元件与该电容性元件分别且交替地接收该第一电流与该第二电流。

4、传统的弛缓振荡器容易遭受元件不匹配、闪烁噪声等等的影响,为了解决闪烁噪声与元件不匹配的问题,本发明提出增加一或多个斩波电路至振荡器中。

技术特征:

1.一种振荡器,包含:

2.如权利要求1所述的振荡器,其中该第一斩波电路用以减少该第一电流源与该第二电流源的闪烁噪声所造成的频率漂移。

3.如权利要求1所述的振荡器,还包含:

4.如权利要求3所述的振荡器,其中该第一斩波电路是依据具有第一时钟频率的第一斩波时钟来运作,该第二斩波电路与该第三斩波电路两者均是依据具有第二时钟频率的第二斩波时钟来运作,且该第二时钟频率不同于该第一时钟频率。

5.如权利要求4所述的振荡器,其中该第一时钟频率与该第二时钟频率中的一者为该第一时钟频率与该第二时钟频率中的另一者的整数倍。

6.如权利要求3所述的振荡器,其中该第一斩波电路是依据第一斩波时钟来运作,该第二斩波电路与该第三斩波电路两者均是依据第二斩波时钟来运作,以及该处理电路包含:

7.如权利要求1所述的振荡器,还包含:

8.如权利要求7所述的振荡器,其中该第一斩波电路是依据具有第一时钟频率的第一斩波时钟来运作,该第二斩波电路与该第三斩波电路两者均是依据具有第二时钟频率的第二斩波时钟来运作,且该第二时钟频率不同于该第一时钟频率。

9.如权利要求8所述的振荡器,其中该第一时钟频率与该第二时钟频率中的一者为该第一时钟频率与该第二时钟频率中的另一者的整数倍。

10.如权利要求7所述的振荡器,其中该第一斩波电路是依据第一斩波时钟来运作,该第二斩波电路与该第三斩波电路两者均是依据第二斩波时钟来运作,以及该处理电路包含:

11.一种时钟产生方法,包含:

12.如权利要求11所述的时钟产生方法,其中该第一电流源与该第二电流源的闪烁噪声所造成的频率漂移是通过控制该第一斩波电路来将该第一连接端与该第二连接端分别且交替地耦接至该第三连接端与该第四连接端而被减少。

13.如权利要求11所述的时钟产生方法,还包含:

14.如权利要求13所述的时钟产生方法,其中该第一斩波电路是依据具有第一时钟频率的第一斩波时钟来运作,该第二斩波电路与该第三斩波电路两者均是依据具有第二时钟频率的第二斩波时钟来运作,且该第二时钟频率不同于该第一时钟频率。

15.如权利要求14所述的时钟产生方法,其中该第一时钟频率与该第二时钟频率中的一者为该第一时钟频率与该第二时钟频率中的另一者的整数倍。

16.如权利要求13所述的时钟产生方法,其中该第一斩波电路是依据第一斩波时钟来运作,该第二斩波电路与该第三斩波电路两者均是依据第二斩波时钟来运作,以及对应横跨该电阻性元件的该第一电压以及横跨该电容性元件的该第二电压来产生该输出时钟的步骤包含:

17.如权利要求11所述的时钟产生方法,还包含:

18.如权利要求17所述的时钟产生方法,其中该第一斩波电路是依据具有第一时钟频率的第一斩波时钟来运作,该第二斩波电路与该第三斩波电路两者均是依据具有第二时钟频率的第二斩波时钟来运作,且该第二时钟频率不同于该第一时钟频率。

19.如权利要求18所述的时钟产生方法,其中该第一时钟频率与该第二时钟频率中的一者为该第一时钟频率与该第二时钟频率中的另一者的整数倍。

20.如权利要求17所述的时钟产生方法,其中该第一斩波电路是依据第一斩波时钟来运作,该第二斩波电路与该第三斩波电路两者均是依据第二斩波时钟来运作,以及对应横跨该电阻性元件的该第一电压以及横跨该电容性元件的该第二电压来产生该输出时钟的步骤包含:

技术总结

本发明揭示一种振荡器,包含第一、第二电流源、第一斩波电路、电阻性元件、电容性元件以及处理电路。该第一、第二电流源分别提供第一、第二电流。该第一斩波电路包含耦接该第一电流源的第一连接端、耦接该第二电流源的第二连接端、耦接该电阻性元件的第三连接端,以及耦接该电容性元件的第四连接端。该处理电路对应横跨该电阻性元件的第一电压与横跨该电容性元件的第二电压来产生输出时钟。该第一斩波电路将该第一、第二连接端分别且交替地耦接至该第三、第四连接端。该电阻性元件与该电容性元件分别且交替地接收该第一、第二电流。

技术研发人员:刘宇华,邱耀德

受保护的技术使用者:达发科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!