SMT良率优化方法与流程

本发明涉及led,尤其是一种smt良率优化方法。

背景技术:

1、随着led的行业的不断发展,从之前的大尺寸封装逐渐升级为小尺寸大功率封装路线,大功率产品csp芯片级封装成为了主流。但是,由于csp芯片极封装焊盘较小,例如,目前主流的2323产品(芯片尺寸为23*23mm)中,焊盘大小仅为0.57*1.22mm;1313产品(芯片尺寸为13*13mm)中,焊盘大小仅为0.18*0.62mm等。过小的封装焊盘对于smt(表面组装技术)生产过程要求非常高,常规方法smt炉后经常出现旋转(超出5°)、偏移、起翘、开路等不良现象,严重影响了产品良率。

技术实现思路

1、为了克服以上不足,本发明提供了一种smt良率优化方法,通过对电极焊盘、钢网开口及厚度、锡膏的精确控制,提高smt的良率。

2、本发明提供的技术方案为:

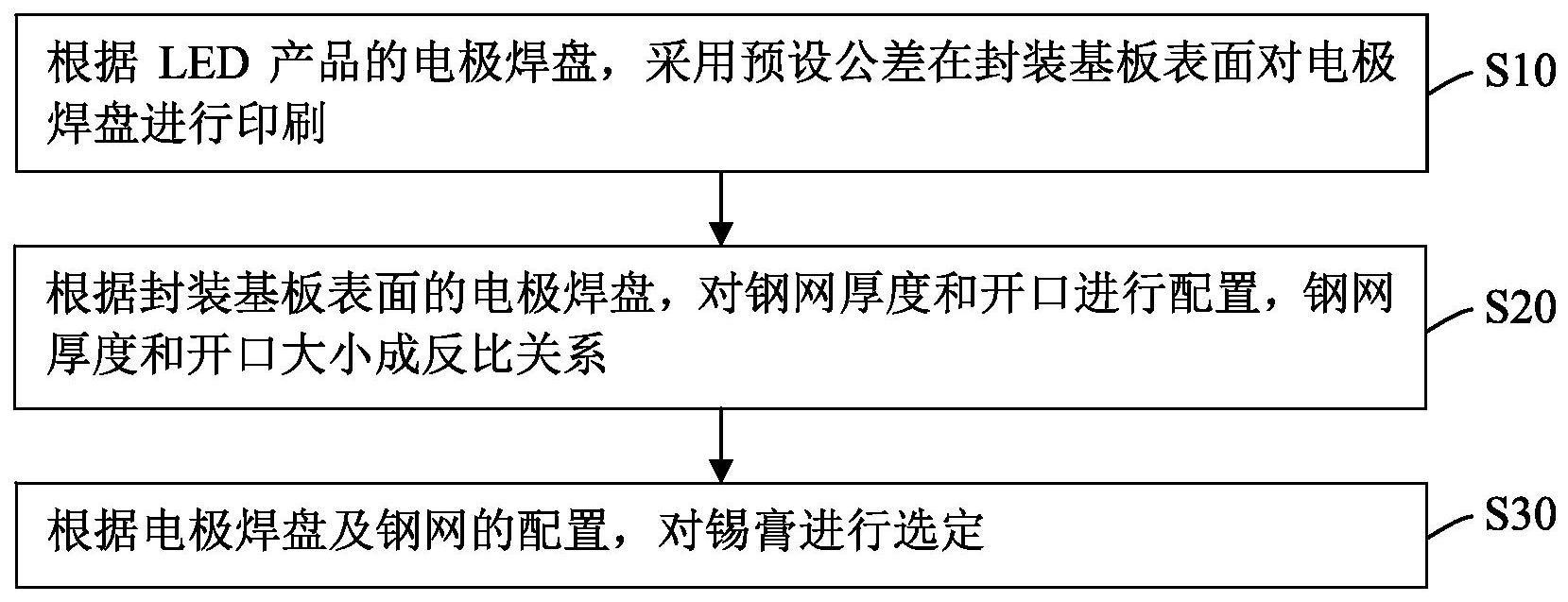

3、一种smt良率优化方法,包括:

4、根据led产品的电极焊盘,采用预设公差在所述封装基板表面对电极焊盘进行印刷;

5、根据封装基板表面的电极焊盘,对钢网厚度和开口进行配置,所述钢网厚度和开口大小成反比关系;

6、根据电极焊盘及钢网的配置,对锡膏进行选定。

7、进一步优选地,所述预设公差为±0.05。

8、进一步优选地,所述钢网开口的形状与所述封装基板表面电极焊盘的形状匹配,且钢网开口为电极焊盘大小的75%~95%,钢网厚度为0.04-0.06mm。

9、进一步优选地,所述锡膏的粒径为10~45μm。

10、本发明提供的smt良率优化方法,综合对焊盘的精度控制、钢网的厚度及开口比例的控制、锡膏的颗粒直径选用多个方面,将smt工艺的不良率降低为0.02%左右,大大提高了生产效率及良率,降低了成本。

技术特征:

1.一种smt良率优化方法,其特征在于,包括:

2.如权利要求1所述的smt良率优化方法,其特征在于,所述预设公差为±0.05。

3.如权利要求1所述的smt良率优化方法,其特征在于,所述钢网开口的形状与所述封装基板表面电极焊盘的形状匹配,且钢网开口为电极焊盘大小的75%~95%,钢网厚度为0.04~0.06mm。

4.如权利要求1或2或3所述的smt良率优化方法,其特征在于,所述锡膏的粒径为10~45μm。

技术总结

本发明提供了一种SMT良率优化方法,包括:根据LED产品的电极焊盘,采用预设公差在封装基板表面对电极焊盘进行印刷;根据封装基板表面的电极焊盘,对钢网厚度和开口进行配置,钢网厚度和开口大小成反比关系;根据电极焊盘及钢网的配置,对锡膏进行选定。其综合对焊盘的精度控制、钢网的厚度及开口比例的控制、锡膏的颗粒直径选用多个方面,将SMT工艺的不良率降低为0.02%左右,大大提高了生产效率及良率,降低了成本。

技术研发人员:王吉军,刘鹏

受保护的技术使用者:江西省昌大光电科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!