一种模数转换器

本发明涉及一种低功耗型模数转换器,本发明利用cmos工艺实现低功耗型模数转换器的设计,模数转换器的低功耗特性有利于设备可以长时间运行,减小散热。

背景技术:

1、大部分模数转换器在设计时没有考虑在片上集成输入缓冲器,而在应用时需要加入输入缓冲器进行阻抗匹配变换,降低前级电路的输出阻抗、增加驱动负载的能力以保证采样的精确度,然而前述方式会造成功耗上升。

2、例如德州仪器公司(ti)的ads7039-q1芯片(电源电压3.3v,采样率2msps,功耗1.2mw)以及ads7041芯片(电源电压1.8v,采样率1msps,功耗189μw)等芯片均未集成输入缓冲器,实际应用中需考虑输入缓冲器设计并分配相应功耗。

技术实现思路

1、本发明要解决的技术问题是:传统的模数转换器在设计时没有考虑在片上集成输入缓冲器,增加了功耗。

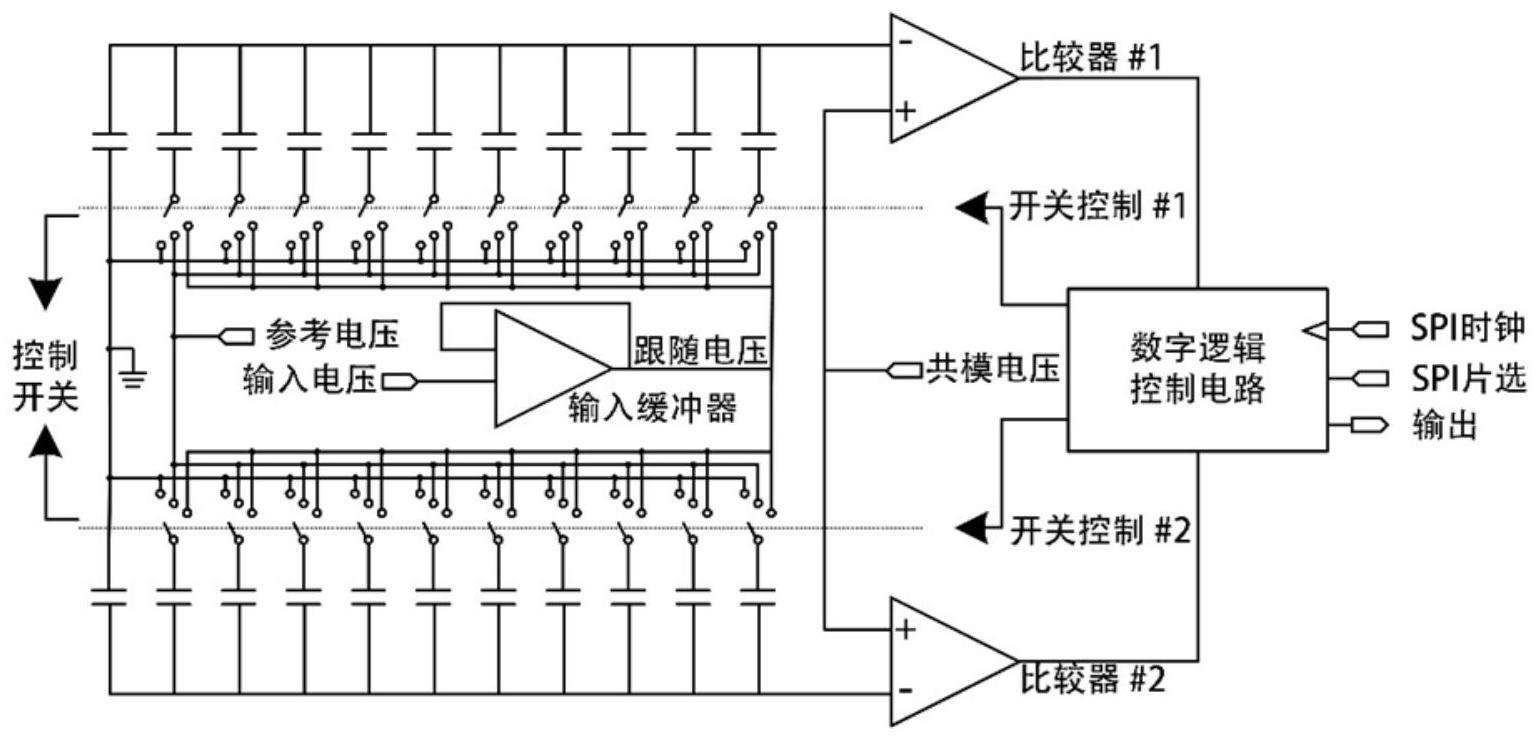

2、为了解决上述技术问题,本发明的技术方案是提供了一种模数转换器,该模数转换器的位数为n位,其特征在于,包括输入缓冲器、输入通道一、输入通道二以及数字逻辑控制电路,其中:

3、输入电压通过输入缓冲器得到跟随电压,跟随电压同时输入输入通道一以及输入通道二;

4、数字逻辑控制电路控制输入通道一以及输入通道二交替地工作于采样模式以及转换模式,其中:数字逻辑控制电路通过工作于采样模式的输入通道完成对跟随电压的采样;数字逻辑控制电路通过工作于转换模式的输入通道,基于已采样的电压获得最终的模数转换结果。

5、优选地,所述输入通道一包括比较器一;比较器一的反相输入端与二进制权重的dac电容阵列一的一端相连,dac电容阵列一的另一端连接n*3个由所述数字逻辑控制电路控制的控制开关一,每个控制开关一连接dac电容阵列一中的一个电容;通过控制开关一将跟随电压、参考电压或接地信号接入所述输入通道一,使所述输入通道一工作于采样模式或转换模式;

6、所述输入通道二包括比较器二;比较器二的反相输入端与二进制权重的dac电容阵列二的一端相连,dac电容阵列二的另一端连接n*3个由所述数字逻辑控制电路控制的控制开关二,每个控制开关二连接dac电容阵列二中的一个电容;通过控制开关二将跟随电压或接地信号接入所述输入通道二,使所述输入通道二工作于采样模式或转换模式;

7、比较器一以及比较器二的同相输入端接入共模电压。

8、优选地,当所述跟随电压接入所述输入通道一或所述输入通道二时,所述输入通道一或所述输入通道二工作于采样模式;当所述接地信号接入所述输入通道一或所述输入通道二时,所述输入通道一或所述输入通道二工作于保持模式。

9、优选地,当所述输入通道一或所述输入通道二工作于采样模式时,由所述数字逻辑控制电路控制控制开关一或控制开关二将所述dac电容阵列一或所述dac电容阵列二的下极板接到跟随电压,采样完成后,由所述数字逻辑控制电路控制控制开关一或控制开关二将所述dac电容阵列一或所述dac电容阵列二的下极板的下极板接到所述接地信号,进入保持状态;

10、当所述输入通道一或所述输入通道二工作于转换模式时,包括以下步骤:

11、步骤1、由所述数字逻辑控制电路控制控制开关一或控制开关二将所述dac电容阵列一或所述dac电容阵列二中的最高位电容接到参考电压,其它位电容接到地;

12、步骤2、将最高位电容做为当前位电容;

13、步骤3、等待下一个时钟周期到来;

14、步骤4、在当前一个时钟周期,所述数字逻辑控制电路根据比较器一或比较器二的输出结果对所述控制开关一或控制开关二进行控制:

15、如果比较器一或比较器二的输出为高电平,则所述控制开关一或控制开关二保持现行状态,并把当前位电容的下一位电容接到参考电压,将下一位电容做为当前位电容后,返回步骤3,直至完成n次迭代,即可得到一个n位模数转换器的结果,通过所述输入通道一或所述输入通道二获得的n位模数转换器的结果是在所述输入通道二或所述输入通道一采样的时候输出到所述模数转换器外的;

16、如果比较器一或比较器二的的输出为低电平,则通过控制所述控制开关一或控制开关二将当前位电容接到接地信号,并把当前位电容的下一位电容接到参考电压,将下一位电容做为当前位电容后,返回步骤3,直至完成n次迭代,即可得到一个n位模数转换器的结果,通过所述输入通道一或所述输入通道二获得的n位模数转换器的结果是在所述输入通道二或所述输入通道一采样的时候输出到所述模数转换器外的;

17、得到所述输入通道一或所述输入通道二的n位模数转换器的结果后,所述数字逻辑控制电路控制所述控制开关一或控制开关二将所述dac电容阵列一或所述dac电容阵列二的下极板都接到接地信号,以等待所述输入通道二或所述输入通道一采样完成。

18、优选地,所述数字逻辑控制电路通过spi通讯的方式控制所述输入通道一以及所述输入通道二交替地工作于所述采样模式以及所述转换模式。

19、本发明公开的模数转换器包含两个通道,将采样与转换过程分解,一个通道在转换时另一通道在采样。对于逐次逼近型模数转换器,与传统的工作模式相比,在最高采样频率不变的情况下,本发明的采样时间可以增加约n倍(n为模数转换器位数)。因此,在相同建立精度要求下,输入缓冲器单位增益带宽可相应减少,从而降低功耗。

技术特征:

1.一种模数转换器,该模数转换器的位数为n位,其特征在于,包括输入缓冲器、输入通道一、输入通道二以及数字逻辑控制电路,其中:

2.如权利要求1所述的一种模数转换器,其特征在于,所述输入通道一包括比较器一;比较器一的反相输入端与二进制权重的dac电容阵列一的一端相连,dac电容阵列一的另一端连接n*3个由所述数字逻辑控制电路控制的控制开关一,每个控制开关一连接dac电容阵列一中的一个电容;通过控制开关一将跟随电压、参考电压或接地信号接入所述输入通道一,使所述输入通道一工作于采样模式或转换模式;

3.如权利要求2所述的一种模数转换器,其特征在于,当所述跟随电压接入所述输入通道一或所述输入通道二时,所述输入通道一或所述输入通道二工作于采样模式;当所述接地信号或所述参考电压接入所述输入通道一或所述输入通道二时,所述输入通道一或所述输入通道二工作于转换模式。

4.如权利要求3所述的一种模数转换器,其特征在于,当所述输入通道一或所述输入通道二工作于采样模式时,由所述数字逻辑控制电路控制控制开关一或控制开关二将所述dac电容阵列一或所述dac电容阵列二的下极板接到跟随电压,采样完成后,由所述数字逻辑控制电路控制控制开关一或控制开关二将所述dac电容阵列一或所述dac电容阵列二的下极板的下极板接到所述接地信号,进入保持状态;

5.如权利要求1所述的一种模数转换器,其特征在于,所述数字逻辑控制电路通过spi通讯的方式控制所述输入通道一以及所述输入通道二交替地工作于所述采样模式以及所述转换模式。

技术总结

本发明公开了一种模数转换器,其特征在于,包括输入缓冲器、输入通道一、输入通道二以及数字逻辑控制电路,其中,数字逻辑控制电路控制输入通道一以及输入通道二交替地工作于采样模式以及转换模式。本发明公开的模数转换器包含两个通道,将采样与转换过程分解,一个通道在转换时另一通道在采样。对于逐次逼近型模数转换器,与传统的工作模式相比,在最高采样频率不变的情况下,本发明的采样时间可以增加约N倍。因此,在相同建立精度要求下,输入缓冲器单位增益带宽可相应减少,从而降低功耗。

技术研发人员:吕宏鸣,古昕玥

受保护的技术使用者:上海科技大学

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!