NAND闪存及其制作方法与流程

本发明涉及半导体,尤其涉及一种nand闪存及其制作方法。

背景技术:

1、闪存(flash memory)是一种电可擦除可编程只读存储器(electricallyerasable programmable read only memory,eeprom),具有非易失、读写速度快、抗震、低功耗、体积小等特性,目前己广泛应用于嵌入式系统、航空航天、消费电子等领域。闪存存储器主要分为nor型和nand型两种,nand闪存相对于nor闪存拥有更大的容量,适合进行数据存储。

2、现有技术的nand闪存制作中,主要研发方向是增加密度与缩小元件,在此过程中,现有nand闪存的扩展限制主要体现在:1ynm(相当于14-16nm级别)已达到了单元扩展的极限,单元扩展在1ynm以下的nand闪存存在短通道效应的问题。

3、因此,如何在nand闪存的制作过程中克服短通道效应是一个亟待解决的问题。

技术实现思路

1、鉴于上述现有技术的不足,本发明的目的在于提供一种nand闪存及其制作方法,旨在解决现有nand闪存制作过程中存在短通道效应的问题。

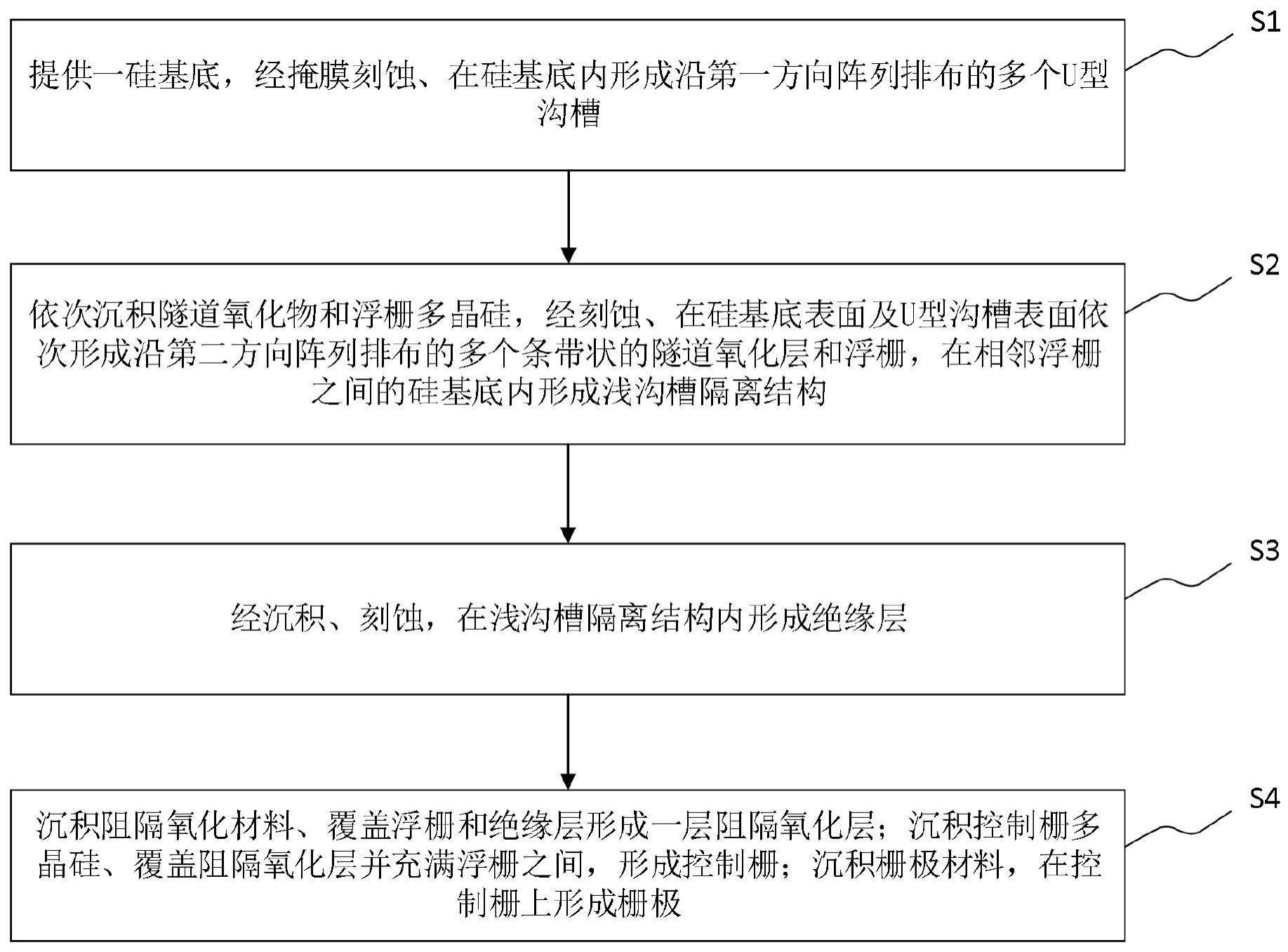

2、本发明的技术方案如下:本发明提供一种nand闪存及其制作方法,其中制作方法包括以下步骤:s1、提供一硅基底,经掩膜刻蚀、在硅基底内形成沿第一方向阵列排布的多个u型沟槽;s2、依次沉积隧道氧化物和浮栅多晶硅,经刻蚀、在硅基底表面及u型沟槽表面依次形成沿第二方向阵列排布的多个条带状的隧道氧化层和浮栅,在相邻浮栅之间的硅基底内形成浅沟槽隔离结构,第二方向垂直于第一方向;s3、经沉积、刻蚀,在浅沟槽隔离结构内形成绝缘层;s4、沉积阻隔氧化材料、覆盖浮栅和绝缘层形成一层阻隔氧化层;沉积控制栅多晶硅、覆盖阻隔氧化层并充满浮栅之间,形成控制栅;沉积栅极材料,在控制栅上形成栅极。

3、于本发明的一实施例中,步骤s1中,u型沟槽底部的纵截面呈半圆形。

4、于本发明的一实施例中,步骤s1中,硅基底表面自然氧化形成有一层基底氧化膜,经掩膜刻蚀、在硅基底内形成沿第一方向阵列排布的多个u型沟槽,具体包括:经沉积,在基底氧化膜上形成一层绝缘膜,经刻蚀、去除基底氧化膜和绝缘膜,在硅基底内形成沿第一方向阵列排布的多个u型沟槽。

5、于本发明的一实施例中,步骤s2中,浅沟槽隔离结构的纵截面呈倒梯形。

6、于本发明的一实施例中,步骤s3之后,还包括:刻蚀绝缘层,以与硅基底表面平齐。

7、于本发明的一实施例中,步骤s4中,形成栅极之后,采用注入技术,在栅极之间注入源极和漏极。

8、于本发明的一实施例中,步骤s4之后,还包括:s5、沉积氧化物,覆盖栅极形成含有气隙的覆盖氧化层;s6、经刻蚀、在每个条带状的浮栅的两端的覆盖氧化层内形成第一柱状槽,在第一柱状槽内沉积导电金属,形成第一金属接触点;s7、经沉积、在覆盖氧化层上形成第一介电层,经刻蚀、暴露位于每个条带状的浮栅的一端的第一金属接触点的表面,经沉积、覆盖第一金属接触点的表面和部分覆盖氧化层形成第一金属层;s8、经沉积、在第一介电层上形成第二介电层,经刻蚀、贯穿第一介电层和第二介层在第一金属接触点的表面上形成第二柱状槽,在第二柱状槽内沉积导电金属,形成第二金属接触点;s9、覆盖第二金属接触点的表面及第二介电层形成第二金属层。

9、于本发明的一实施例中,步骤s5中,气隙形成在相邻u型沟槽之间的硅基底上的覆盖氧化层内。

10、本发明提供一种nand闪存,基于上述的nand闪存的制作方法制备而成。

11、本发明提供一种nand闪存,包括硅基底,硅基底内凹设有多个u型沟槽,多个u型沟槽沿第一方向呈阵列排布;在硅基底表面及u型沟槽表面设有沿第二方向呈阵列排布的多个条带状的隧道氧化物层,隧道氧化物层上对应设有浮栅、且浮栅之间的硅基底内设有浅沟槽隔离结构;第二方向垂直于第一方向;浅沟槽隔离结构内充满有绝缘层,覆盖绝缘层表面和浮栅依次设有阻隔氧化层,阻隔氧化层上覆盖设有控制栅,控制栅表面设有栅极;自u型沟槽之间的硅基底表面向上延伸至覆盖栅极设有含有气隙的覆盖氧化层,气隙分布在u型沟槽之间的硅基底表面上的覆盖氧化层内;在每个条带状的浮栅的两端的覆盖氧化层内分别设有柱状第一金属接触点,第一金属接触点贯穿覆盖氧化层;覆盖氧化层表面设有第一介电层和第一金属层,金属层设于位于浮栅一端的第一金属接触点表面;覆盖第一介电层和第一金属层设有第二介电层,贯穿第一介电层和第二介电层、在位于浮栅另一端的第一金属接触点表面设有柱状第二金属接触点;覆盖第二金属接触点及第二介电层设有第二金属层。

12、如上,本发明的nand闪存及其制作方法,具有以下有益效果:

13、(1)能够克服短通道效应。

14、(2)工艺简单,降低投资成本。

技术特征:

1.一种nand闪存的制作方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的制作方法,其特征在于,所述步骤s1中,所述u型沟槽底部的纵截面呈半圆形。

3.根据权利要求1所述的制作方法,其特征在于,所述步骤s1中,所述硅基底表面自然氧化形成有一层基底氧化膜,

4.根据权利要求1所述的制作方法,其特征在于,所述步骤s2中,所述浅沟槽隔离结构的纵截面呈倒梯形。

5.根据权利要求1所述的制作方法,其特征在于,所述步骤s3之后,还包括:

6.根据权利要求1所述的制作方法,其特征在于,所述步骤s4中,形成所述栅极之后,采用注入技术,在所述栅极之间注入源极和漏极。

7.根据权利要求1所述的制作方法,其特征在于,所述步骤s4之后,还包括:

8.根据权利要求7所述的制作方法,其特征在于,所述步骤s5中,所述气隙形成在相邻所述u型沟槽之间的所述硅基底上的所述覆盖氧化层内。

9.一种nand闪存,其特征在于,采用如权利要求1-8任一项所述的制作方法制备而成。

10.一种nand闪存,其特征在于,包括硅基底,所述硅基底内凹设有多个u型沟槽,所述多个u型沟槽沿第一方向呈阵列排布;

技术总结

本发明公开一种NAND闪存及其制作方法,其中制作方法包括以下步骤:提供一硅基底,经掩膜刻蚀、在硅基底内形成沿第一方向阵列排布的多个U型沟槽;依次沉积隧道氧化物和浮栅多晶硅,经刻蚀、在硅基底表面及U型沟槽表面依次形成沿第二方向阵列排布的多个条带状的隧道氧化层和浮栅,在相邻浮栅之间的硅基底内形成浅沟槽隔离结构,第二方向垂直于第一方向;经沉积、刻蚀,在浅沟槽隔离结构内形成绝缘层;沉积阻隔氧化材料、覆盖浮栅和绝缘层形成一层阻隔氧化层;沉积控制栅多晶硅、覆盖阻隔氧化层并充满浮栅之间,形成控制栅;沉积栅极材料,在控制栅上形成栅极。本发明的NAND闪存及其制作方法,能够克服短通道效应。

技术研发人员:金镇湖

受保护的技术使用者:东芯半导体股份有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!