一种MMIC低噪声放大器的制作方法

一种mmic低噪声放大器

技术领域

1.本发明涉及放大器,特别是涉及一种mmic低噪声放大器。

背景技术:

2.随着无线技术迈入5g时代,新一代高性能射频收发系统提出更苛刻的要求,在高增益低噪声系数的基础上,由于低噪声放大器位于整个射频系统最前端,其性能的好坏直接整个系统的噪声系数以及接收灵敏度,是射频系统最为关键的部分之一。

3.目前市面上常见的一些mmic低噪声放大器芯片大多采用自偏置的拓扑结构,或者分布式的拓扑结构。对一款低噪声放大器而言,我们第一个关注的点往往就是其噪声系数,这是低噪放的一个极为重要指标。假设这种情景,当放大器内部本身没有任何噪声,输入信号夹杂着其他噪声信号一起通过放大器时, 放大器将所有信号进行放大,那么放大器输入端的输入信号与噪声比值将和输出端的输出信号与输出噪声比值一致。设计具有高增益低噪声系数的低噪声放大器很有必要的。

技术实现要素:

4.本实用新型的目的在于克服现有技术的不足,提供一种mmic低噪声放大器,具有高增益和低噪声系数,能够满足射频系统的更高要求。

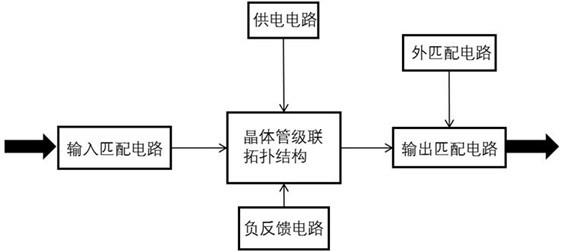

5.本实用新型的目的是通过以下技术方案来实现的:一种mmic低噪声放大器,包括输入匹配电路、晶体管级联拓扑结构、输出匹配电路和负反馈电路,所述输入匹配电路作为整个放大器的输出端口,接收外部输入信号,输入匹配电路的输出端与晶体管级联拓扑结构的输入端连接,晶体管级联拓扑结构的输出端与所述输出匹配电路的输入端连接,输出匹配电路的输出端作为整个放大器的输出端口,用于对外输出信号;所述负反馈电路与晶体管级联拓扑结构连接;

6.所述晶体管级联拓扑结构包括mos管m1、mos管m2和电阻rd,所述mos管m1的源极接地,mos管m1的栅极作为晶体管级联拓扑结构的输入端,mos管m1的漏极与mos管m2的源极连接,所述mos管m2的栅极接入vb接口,所述接口vb作为mos管m2的栅压供电端口,mos管m2的漏极通过电阻rd连接到电源端口,所述晶体管级联拓扑结构的输出端连接在mos管m2的漏极与电阻rd之间。

7.所述负反馈电路包括电容c2和电阻r2,所述电容c2的第一端连接到mos管m1的栅极,所述电容c2的第二端与电阻r2的第一端连接,所述电阻r2的第二端连接到mos管m2的漏极。

8.本实用新型的有益效果是:本实用新型提供的mmic低噪声放大器具有高增益和低噪声系数,能够满足射频系统的更高要求。

附图说明

9.图1为本实用新型的原理示意图;

10.图2为晶体管级联拓扑结构的原理图;

11.图3为负反馈电路及其连接原理示意图;

12.图4为实施例中增益和回波损耗曲线示意图;

13.图5为实施例中噪声系数曲线示意图;

14.图6为实施例中稳定性曲线示意图;

15.图7为实施例中p-1db曲线示意图。

具体实施方式

16.下面结合附图进一步详细描述本实用新型的技术方案,但本实用新型的保护范围不局限于以下所述。

17.如图1所示,一种mmic低噪声放大器,其特征在于:包括输入匹配电路、晶体管级联拓扑结构、输出匹配电路和负反馈电路,所述输入匹配电路作为整个放大器的输出端口,接收外部输入信号,输入匹配电路的输出端与晶体管级联拓扑结构的输入端连接,晶体管级联拓扑结构的输出端与所述输出匹配电路的输入端连接,输出匹配电路的输出端作为整个放大器的输出端口,用于对外输出信号;所述负反馈电路与晶体管级联拓扑结构连接;

18.所述晶体管级联拓扑结构包括mos管m1、mos管m2和电阻rd,所述mos管m1的源极接地,mos管m1的栅极作为晶体管级联拓扑结构的输入端,mos管m1的漏极与mos管m2的源极连接,所述mos管m2的栅极接入vb接口,所述接口vb作为mos管m2的栅压供电端口,mos管m2的漏极通过电阻rd连接到电源端口,所述晶体管级联拓扑结构的输出端连接在mos管m2的漏极与电阻rd之间。

19.所述负反馈电路包括电容c2和电阻r2,所述电容c2的第一端连接到mos管m1的栅极,所述电容c2的第二端与电阻r2的第一端连接,所述电阻r2的第二端连接到mos管m2的漏极。晶体管级联拓扑结构部分具体指共源共栅的拓扑结构,由共源极和共栅极的级联。由于共源放大级把电压信号转换为电流信号,而共栅放大级的输入信号为电流信号,故可把共源与共栅放大电路级联起来构成了共源共栅放大器,如图2所示:

20.负反馈电路具体包括rc电路,通过在晶体管级联拓扑结构的漏极和栅极之间加反馈电阻r2,可以在不加额外匹配电路的情况下获得具有较好增益平坦度和较小输入输出驻波比的放大器。其中电容c2主要是为了防止场效应管源级的直流偏置电压反馈回栅极中,影响场效应管的静态工作点。如图3所示:

21.在本申请的实施例中,所述输入匹配电路包括隔直电容c1,所述隔直电容c1的第一端作为输入匹配电路的输入端,接收外部输入信号;隔直电容c1的第二端作为输入匹配电路的输出端,与mos管m1的栅极连接。所述低噪声放大器还包括供电电路,用于为整个低噪声放大器供电,所述供电电路采用vcc电源和拓扑供电电源,所述拓扑供电电源连接到晶体管级联拓扑结构的单元端口,为晶体管级联拓扑结构供电。所述输出匹配电路包括隔直电容c3和扼流电感l1,隔直电容c3的第一端作为输出匹配电路的输入端,用于连接晶体管级联拓扑结构中mos管m2的漏极,隔直电容的第二端作为输出匹配电路的输出端,对外输出信号;所述扼流电感l1的第一端与隔直电容c3的第一端连接,隔直电容的第二端与vcc电源连接。所述低噪声放大器还包括外匹配电路,所述外匹配电路包括在输入端口串联的100pf电容,在输出端口串联的100pf电容,在供电端口与输出端口间串联的820nh扼流电感,以及

供电端口并联到地的电容。

22.该低噪声放大器通过晶体管级联拓扑结构使得晶体管组实现高增益,同时利用外匹配电路减小输入输出端口因匹配所造成的噪声系数变大来实现低噪声系数。

23.在本申请的实施例中,利用ads软件完成对低噪声放大器芯片的设计,其仿真曲线如下图所示,其中,图4为增益和回波损耗曲线,图5为噪声系数曲线示意图,图6为稳定性曲线示意图,图7为p-1db曲线示意图。通过仿真结果可以看出,具有高增益低噪声系数的低噪声放大器芯片,其频带覆盖300mhz~1ghz,增益大于27db,低噪声系数小于0.6db。

24.需要说明的是,在不背离本实用新型精神及其实质的情况下,熟悉本领域的技术人员可根据本实用新型作出各种相应的改变和变形,但这些相应的改变和变形都应属于本实用新型所附的权利要求的保护范围。

技术特征:

1.一种mmic低噪声放大器,其特征在于:包括输入匹配电路、晶体管级联拓扑结构、输出匹配电路和负反馈电路,所述输入匹配电路作为整个放大器的输出端口,接收外部输入信号,输入匹配电路的输出端与晶体管级联拓扑结构的输入端连接,晶体管级联拓扑结构的输出端与所述输出匹配电路的输入端连接,输出匹配电路的输出端作为整个放大器的输出端口,用于对外输出信号;所述负反馈电路与晶体管级联拓扑结构连接;所述晶体管级联拓扑结构包括mos管m1、mos管m2和电阻rd,所述mos管m1的源极接地,mos管m1的栅极作为晶体管级联拓扑结构的输入端,mos管m1的漏极与mos管m2的源极连接,所述mos管m2的栅极接入vb接口,所述接口vb作为mos管m2的栅压供电端口,mos管m2的漏极通过电阻rd连接到电源端口,所述晶体管级联拓扑结构的输出端连接在mos管m2的漏极与电阻rd之间。2.根据权利要求1所述的一种mmic低噪声放大器,其特征在于:所述负反馈电路包括电容c2和电阻r2,所述电容c2的第一端连接到mos管m1的栅极,所述电容c2的第二端与电阻r2的第一端连接,所述电阻r2的第二端连接到mos管m2的漏极。3.根据权利要求2所述的一种mmic低噪声放大器,其特征在于:所述输入匹配电路包括隔直电容c1,所述隔直电容c1的第一端作为输入匹配电路的输入端,接收外部输入信号;隔直电容c1的第二端作为输入匹配电路的输出端,与mos管m1的栅极连接。4.根据权利要求2所述的一种mmic低噪声放大器,其特征在于:所述低噪声放大器还包括供电电路,用于为整个低噪声放大器供电,所述供电电路采用vcc电源和拓扑供电电源,所述拓扑供电电源连接到晶体管级联拓扑结构的单元端口,为晶体管级联拓扑结构供电。5.根据权利要求4所述的一种mmic低噪声放大器,其特征在于:所述输出匹配电路包括隔直电容c3和扼流电感l1,隔直电容c3的第一端作为输出匹配电路的输入端,用于连接晶体管级联拓扑结构中mos管m2的漏极,隔直电容的第二端作为输出匹配电路的输出端,对外输出信号;所述扼流电感l1的第一端与隔直电容c3的第一端连接,隔直电容的第二端与vcc电源连接。6.根据权利要求1所述的一种mmic低噪声放大器,其特征在于:所述低噪声放大器还包括外匹配电路,所述外匹配电路包括在输入端口串联的100pf电容,在输出端口串联的100pf电容,在供电端口与输出端口间串联的820nh扼流电感,以及供电端口并联到地的电容。

技术总结

本实用新型公开了一种MMIC低噪声放大器,包括输入匹配电路、晶体管级联拓扑结构、输出匹配电路和负反馈电路,所述输入匹配电路作为整个放大器的输出端口,接收外部输入信号,输入匹配电路的输出端与晶体管级联拓扑结构的输入端连接,晶体管级联拓扑结构的输出端与所述输出匹配电路的输入端连接,输出匹配电路的输出端作为整个放大器的输出端口,用于对外输出信号;所述负反馈电路与晶体管级联拓扑结构连接。本实用新型提供的低噪声放大器具有高增益和低噪声系数,能够满足射频系统的更高要求。求。求。

技术研发人员:王玉军 钟莉 冯洋

受保护的技术使用者:成都泰格微波技术股份有限公司

技术研发日:2022.08.09

技术公布日:2022/11/24

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1