一种极微小传感器PCB的制作方法

本申请属于pcb,具体涉及一种极微小传感器pcb。

背景技术:

1、医疗领域上会应用到很多微型设备,用于探测和传感相关检测数据,因为这类设备应用的特殊性,必须要做到非常小型,这样对里面的电子元器件之母pcb,同样也要做到非常微小。pcb做到极其微小时,会导致布线密度过大,导致pcb的各层之间难以连通,并且无法满足阻抗的要求。

技术实现思路

1、本申请实施例的目的是提供一种极微小传感器pcb,其设计盘中孔、背钻孔等减少布线密度,从而可以解决背景技术中涉及的技术问题。

2、为了解决上述技术问题,本申请是这样实现的:

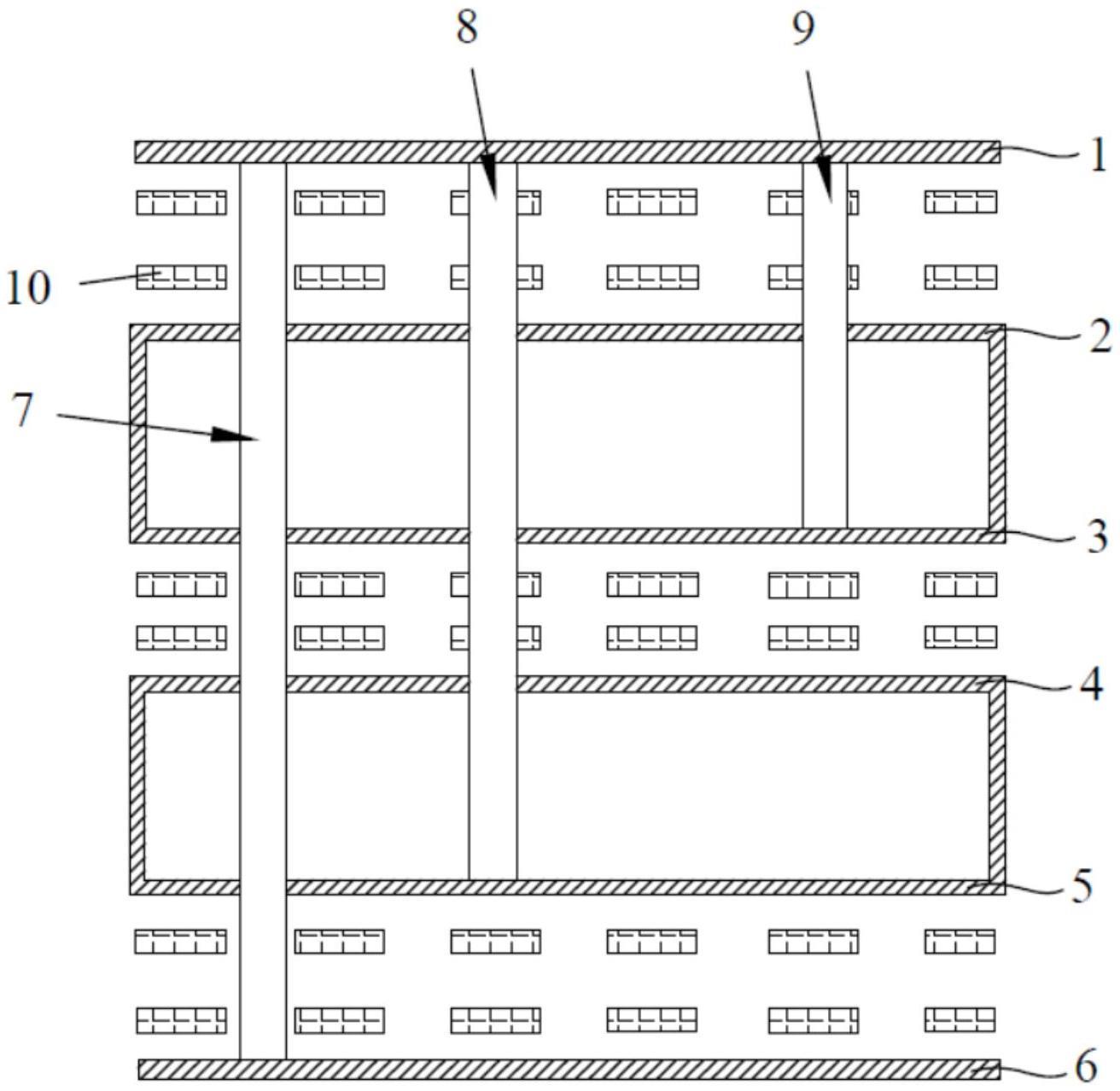

3、一种极微小传感器pcb,包括从上至下依次设置的芯片贴装层、第一接地屏蔽层、第二接地屏蔽层、走线层、第三接地屏蔽层以及器件贴装层,所述极微小传感器pcb还包括连通所述芯片贴装层至所述器件贴装层的盘中孔、连通所述芯片贴装层至所述第三接地屏蔽层的第一背钻孔连接以及连通所述芯片贴装层至所述第二接地屏蔽层的第二背钻孔。

4、作为本实用新型的一种优选改进,所述芯片贴装层与所述第一接地屏蔽层之间、所述第二接地屏蔽层与所述走线层之间以及所述第三接地屏蔽层与所述器件贴装层之间均设有介质层。

5、作为本实用新型的一种优选改进,所述极微小传感器pcb的尺寸为3.5*4mm。

6、作为本实用新型的一种优选改进,所述盘中孔、所述第一背钻孔以及所述第二背钻孔的孔径均为0.15mm。

7、本实用新型的有益效果如下:各层之间通过盘中孔和背钻孔连接,这样可减少通孔,最大限度增加线路布局;第一层设计芯片贴装层,第二/三层设计接地屏蔽层,第四层设计走线层,第五层设计接地屏蔽层,第六层设计器件贴装层,满足阻抗的匹配要求。

技术特征:

1.一种极微小传感器pcb,其特征在于,包括从上至下依次设置的芯片贴装层、第一接地屏蔽层、第二接地屏蔽层、走线层、第三接地屏蔽层以及器件贴装层,所述极微小传感器pcb还包括连通所述芯片贴装层至所述器件贴装层的盘中孔、连通所述芯片贴装层至所述第三接地屏蔽层的第一背钻孔连接以及连通所述芯片贴装层至所述第二接地屏蔽层的第二背钻孔。

2.根据权利要求1所述的一种极微小传感器pcb,其特征在于,所述芯片贴装层与所述第一接地屏蔽层之间、所述第二接地屏蔽层与所述走线层之间以及所述第三接地屏蔽层与所述器件贴装层之间均设有介质层。

3.根据权利要求1所述的一种极微小传感器pcb,其特征在于,所述极微小传感器pcb的尺寸为3.5*4mm。

4.根据权利要求1所述的一种极微小传感器pcb,其特征在于,所述盘中孔、所述第一背钻孔以及所述第二背钻孔的孔径均为0.15mm。

技术总结

本申请公开了一种极微小传感器PCB,包括从上至下依次设置的芯片贴装层、第一接地屏蔽层、第二接地屏蔽层、走线层、第三接地屏蔽层以及器件贴装层,所述极微小传感器PCB还包括连通所述芯片贴装层至所述器件贴装层的盘中孔、连通所述芯片贴装层至所述第三接地屏蔽层的第一背钻孔连接以及连通所述芯片贴装层至所述第二接地屏蔽层的第二背钻孔。本技术的有益效果如下:各层之间通过盘中孔和背钻孔连接,这样可减少通孔,最大限度增加线路布局;第一层设计芯片贴装层,第二/三层设计接地屏蔽层,第四层设计走线层,第五层设计接地屏蔽层,第六层设计器件贴装层,满足阻抗的匹配要求。

技术研发人员:黄先广,张可权,钟岳松

受保护的技术使用者:珠海牧泰莱电路有限公司

技术研发日:20221122

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!