晶振电路装置、主板控制系统及电子设备的制作方法

本申请涉及电子,尤其涉及一种晶振电路装置、主板控制系统及电子设备。

背景技术:

1、目前电路中,为了给集成电路(integrated circuit,ic)提供一个稳定的工作时钟,不少ic的外围电路上都会加上一个晶振电路。当主板上有几个ic,就需要有几个不同的晶振电路,使得每个ic都配置有与其一一对应连接的晶振电路,以通过晶振电路提供的时钟信号实现ic的启动。但是,针对每一个ic配置一个晶振电路,增加电路成本。

技术实现思路

1、本申请提供了一种晶振电路装置、主板控制系统及电子设备,以解决电路成本高的问题。

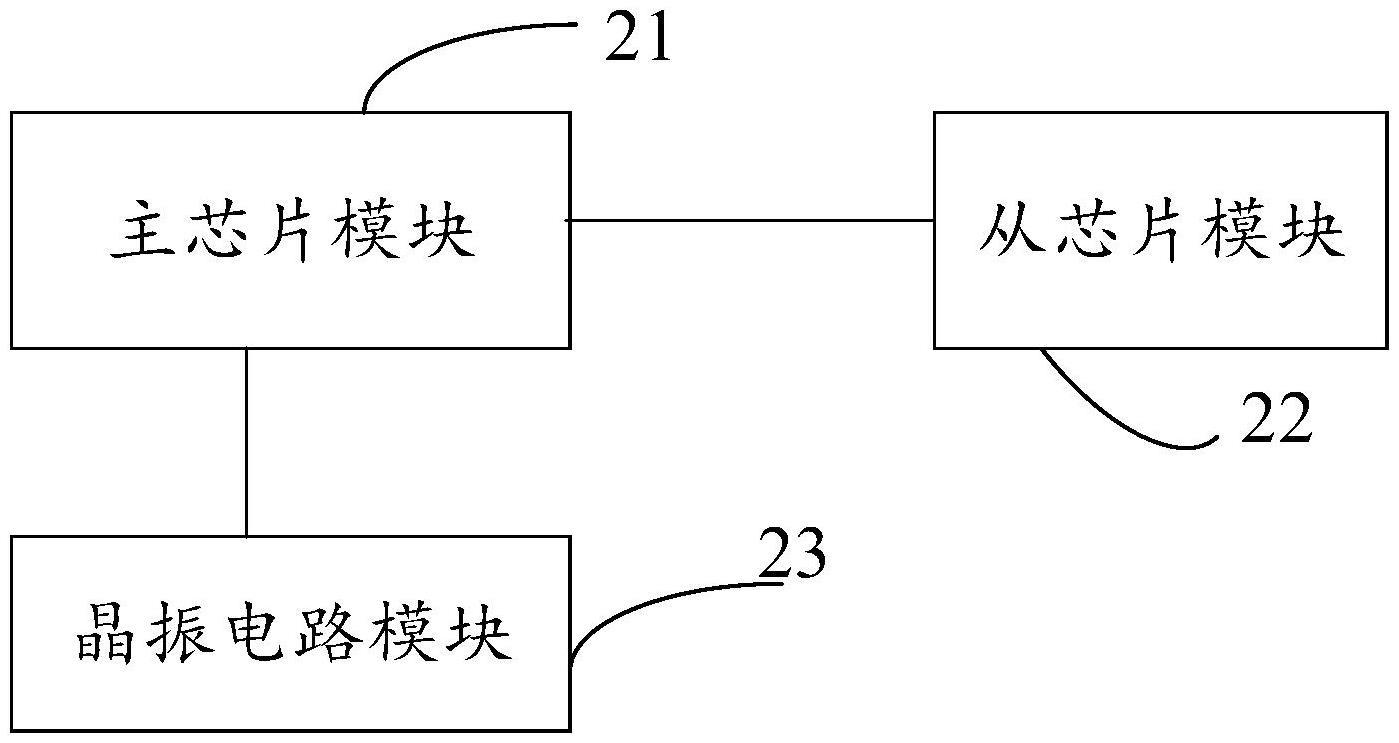

2、第一方面,本申请提供了一种晶振电路装置,包括:主芯片模块、从芯片模块及晶振电路模块;

3、其中,所述主芯片模块的时钟信号端与所述晶振电路模块的输出端电连接,所述主芯片模块的脉冲输出端与所述从芯片模块的时钟信号端电连接;

4、所述主芯片模块,用于根据所述晶振电路模块提供的时钟信号,通过所述脉冲输出端向所述从芯片模块输出目标脉冲信号;

5、所述从芯片模块,用于将所述目标脉冲信号确定为时钟输入信号,并基于所述时钟输入信号进行上电初始化。

6、可选的,所述晶振电路装置,还包括:

7、所述主芯片模块的串行总线端与所述从芯片模块的串行总线端电连接;

8、所述从芯片模块,还用于接收所述主芯片模块输出的主控指令,并基于所述主控指令输出驱动控制信号。

9、可选的,所述主芯片模块包括主控芯片;

10、所述主控芯片的第一时钟信号端与所述晶振电路模块的第一输出端电连接,所述主控芯片的第二时钟信号端与所述晶振电路模块的第二输出端电连接,所述主控芯片的串行数据端与所述从芯片模块的串行数据端电连接,所述主控芯片的串行时钟端与所述从芯片模块的串行时钟端电连接,所述主控芯片的脉冲输出端与所述从芯片模块的时钟信号端电连接。

11、可选的,所述从芯片模块包括从控芯片;

12、所述从控芯片的时钟信号端与所述主芯片模块的脉冲输出端电连接,所述从控芯片的串行数据端与所述主芯片模块的串行数据端电连接,所述从控芯片的串行时钟端与所述主芯片模块的串行时钟端电连接。

13、可选的,所述晶振电路装置,还包括:受控电路模块,所述受控电路模块与所述从芯片模块的信号输出端电连接;

14、所述受控电路模块,用于依据所述驱动控制信号,输出所述主控指令对应的指令执行结果。

15、可选的,所述受控电路模块包含一个或多个传感器,所述从芯片模块的信号输出端包含与所述传感器一一对应连接的信号输出端口。

16、可选的,所述受控电路模块包含扬声器,所述扬声器的输入端与所述从芯片模块的信号输出端电连接。

17、可选的,所述晶振电路模块包括:晶振、电阻、第一电容及第二电容;

18、所述晶振的第一端与所述电阻的第一端、所述主控芯片的第一时钟信号端以及所述第一电容的第一端电连接,所述晶振的第二端与所述第一电容的第二端、所述第二电容的第一端及参考地电连接,所述晶振的第三端与所述第二电容的第二端、所述主控芯片的第二时钟信号端及所述电阻的第二端电连接,所述晶振的第四端与所述参考地电连接。

19、第二方面,本申请提供了一种主板控制系统,包括:如第一方面任一所述的晶振电路装置。

20、第三方面,本申请提供了一种电子设备,包括:如第二方面所述的主板控制系统。

21、本申请实施例中的主芯片模块的时钟信号端与晶振电路模块的输出端电连接,主芯片模块的脉冲输出端与从芯片模块的时钟信号端电连接,使得主芯片模块可以根据晶振电路模块提供的时钟信号,通过脉冲输出端向从芯片模块输出目标脉冲信号,从而使得从芯片模块可以将目标脉冲信号确定为时钟输入信号,并可基于时钟输入信号进行上电初始化,实现了用脉冲信号替代外置晶振的功能,无需为从芯片模块配置相应的晶振电路,解决了现有技术中需要为主板中每个ic配置晶振电路所导致的电路成本高的问题,降低了电路硬件成本。

技术特征:

1.一种晶振电路装置,其特征在于,包括:主芯片模块、从芯片模块及晶振电路模块;

2.根据权利要求1所述晶振电路装置,其特征在于,还包括:

3.根据权利要求1所述晶振电路装置,其特征在于,所述主芯片模块包括主控芯片;

4.根据权利要求1所述晶振电路装置,其特征在于,所述从芯片模块包括从控芯片;

5.根据权利要求2所述晶振电路装置,其特征在于,还包括:受控电路模块,所述受控电路模块与所述从芯片模块的信号输出端电连接;

6.根据权利要求5所述晶振电路装置,其特征在于,所述受控电路模块包含一个或多个传感器,所述从芯片模块的信号输出端包含与所述传感器一一对应连接的信号输出端口。

7.根据权利要求5所述晶振电路装置,其特征在于,所述受控电路模块包含扬声器,所述扬声器的输入端与所述从芯片模块的信号输出端电连接。

8.根据权利要求3所述晶振电路装置,其特征在于,所述晶振电路模块包括:晶振、电阻、第一电容及第二电容;

9.一种主板控制系统,其特征在于,包括:如权利要求1至8任一所述的晶振电路装置。

10.一种电子设备,其特征在于,包括:如权利要求9所述的主板控制系统。

技术总结

本申请涉及电子技术领域,尤其设计一种晶振电路装置、主板控制系统及电子设备,本申请晶振电路装置中包括:主芯片模块、从芯片模块及晶振电路模块;其中,主芯片模块的时钟信号端与晶振电路模块的输出端电连接,主芯片模块的脉冲输出端与从芯片模块的时钟信号端电连接;主芯片模块,用于根据晶振电路模块提供的时钟信号,通过脉冲输出端向从芯片模块输出目标脉冲信号;从芯片模块,用于将目标脉冲信号确定为时钟输入信号,并基于时钟输入信号进行上电初始化,从而实现了用脉冲信号替代外置晶振的功能,无需为从芯片模块配置相应的晶振电路,解决了现有技术中需要为主板中每个IC配置晶振电路所导致的电路成本高的问题,降低了电路硬件成本。

技术研发人员:陶泽华,徐正新,洪明彬,魏海峰

受保护的技术使用者:深圳创维-RGB电子有限公司

技术研发日:20221207

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!