三维存储器件的制作方法

本技术是关于半导体器件,特别是关于一种三维存储器件。

背景技术:

1、现代电子产品中,存储器扮演着不可或缺的重要的角色。存储器除了用来存储使用者的数据,也负责存放中央处理器所执行的程式码以及运算过程中须暂时保存的信息。存储器通常包括存储单元阵列(memory array)以及用于读取(read)、感测(sense)、写入(write)或编程(program)存储单元信息的外围电路(peripheral circuits)。二进制(binary)系统的存储单元具有两种逻辑状态,分别代表逻辑1和逻辑0。其他存储器系统的存储单元可包括更多种逻辑状态。

2、目前发展出的存储器种类可分为易失性存储器(volatile memory)与非易失性存储器(non-volatile memory)。常见的易失性存储器包括动态随机存储器(dynamic randomaccess memory,dram)和静态随机存储器(static random access memory,sram),其数据会在断电后消失,而必须在下次供电时重新输入。非易失性存储器包括唯读式存储器(readonly memory,rom)和闪存(flash memory),其存储的数据即使切断电源仍然存在,因此在重新供电后可以直接读取早先存储的有效数据。为了在面积效率、读写速度、可靠度、功耗及制造成本等方面达到各种先进电子产品的规格需求,本领域仍持续针对存储器的结构及制造方法进行改良。

技术实现思路

1、本实用新型目的在于提供一种三维存储器件,其存储单元是以串接成存储串结构的方式垂直设置在衬底上,可提高存储器件的面积效率。另外,借由使存储层填入通孔侧壁的凹陷而在存储单元的上侧和下侧形成凸出部,可改善存储单元之间的电性隔离,减少写入或读取时相邻存储单元之间的信号干扰问题。

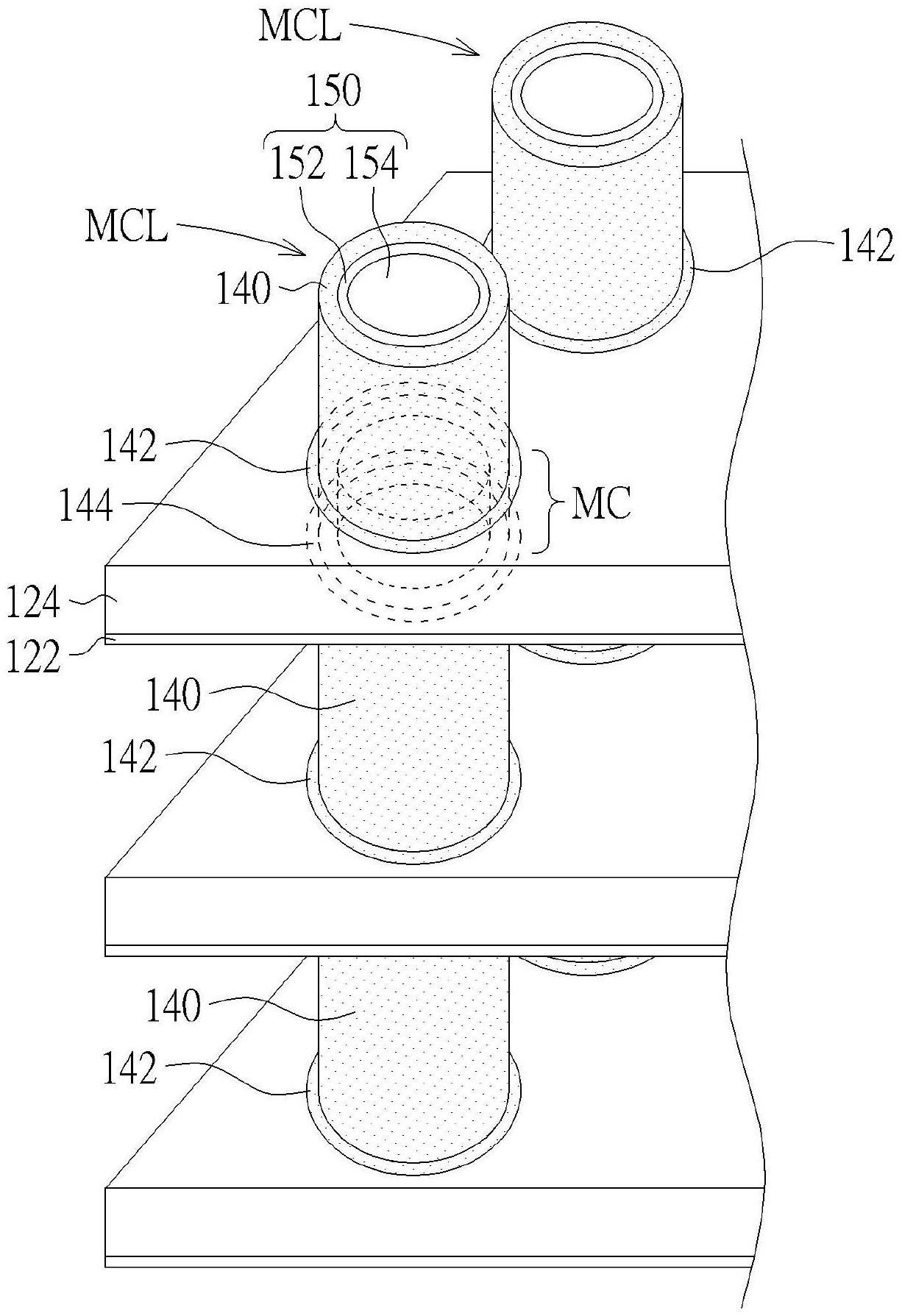

2、本实用新型一实施例提供了一种三维存储器件,包括一衬底、设置在所述衬底上的一堆叠结构,以及贯穿所述堆叠结构的一存储串结构。所述堆叠结构包括交替设置的多个导电层和多个电介质层。所述存储串结构包括一导电柱,以及介于所述导电柱与所述堆叠结构之间幷且围绕所述导电柱的一存储层,其中所述存储层包括多个第一凸出部,分别填充在所述导电层和所述电介质层之交界处的多个第一凹陷中。

技术特征:

1.一种三维存储器件,其特征在于,包括:

2.根据权利要求1所述的三维存储器件,其特征在于,所述堆叠结构还包括多个介面层,分别位于所述导电层的底面与所述电介质层之间。

3.根据权利要求2所述的三维存储器件,其特征在于,所述存储层还包括多个第二凸出部,分别填充在所述导电层、所述电介质层,和所述介面层之间的多个第二凹陷中,其中所述第二凹陷的深度大于所述第一凹陷的深度。

4.根据权利要求1所述的三维存储器件,其特征在于,还包括:

5.根据权利要求4所述的三维存储器件,其特征在于,所述衬垫层包括一金属氧化物层。

6.根据权利要求1所述的三维存储器件,其特征在于,所述导电层与所述第一凸出部接触的部分包括一圆化轮廓。

7.根据权利要求1所述的三维存储器件,其特征在于,所述存储串结构的顶部宽度大于底部宽度。

8.根据权利要求1所述的三维存储器件,其特征在于,所述多个导电层中,越上层的厚度越厚。

技术总结

本技术公开了一种三维存储器件,包括一衬底、设置在衬底上的一堆叠结构,以及贯穿堆叠结构的一存储串结构。堆叠结构包括交替设置的多个导电层和多个电介质层。存储串结构包括一导电柱,以及介于导电柱与堆叠结构之间幷且围绕着导电柱的一存储层,其中存储层包括多个第一凸出部,分别填充在导电层和电介质层之交界处的多个第一凹陷中,可改善存储单元之间的电性隔离,减少写入或读取时相邻存储单元之间的信号干扰问题。

技术研发人员:何世伟,戴灿发,刁德天宇,孔果果,朱贤士,余永健

受保护的技术使用者:福建省晋华集成电路有限公司

技术研发日:20221214

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!