包含填充狭缝及存储器胞元支柱的微电子装置以及相关存储器装置、电子系统及方法与流程

本公开的实施例涉及微电子装置设计及制造的领域。更特定来说,本公开涉及用于形成其中同时形成狭缝插塞及支柱插塞的微电子装置(例如,存储器装置,例如3d nand存储器装置)的方法以及相关装置、系统及方法。

背景技术:

1、存储器装置为电子系统提供数据存储。快闪存储器装置是各种存储器装置类型中的一者且在现代计算机及其它电子装置中具有众多用途。常规快闪存储器装置可包含具有布置成行及列的大数目个电荷存储装置(例如,存储器胞元,例如非易失性存储器胞元)的存储器阵列。在nand架构类型的快闪存储器中,布置成列的存储器胞元串联地耦合,且所述列的第一存储器胞元耦合到数据线(例如,位线)。

2、在“三维nand”存储器装置(其在本文中还可被称为“3d nand”存储器装置)中,一种类型的垂直存储器装置不仅是以行及列方式布置于水平阵列中的存储器胞元,而且水平阵列的阶层彼此叠置(例如,作为存储器胞元的垂直串)以提供存储器胞元的“三维阵列”。阶层的堆叠使导电材料与绝缘(例如,介电)材料垂直地交错。导电材料用作例如存储器胞元的存取线(例如,字线)的控制栅极。垂直结构(例如,包括沟道结构及隧穿结构的支柱)沿着存储器胞元的垂直串延伸。串的漏极端与垂直结构(例如,支柱)的顶部及底部中的一者相邻,而所述串的源极端与所述支柱的顶部及底部中的另一者相邻。漏极端可操作地连接到位线,而源极端可操作地连接到源极线。3d nand存储器装置还包含例如存取线(例如,字线)与所述装置的其它导电结构之间的电连接使得可选择垂直串的存储器胞元以用于写入、读取及擦除操作。

3、归因于此类装置的复杂性,制造可能涉及复制许多过程以实现所述装置的所要端结构及功能性。然而,在例如3d nand存储器装置的制造装置中重复处理步骤可能增加制造成本。例如,各自涉及单独掩模步骤、光刻步骤及蚀刻步骤的多个图案化序列可显著地增加制造成本。

技术实现思路

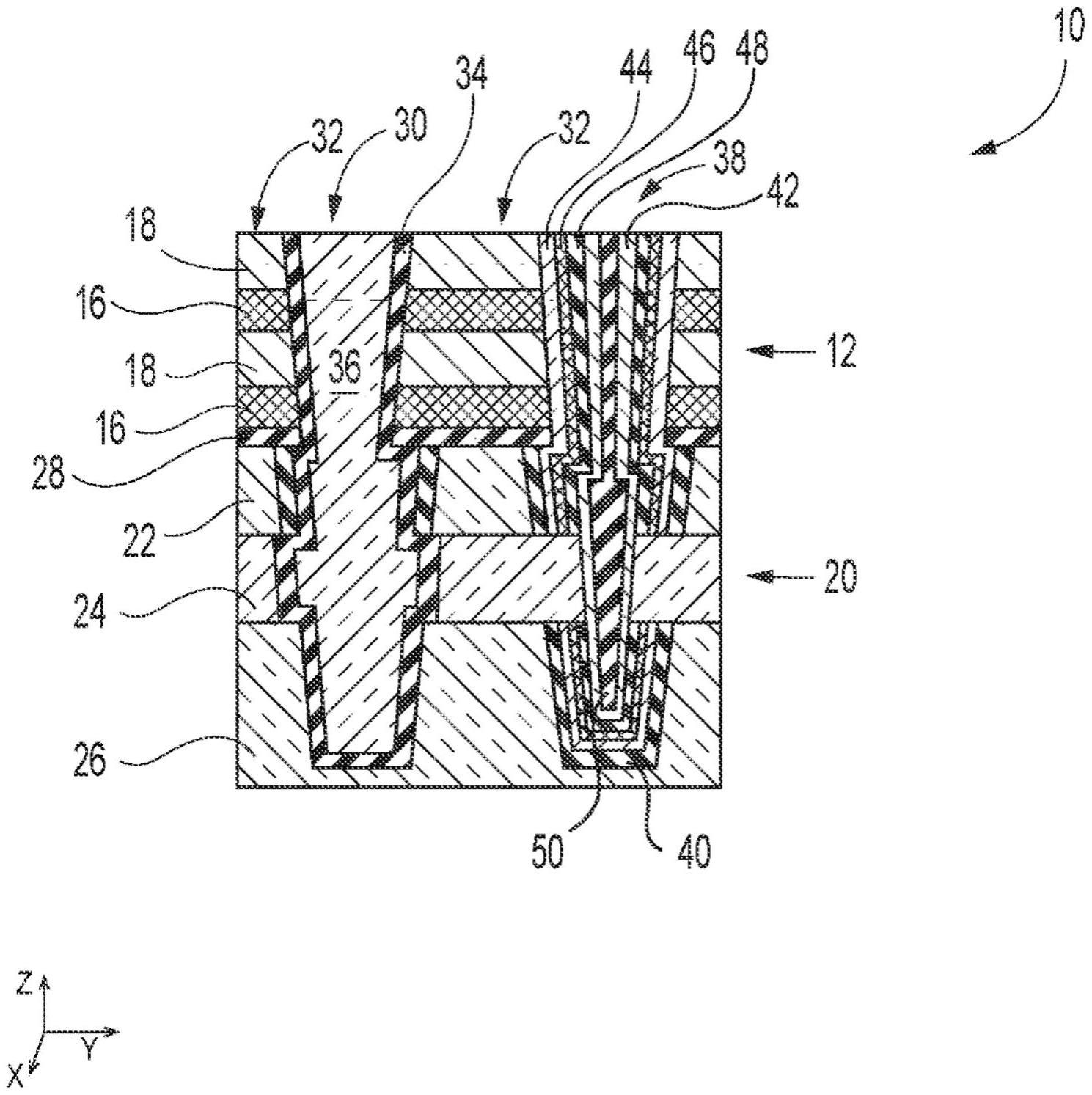

1、在一些实施例中,一种微电子装置包括源极结构、堆叠结构、填充狭缝及存储器胞元支柱。所述堆叠结构包括绝缘结构及导电结构的垂直交错序列。所述填充狭缝延伸穿过所述堆叠结构且到所述源极结构中。所述填充狭缝将所述堆叠结构划分成多个块。所述存储器胞元支柱延伸穿过所述堆叠结构且到所述源极结构中。所述存储器胞元支柱及所述填充狭缝终止于所述源极结构内大体上彼此相同的深度处。

2、在额外实施例中,一种存储器装置包括源极结构、堆叠结构、填充狭缝及存储器胞元支柱。所述源极结构包括源极区、横向接触区及帽盖区。所述填充狭缝各自包括填充有填充材料的介电衬垫而延伸穿过所述堆叠结构且到所述源极结构中。所述存储器胞元支柱各自包括沟道材料、隧穿介电材料、电荷阻挡材料及介电衬垫而延伸到所述源极结构中。所述存储器胞元支柱的所述介电衬垫的底部与所述填充狭缝的所述介电衬垫的底部大体上共面。

3、在进一步实施例中,一种形成微电子装置的方法包括形成源极结构,所述源极结构包括定位于帽盖区与源极区之间的牺牲区。在所述源极结构中形成支柱插塞。在形成所述支柱插塞的同时在所述源极结构中形成狭缝插塞。

4、在又进一步实施例中,一种电子系统包括:输入装置;输出装置;处理器装置,其可操作地耦合到所述输入装置及所述输出装置;及存储器装置,其可操作地耦合到所述处理器装置且包括至少一个微电子装置结构。所述至少一个微电子装置结构包括源极结构、堆叠结构、填充狭缝及存储器胞元支柱。所述堆叠结构包括绝缘结构及导电结构的垂直交错序列。所述填充狭缝延伸穿过所述堆叠结构且到所述源极结构中。所述填充狭缝将所述堆叠结构划分成块部分。所述存储器胞元支柱延伸穿过所述堆叠结构且到所述源极结构中。所述存储器胞元支柱的底部与所述填充狭缝的底部大体上共面。

技术特征:

1.一种微电子装置,其包括:

2.根据权利要求1所述的微电子装置,其中所述填充狭缝中的每一者包括与所述堆叠结构及所述源极结构水平地相邻的介电衬垫。

3.根据权利要求2所述的微电子装置,其中所述存储器胞元支柱中的每一者包含与所述源极结构的部分水平地相邻的额外介电衬垫。

4.根据权利要求3所述的微电子装置,其中所述填充狭缝中的每一者的所述介电衬垫的下垂直边界与所述存储器胞元支柱中的每一者的所述额外介电衬垫的下垂直边界大体上共面。

5.根据权利要求1所述的微电子装置,其中所述填充狭缝中的每一者的一部分包括多晶硅。

6.根据权利要求5所述的微电子装置,其中所述填充狭缝中的每一者的所述多晶硅与所述源极结构电隔离。

7.根据权利要求5所述的微电子装置,其中所述填充狭缝中的每一者的所述多晶硅通过氧化物衬垫与所述源极结构电隔离。

8.根据权利要求1到7中任一权利要求所述的微电子装置,其中所述存储器胞元支柱中的每一者的沟道材料物理地接触所述源极结构的导电接触区,所述导电接触区与所述沟道材料直接水平地相邻且环绕所述沟道材料。

9.根据权利要求8所述的微电子装置,其中所述源极结构进一步包括垂直地下伏于且耦合到所述导电接触区的额外导电区。

10.根据权利要求8所述的微电子装置,其中所述沟道材料及所述导电接触区各自包括多晶硅。

11.一种存储器装置,其包括:

12.根据权利要求11所述的存储器装置,其进一步包括所述填充狭缝中的每一者的在所述堆叠结构下方横向地延伸的一部分使得所述填充狭缝中的每一者的所述介电衬垫的至少一部分直接下伏于所述堆叠结构。

13.根据权利要求12所述的存储器装置,其进一步包括所述存储器胞元支柱中的每一者的在所述堆叠结构下方横向地延伸的一部分使得所述存储器胞元支柱中的每一者的所述介电衬垫的至少一部分直接下伏于所述堆叠结构。

14.一种形成微电子装置的方法,所述方法包括:

15.根据权利要求14所述的方法,其进一步包括形成所述支柱插塞及狭缝插塞以延伸穿过所述帽盖区及所述牺牲区且到所述源极结构的所述源极区中。

16.根据权利要求14所述的方法,其进一步包括形成所述支柱插塞及狭缝插塞以包括金属。

17.根据权利要求14所述的方法,其进一步包括形成所述牺牲区、所述帽盖区及所述源极区中的每一者以包括多晶硅。

18.根据权利要求14到17中任一权利要求所述的方法,其进一步包括:

19.根据权利要求18所述的方法,其中在所述支柱开口内形成所述支柱结构包括在所述支柱开口内形成存储器胞元支柱,所述存储器胞元支柱个别地包括电荷阻挡材料、由所述电荷阻挡材料环绕的电荷陷捕材料、由所述电荷陷捕材料环绕的隧穿介电材料、由所述隧穿介电材料环绕的沟道材料及由所述沟道材料环绕的填充材料。

20.根据权利要求18所述的方法,其进一步包括:

21.根据权利要求20所述的方法,其进一步包括:

22.根据权利要求21所述的方法,其进一步包括:

23.一种电子系统,其包括:

24.根据权利要求23所述的电子系统,其中所述存储器装置包括3d nand存储器装置。

25.根据权利要求23及24中任一权利要求所述的电子系统,其中所述存储器装置进一步包括控制单元,所述控制单元包括垂直地下伏于所述堆叠结构的cmos电路系统。

技术总结

一种微电子装置可包含源极结构及堆叠结构。所述堆叠结构可包含绝缘结构及导电结构的垂直交错序列。填充狭缝可延伸穿过所述堆叠结构且到所述源极结构中,所述狭缝将所述堆叠结构划分成多个块。存储器胞元支柱可延伸穿过所述堆叠结构且到所述源极结构中,所述存储器胞元支柱及所述填充狭缝终止于所述源极结构内大体上彼此相同的深度处。

技术研发人员:C·豪德,J·D·谢泼德森,C·E·卡特

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!