半导体装置以及电力变换装置的制作方法

本发明涉及半导体装置的结构,特别是涉及有效地适用于将多个低压元件串联连接而构成的共源共栅型的高压元件的技术。

背景技术:

1、在功率晶体管、功率二极管等功率半导体器件的开发中,重要的课题是制造具备高耐压的同时导通电阻低且开关损失少的器件。

2、功率晶体管通常配置于体(body)区域与漏极区域之间,并且具有比漏极区域低浓度地掺杂的漂移区域。以往的功率晶体管的导通电阻依赖于电流流动的方向的漂移区域的长度和漂移区域的掺杂浓度,在缩短漂移区域的长度或者提高漂移区域的掺杂浓度时,导通电阻会降低。

3、然而,在缩短漂移区域的长度或者提高漂移区域的掺杂浓度时,存在器件的耐压会降低这样的问题。

4、作为降低具有预定的耐压的功率晶体管的导通电阻的方法,熟知的是在漂移区域中设置互补地掺杂的补偿区域的技术、以及从漂移区域介电绝缘、例如将与晶体管的栅极或者源极端子连接的场板(field plate)设置于漂移区域的技术等。

5、在这些类型的功率晶体管中,补偿区域或者场板由于在器件为截止状态时部分地补偿漂移区域的掺杂电荷,所以能够向漂移区域进行更高浓度的掺杂,不用降低耐压而能够降低导通电阻。但是,这些器件的输出电容存在变大的趋势。

6、作为本技术领域的背景技术,例如有专利文献1那样的技术。在专利文献1中公开了“通过将多个功率晶体管以共源共栅连接方式自主地进行控制而能够提高耐压并且减小输出电容的半导体元件”。

7、专利文献1的技术不仅具有耐压提高、导通电阻降低、开关损失降低这样的功率晶体管的性能方面的优点,而且还具有通过共源共栅的连接级数能够使耐压变化这样的设计变容易的优点。

8、现有技术文献

9、专利文献1:美国专利申请公开第2012/0175635号说明书

技术实现思路

1、然而,在上述专利文献1中公开的技术由于使用了将栅电极与前一级的源电极进行连接的共源共栅连接,所以具有如下的课题。

2、[课题1]

3、第2级以后的功率晶体管由于需要使用在栅极电压为0v时接通的常开(normally-on)型的功率晶体管,所以功率晶体管的设计、制造工艺的自由度变低。另外,在使功率晶体管成为导通(接通)时,无法使栅极-源极间电压成为0v以上,所以存在无法充分地减小沟道电阻这样的问题。

4、[课题2]

5、在专利文献1中,第2级以后的功率晶体管的耐压被栅极氧化膜的耐压所限制,单独的功率晶体管的耐压通常被限制为20v左右。另外,为了得到高耐压,需要增加共源共栅连接的级数,但存在如下问题:随着级数增加,功率晶体管的沟道、将功率晶体管彼此进行连接的接触增加,寄生电阻变大。

6、[课题3]

7、由于将多个功率晶体管进行串联连接来构成,所以可靠性成为问题。

8、例如,在专利文献1中,在串联连接的功率晶体管之中即便有一个功率晶体管的源极-漏极间被破坏的情况下,该被破坏的功率晶体管的次级以后的功率晶体管也会变得全部无法截止,所以存在串联级数越大则故障概率越增加这样的问题。

9、因此,针对上述课题1,期望实现一种半导体装置,具有即便串联连接的多个功率晶体管中的第2级以后的功率晶体管是常关(normally-off)型也能够与初级的功率晶体管联动地自主控制的电路结构、即在初级的功率晶体管为导通时能够对第2级以后的功率晶体管施加原始的栅极-源极间电压的电路结构。

10、另外,针对上述课题2,期望实现一种半导体装置,即使串联连接的多个功率晶体管中的一部分功率晶体管成为源极-漏极间耐压不良(短路)也能够使其他功率晶体管截止,作为串联连接的一连串的功率晶体管整体的耐压不会显著降低。

11、而且,针对上述课题3,重要的是在功率晶体管具有的电阻分量之中恰当地设计沟道电阻、接触电阻等寄生电阻的比例,针对某个目标耐压,能够自由地设计串联连接的第2级以后的功率晶体管的串联连接的级数。即,期望实现第2级以后的功率晶体管的耐压不会被栅极氧化膜的耐压所限制的半导体装置。

12、因此,本发明的目的在于,提供一种设计/制造上的自由度以及可靠性高的半导体装置和使用该半导体装置的电力变换装置,在将多个功率晶体管进行串联连接而构成的共源共栅型的半导体装置中,在各个功率晶体管中能够使用常关型的功率晶体管,另外能够独立地设计各个功率晶体管的源极-漏极间耐压和栅极-源极间耐压,即使在一部分功率晶体管的源极-漏极间成为耐压不良的情况下,作为半导体装置整体而言耐压也不会显著降低。

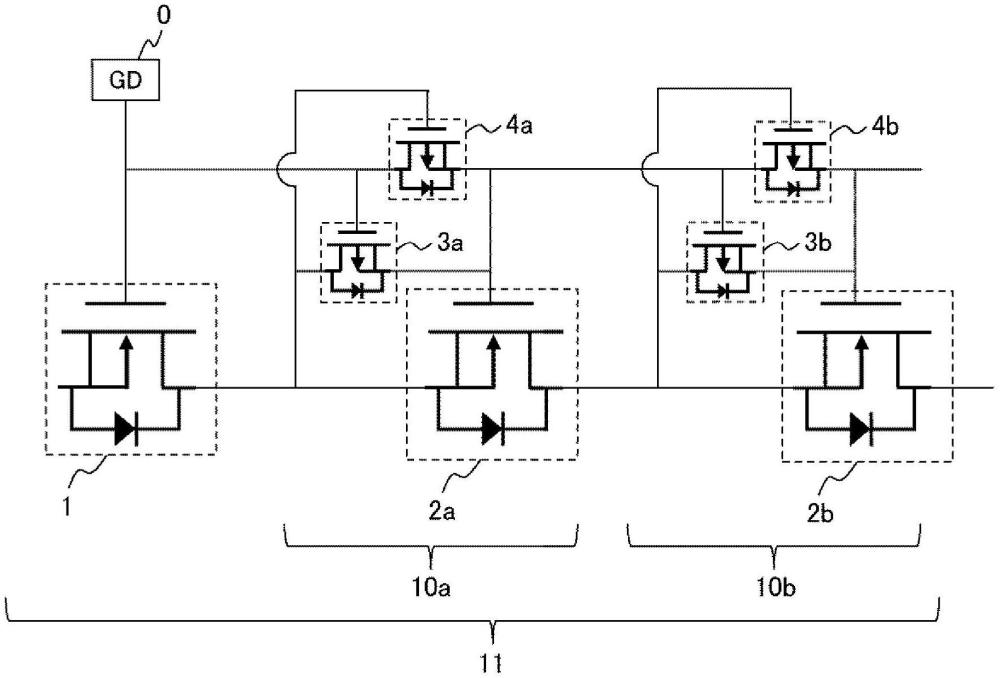

13、为了解决上述课题,本发明提供一种半导体装置,具备第1级的栅极被输入来自栅极驱动电路的驱动信号、并将前级的漏极和次级的源极串联连接而成的多级连接的多个半导体元件,其特征在于,在将n型和p型中的一方的导电类型设为第1导电类型、并将另一方的导电类型设为第2导电类型时,所述多个半导体元件是第1导电类型mosfet,所述半导体装置具备:一个或者多个第一第2导电类型mosfet,在从所述栅极驱动电路对第1级的半导体元件的栅极输入导通驱动信号时,将所述导通驱动信号供给到第2级以后的半导体元件,使所述第2级以后的半导体元件导通;以及一个或者多个第二第2导电类型mosfet,在从所述栅极驱动电路对所述第1级的半导体元件的栅极输入截止驱动信号时,所述第一第2导电类型mosfet截止,并且对所述第2级以后的半导体元件的栅极供给前级的半导体元件的源极或者漏极的电压而使所述第2级以后的半导体元件截止。

14、根据本发明,能够实现设计/制造上的自由度以及可靠性高的半导体装置和使用该半导体装置的电力变换装置,在将多个功率晶体管进行串联连接而构成的共源共栅型的半导体装置中,在各个功率晶体管中能够使用常关型的功率晶体管,另外能够独立地设计各个功率晶体管的源极-漏极间耐压和栅极-源极间耐压,即使在一部分功率晶体管的源极-漏极间成为耐压不良的情况下,作为半导体装置整体而言耐压也不会显著降低。

15、上述以外的课题、结构以及效果通过以下的实施方式的说明而会变得清楚。

技术特征:

1.一种半导体装置,具备第1级的栅极被输入来自栅极驱动电路的驱动信号、并将前级的漏极和次级的源极串联连接而成的多级连接的多个半导体元件,其特征在于,

2.根据权利要求1所述的半导体装置,其特征在于,

3.根据权利要求2所述的半导体装置,其特征在于,还具备:

4.根据权利要求3所述的半导体装置,其特征在于,

5.根据权利要求1所述的半导体装置,其特征在于,

6.根据权利要求1所述的半导体装置,其特征在于,

7.根据权利要求1所述的半导体装置,其特征在于,

8.根据权利要求1所述的半导体装置,其特征在于,

9.根据权利要求1所述的半导体装置,其特征在于,

10.根据权利要求1所述的半导体装置,其特征在于,

11.根据权利要求1至10中的任意一项所述的半导体装置,其特征在于,

12.根据权利要求1至10中的任意一项所述的半导体装置,其特征在于,

13.一种电力变换装置,其特征在于,

技术总结

提供设计/制造上的自由度及可靠性高的半导体装置,在将多个功率晶体管串联连接构成的共源共栅型的半导体装置中,在各个功率晶体管中能使用常关型的功率晶体管,另外能独立地设计各个功率晶体管的源极‑漏极间耐压和栅极‑源极间耐压,即使在一部分功率晶体管的源极‑漏极间成为耐压不良的情况下作为半导体装置整体而言耐压也不会显著降低。在具备第1级的栅极被输入来自栅极驱动电路的驱动信号并将前级的漏极和次级的源极串联连接而成的多级连接的多个半导体元件的半导体装置中,特征在于,在将N型和P型中的一方的导电类型设为第1导电类型并将另一方的导电类型设为第2导电类型时,所述多个半导体元件是第1导电类型MOSFET,所述半导体装置具备:一个或多个第一第2导电类型MOSFET,在从所述栅极驱动电路对第1级的半导体元件的栅极输入导通驱动信号时,将所述导通驱动信号供给到第2级以后的半导体元件,使所述第2级以后的半导体元件导通;和一个或多个第二第2导电类型MOSFET,在从所述栅极驱动电路对所述第1级的半导体元件的栅极输入截止驱动信号时,所述第一第2导电类型MOSFET截止,并且对所述第2级以后的半导体元件的栅极供给前级的半导体元件的源极或漏极的电压而使所述第2级以后的半导体元件截止。

技术研发人员:谷和树,原贤志

受保护的技术使用者:株式会社日立功率半导体

技术研发日:

技术公布日:2024/2/6

- 还没有人留言评论。精彩留言会获得点赞!