数字锁频环的压降检测和控制的制作方法

背景技术:

1、集成电路和分立电路包括用于从电源接收功率以向相关联的电路提供源电压的端子。电路(例如,反相器)通常连接在电源和电路公共端或地之间。在金属氧化物半导体场效应晶体管(mosfet)的情况下,栅极端子处的指定电压激活晶体管以产生用于驱动连接在输出端子与电源或地之间的电路元件并驱动连接至输出端子的后续电路的操作的电路路径。通常,电流和电路负载的量与操作速度和电源电压两者相关。由于许多电路的有源特性,负载有时会变化,并且有时会使供电电压电平从期望电平下降或降低。

2、电压压降是用于指当电源驱动负载时电压从期望电压电平下降的术语。在稳压系统中,当负载突然非常快速地增加时,输出电压可能下降。例如,可能发生导致电压压降的瞬态负载状况。如果压降过大,则导致电路故障。

3、在现有技术系统中,供电调整电路或″头部″电路可操作地设置在电源和电路之间,并且被稳压以调整或补偿电源中的此类变型。例如,一些解决方案包括相对于其他功率管理特征诸如功率状态改变以相对高的频率恒定地切换的头部电路,以便最小化来自瞬态响应的负载并且对供电电压进行稳压。这些头部电路通常被优化以非常快速地响应由于瞬态负载条件和其他负载条件引起的电压压降。

4、这些现有技术系统通常具有大量定制的模拟设计块,并且当它们为了响应瞬态负载条件而接入和断开连接相对大的场效应晶体管时,增加了显著的开销。该开销甚至在以稳态模式操作时发生。因此,此类系统不仅消耗宝贵的集成电路基板面,而且从功率观点来看效率低下。

技术实现思路

技术特征:

1.一种装置,所述装置包括:

2.根据权利要求1所述的装置,所述装置还包括:

3.根据权利要求2所述的装置,所述装置还包括状态机,所述状态机具有接收所述压降检测信号的输入和被耦接以控制所述锁存器的输出,其中所述状态机控制所述锁存器在所述压降检测电路不再检测到所述压降之后将所述压降检测信号保持达指定时间段,并且在所述指定时间段之后复位所述压降检测信号。

4.根据权利要求1所述的装置,其中所述dfll控制电路包括:

5.根据权利要求1所述的装置,其中所述dfll控制电路还可操作为在所述dfll处设定dfll增量,用于控制在所述时钟信号被减慢之后所述dfll多快地增加所述时钟信号的速度。

6.根据权利要求1所述的装置,其中所述压降检测电路包括电平转换器,用于将所述脉冲密度调制信号转换为以清洁供电电压为参考。

7.根据权利要求1所述的装置,其中所述压降检测电路包括比较器,所述比较器包括一系列反相器,所述一系列反相器至少包括第一互补金属氧化物半导体(cmos)反相器和第二cmos反相器,各自包括接收所述监测的供电电压的正电源端子,所述第一cmos反相器包括接收所述模拟信号的输入,所述第一cmos反相器被配置为当所述监测的供电电压接近指定电平时在消弧模式下操作。

8.根据权利要求1所述的装置,所述装置还包括:

9.根据权利要求1所述的装置,其中所述装置是处理器。

10.根据权利要求1所述的装置,其中所述装置还包括设备,所述设备是膝上型计算机、台式计算机、智能电话、平板计算机、服务器、游戏控制台和多媒体设备中的一者。

11.一种监测电源的方法,所述方法包括:

12.根据权利要求11所述的方法,所述方法还包括响应于所述压降检测信号,在指定时间段内选通所述时钟信号。

13.根据权利要求11所述的方法,所述方法还包括响应于所述压降检测信号,在所述压降检测电路不再检测到所述压降之后,控制锁存器将所述压降检测信号保持达指定时间段,并且在所述指定时间段之后复位所述压降检测信号。

14.根据权利要求11所述的方法,所述方法还包括在减慢所述时钟信号之后,随着时间以指定的周期性递增来增加时钟信号的速度。

15.根据权利要求14所述的方法,所述方法还包括设定dfll增量,用于控制在所述时钟信号被减慢后所述dfll多快地增加所述时钟信号的所述速度。

16.根据权利要求11所述的方法,所述方法还包括:

17.根据权利要求11所述的方法,所述方法还包括:

18.一种数据处理系统,所述数据处理系统包括:

19.根据权利要求18所述的数据处理系统,其中每个处理器块还包括:

20.根据权利要求19所述的数据处理系统,其中每个处理器块还包括状态机,所述状态机具有接收所述压降检测信号的输入和被耦接以控制所述锁存器的输出,其中所述状态机控制所述锁存器在所述压降检测电路不再检测到所述压降之后将所述压降检测信号保持达指定时间段,并且在所述指定时间段之后复位所述压降检测信号。

21.根据权利要求18所述的数据处理系统,其中每个dfll控制电路包括:

22.根据权利要求18所述的数据处理系统,其中所述dfll控制电路还可操作为在所述本地dfll处设定dfll增量,以用于控制在所述时钟信号被减慢之后所述本地dfll多快地增加所述时钟信号的速度。

23.根据权利要求18所述的数据处理系统,其中所述压降检测电路包括电平转换器,用于将所述脉冲密度调制信号转换为以清洁供电电压为参考。

24.根据权利要求18所述的数据处理系统,其中所述压降检测电路包括比较器,所述比较器包括一系列反相器,所述一系列反相器至少包括第一互补金属氧化物半导体(cmos)反相器和第二cmos反相器,各自包括接收所述相应监测的本地供电电压的正电源端子,所述第一cmos反相器包括接收所述模拟信号的输入,所述第一cmos反相器被配置为当所述相应监测的本地供电电压接近指定电平时在消弧模式下操作。

25.根据权利要求18所述的数据处理系统,其中所述处理器块中的至少一个处理器块还包括:

技术总结

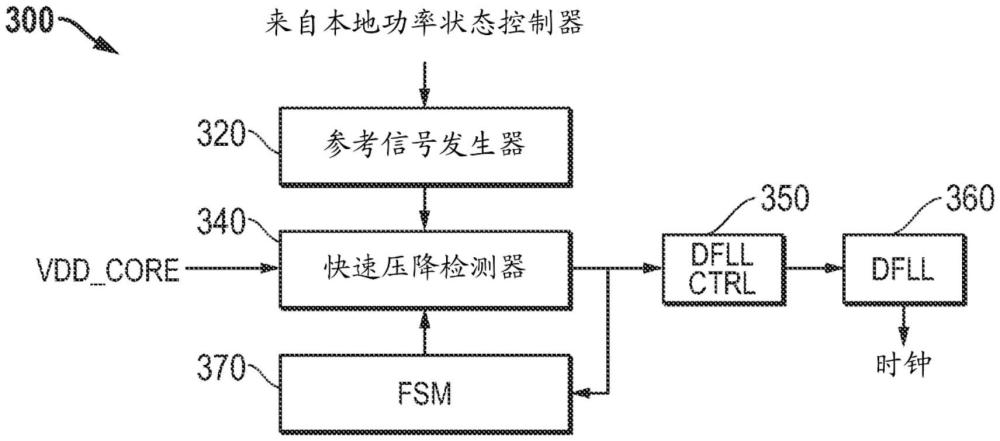

一种装置,包括参考信号发生器、压降检测电路、数字锁频环(DFLL)和DFLL控制电路。参考信号发生器接收数字值并基于该数字值产生脉冲密度调制信号。压降检测电路将脉冲密度调制信号转换为模拟信号,将该模拟信号与监测的供电电压进行比较,并且响应于检测到相对于该模拟信号该监测的供电电压的压降比指定值低,产生压降检测信号。该DFLL提供用于同步该监测的供电电压的域内的电路的时钟信号。该DFLL控制电路响应于接收到该压降检测信号而使该DFLL减慢该时钟信号。

技术研发人员:考希克·玛祖达尔,乔伊斯·丘克·韦·王,纳伊姆·伊布拉希姆·阿利,斯蒂芬·维克托·科索诺基

受保护的技术使用者:超威半导体公司

技术研发日:

技术公布日:2024/8/15

- 还没有人留言评论。精彩留言会获得点赞!