一种多电压域上下电复位中时序亚稳态消除方法及装置与流程

本发明涉及集成电路,尤其涉及一种多电压域上下电复位中时序亚稳态消除方法及装置。

背景技术:

1、复杂功能芯片通常内部有多种电压域工作需求,上电复位往往会遇到不同电压域或不同功能模块先后启动的时序处理问题。在这种多电源域的复杂功能芯片应用中,利用组合门逻辑控制来进行时序处理,通常是容易想到的解决方案,例如:

2、公开号为us10228415b1的发明专利公开了一种用于在集成电路中提供安全性的测试电路,包括控制电路和测试加电复位电路,所述控制电路确定所述集成电路是否配置在非安全条件下,并且响应于所述非安全条件产生控制信号。因此,测试加电复位电路在测试操作期间响应于控制信号选择性地禁用集成电路上的加电复位电路。所述测试上电复位电路接收来自所述控制电路的控制指令,并根据所述控制指令产生测试上电复位输出。所述集成电路包括逻辑门,所述逻辑门从所述上电复位电路接收所述测试上电复位输出和上电复位信号,并产生用于旁路所述上电复位电路对所述集成电路的操作的输出信号。

3、公开号为wo2016119471a1的发明专利申请公开了一种上电复位电路,包括电流偏置电路(110)、门限电平控制电路(120)及电容充放电电路(130);电流偏置电路(110)用于为门限电平控制电路(120)和电容充放电电路(130)提供不随电源变化的基准电流;门限电平控制电路(120)用于设定上、下电复位的门限电平值;电容充放电电路(130)用于根据门限电平控制电路(120)设定的门限电平值,输出上电复位信号;其中,电流偏置电路(110)包括第一路基准电流输出端、第二路基准电流输出端和第三路基准电流输出端,所述第一路基准电流输出端用于与门限电平控制电路(120)连接,所述第二路基准电流输出端和第三路基准电流输出端用于与电容充放电电路(130)连接。

4、公开号为us7348816b2的发明专利公开了一种用于上电复位的电路和方法,其通电复位电路包括第一通电复位单元,第二通电复位单元和逻辑门。所述第一上电复位单元产生第一上电复位信号,所述第一上电复位信号在第一温度的电源电压的第一电平处被激活,并且在第二温度的电源电压的第二电平处被激活。所述第二上电复位单元产生第二上电复位信号,所述第二上电复位信号在所述第一温度下在所述第二电平处被激活,并且在所述第二温度下在所述第一电平处被激活。所述逻辑门执行所述第一上电复位信号和所述第二上电复位信号的逻辑分离操作或逻辑合并操作,并产生第三上电复位信号。

5、但是利用组合门逻辑控制来进行时序处理的方式,可能会遇到触发器亚稳态问题或不可预测的延迟导致组合门逻辑产生时序偏差而引发毛刺(故障)。同时,处理时钟还会不可避免地产生jitter(抖动)。显然这类缺陷是复杂功能芯片的复位机制不可接受的,jitter或毛刺会诱导采样到的上升沿时间不确定,可能造成上电复位不正常,无法正常上电甚至致使整个芯片功能失效。

技术实现思路

1、为了解决上述问题,本发明提出一种多电压域上下电复位中时序亚稳态消除方法及装置,可解决复杂功能芯片的多电压域应用中的上电复位机制时序产生亚稳态或毛刺的问题,本发明应用脉冲信号计数对上电复位电路(por,power-on-reset)进行分段延迟处理,同时仅在分频后拍数少的情况下产生足够的延迟,以保护芯片内不同模块依次上电复位而不受到状态干扰。

2、本发明采用的技术方案如下:

3、一种多电压域上下电复位中时序亚稳态消除方法,包括以下步骤:

4、s1.目标芯片上电时,通过上电复位电路产生复位,同时通过分频采样电路对振荡器输出信号进行计时,生成第一时钟信号,并基于预设延迟生成第二时钟信号;

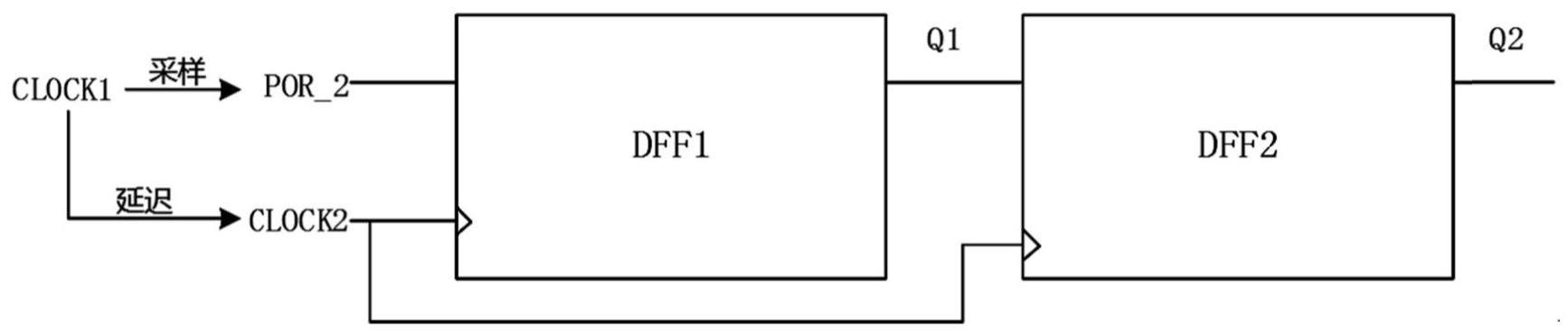

5、s2.对所述第一时钟信号进行预处理并采样,生成第一复位信号;基于所述第一复位信号和所述第二时钟信号,通过两级触发同步器进行同步处理生成第二复位信号,控制目标芯片进行上电复位。

6、进一步地,通过预复位电路进行各个电压域之间的衔接控制,使目标芯片在不同电源先后上电顺序条件下都能够正常工作。

7、进一步地,所述预复位电路包括第一反相器、第二反相器和下拉电阻,所述第一反相器的信号输入端电连接所述两级触发同步器的信号输出端,所述第一反相器的信号输出端电连接所述下拉电阻的第一端和所述第二反相器的信号输入端,所述下拉电阻的第二端接地,所述第二反相器的信号输出端电连接待复位器件的信号输入端。

8、进一步地,所述两级触发同步器能够替换为多级触发同步器。

9、一种多电压域上下电复位中时序亚稳态消除装置,包括上电复位电路、分频采样电路、预处理电路、延迟电路和两级触发同步器,所述上电复位电路、分频采样电路、预处理电路和两级触发同步器依次电连接,所述延迟电路电连接所述上电复位电路和两级触发同步器;所述上电复位电路用于产生复位,所述分频采样电路被配置为在复位时对振荡器输出信号进行计时生成第一时钟信号,并通过所述延迟电路生成第二时钟信号;所述预处理电路被配置为对所述第一时钟信号进行预处理并采样生成第一复位信号;所述两级触发同步器被配置为基于所述第一复位信号和所述第二时钟信号进行同步处理生成第二复位信号,控制目标芯片进行上电复位。

10、进一步地,还包括预复位电路,所述预复位电路电连接所述两级触发同步器,所述预复位电路被配置为进行各个电压域之间的衔接控制,使目标芯片在不同电源先后上电顺序条件下都能够正常工作。

11、进一步地,所述预复位电路包括第一反相器、第二反相器和下拉电阻,所述第一反相器的信号输入端电连接所述两级触发同步器的信号输出端,所述第一反相器的信号输出端电连接所述下拉电阻的第一端和所述第二反相器的信号输入端,所述下拉电阻的第二端接地,所述第二反相器的信号输出端电连接待复位器件的信号输入端。

12、进一步地,所述两级触发同步器能够替换为多级触发同步器。

13、本发明的有益效果在于:

14、1)基于本发明的时序亚稳态消除方法及装置,目标芯片各个模块上电延迟时间可根据实际应用选择,即por_1和por_2;

15、2)本发明通过两级触发同步器防止复位信号被毛刺或jitter的上升沿信号提前复位拉起,常规por上电复位电路不能正常工作。

16、3)本发明通过预复位电路保证各个电压域之间的衔接控制,,使目标芯片在不同电源先后上电顺序条件下都能够正常工作。该功能可以扩展到更多电源域工作,采用相同的方式预复位处理即可。

17、综上所述,为了防止连续数据信号两次变化发生的时间间隔过于靠近,从而导致其输出陷入亚稳态,本发明采用双触发同步的形式处理亚稳态问题,即使用触发器打两拍的方式进行同步,很好地解决了时钟上毛刺以及抖动偏差的问题,尽可能减少时钟不稳定性带来的芯片各种电路的上电安全。

技术特征:

1.一种多电压域上下电复位中时序亚稳态消除方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的多电压域上下电复位中时序亚稳态消除方法,其特征在于,通过预复位电路进行各个电压域之间的衔接控制,使目标芯片在不同电源先后上电顺序条件下都能够正常工作。

3.根据权利要求2所述的多电压域上下电复位中时序亚稳态消除方法,其特征在于,所述预复位电路包括第一反相器、第二反相器和下拉电阻,所述第一反相器的信号输入端电连接所述两级触发同步器的信号输出端,所述第一反相器的信号输出端电连接所述下拉电阻的第一端和所述第二反相器的信号输入端,所述下拉电阻的第二端接地,所述第二反相器的信号输出端电连接待复位器件的信号输入端。

4.根据权利要求1-3任一项所述的多电压域上下电复位中时序亚稳态消除方法,其特征在于,所述两级触发同步器能够替换为多级触发同步器。

5.一种多电压域上下电复位中时序亚稳态消除装置,其特征在于,包括上电复位电路、分频采样电路、预处理电路、延迟电路和两级触发同步器,所述上电复位电路、分频采样电路、预处理电路和两级触发同步器依次电连接,所述延迟电路电连接所述上电复位电路和两级触发同步器;所述上电复位电路用于产生复位,所述分频采样电路被配置为在复位时对振荡器输出信号进行计时生成第一时钟信号,并通过所述延迟电路生成第二时钟信号;所述预处理电路被配置为对所述第一时钟信号进行预处理并采样生成第一复位信号;所述两级触发同步器被配置为基于所述第一复位信号和所述第二时钟信号进行同步处理生成第二复位信号,控制目标芯片进行上电复位。

6.根据权利要求5所述的多电压域上下电复位中时序亚稳态消除装置,其特征在于,还包括预复位电路,所述预复位电路电连接所述两级触发同步器,所述预复位电路被配置为进行各个电压域之间的衔接控制,使目标芯片在不同电源先后上电顺序条件下都能够正常工作。

7.根据权利要求6所述的多电压域上下电复位中时序亚稳态消除装置,其特征在于,所述预复位电路包括第一反相器、第二反相器和下拉电阻,所述第一反相器的信号输入端电连接所述两级触发同步器的信号输出端,所述第一反相器的信号输出端电连接所述下拉电阻的第一端和所述第二反相器的信号输入端,所述下拉电阻的第二端接地,所述第二反相器的信号输出端电连接待复位器件的信号输入端。

8.根据权利要求5-7任一项所述的多电压域上下电复位中时序亚稳态消除装置,其特征在于,所述两级触发同步器能够替换为多级触发同步器。

技术总结

本发明公开了一种多电压域上下电复位中时序亚稳态消除方法及装置,其中方法包括以下步骤:目标芯片上电时,通过上电复位电路产生复位,同时通过分频采样电路对振荡器输出信号进行计时,生成第一时钟信号,并基于预设延迟生成第二时钟信号;对第一时钟信号进行预处理并采样,生成第一复位信号;基于第一复位信号和第二时钟信号,通过两级触发同步器进行同步处理生成第二复位信号,控制目标芯片进行上电复位。本发明可解决复杂功能芯片的多电压域应用中上电复位时序产生亚稳态或毛刺的问题,应用脉冲信号计数对上电复位电路进行分段延迟处理,仅在分频后拍数少的情况下产生足够的延迟,以保护芯片内不同模块依次上电复位而不受到状态干扰。

技术研发人员:蹇俊杰,唐梓豪,李蓝

受保护的技术使用者:成都电科星拓科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!