具有占空比校正器的正交时钟生成器的制作方法

本公开总体上涉及用于数字时钟生成的电路和技术,并且更具体地涉及正交时钟信号的生成。

背景技术:

1、电子设备通常采用时钟信号来进行定时和同步。例如,正交时钟可以包括同相时钟信号和正交相位时钟信号,其中正交相位时钟信号具有与同相时钟信号相同的频率和幅度,但是相位偏移了四分之一波长,换句话说,偏移了90°或π/2弧度。

2、用于生成这种正交时钟信号的电路可以被配置为对于同相和正交相位时钟信号中的每一个维持适当的占空比、幅度和频率,以及维持同相时钟信号和正交相位时钟信号之间的四分之一波长相位差。

技术实现思路

1、提供本

技术实现要素:

是为了以简化的形式介绍下面在详细描述中进一步描述的概念的选择。本发明内容不旨在标识所要求保护的主题的关键特征或必要特征,也不旨在限制所要求保护的主题的范围。

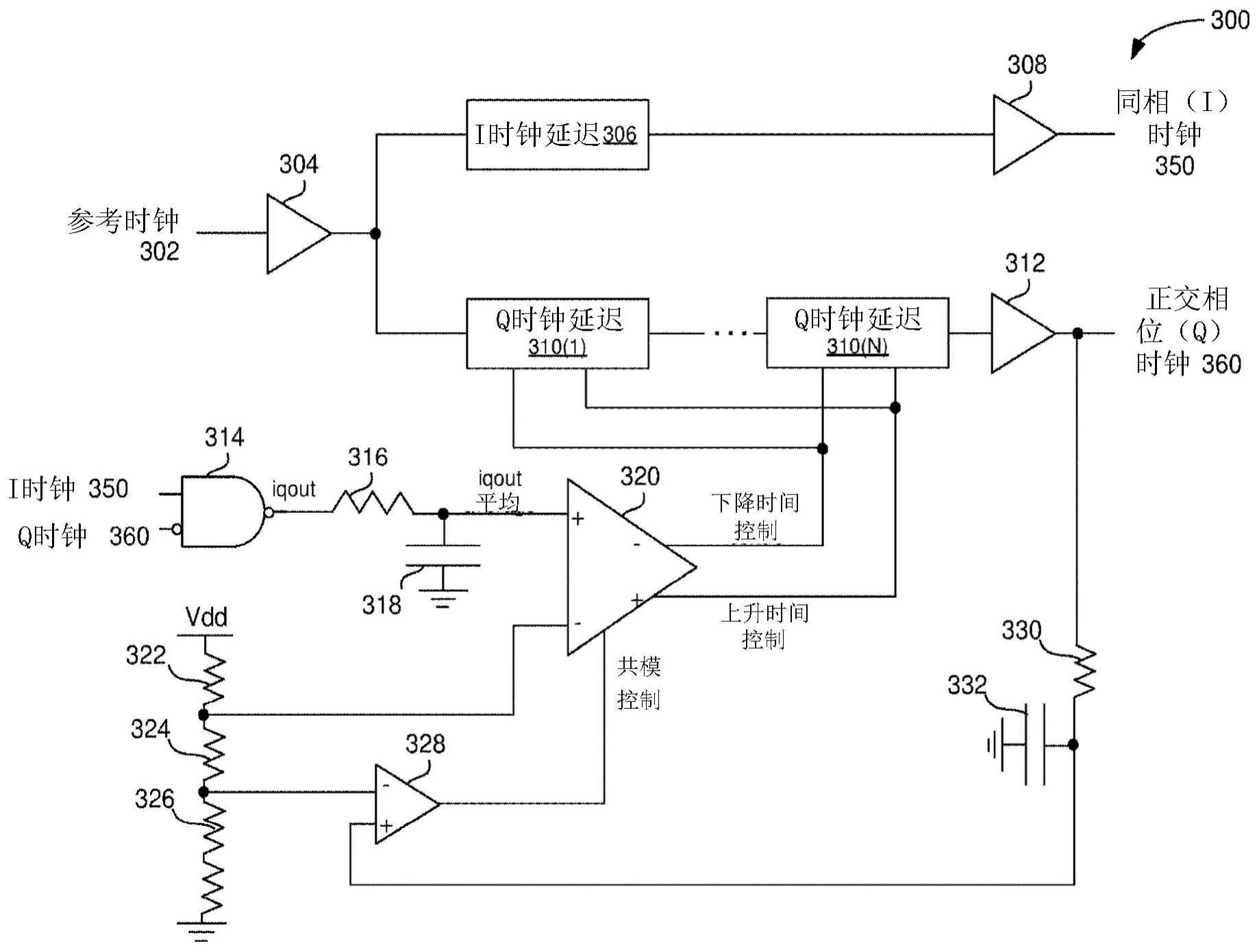

2、在本公开的一些方面中,公开了用于正交时钟生成的电路和技术。示例正交时钟生成器包括:同相(i)时钟生成电路,用于基于参考时钟信号生成i时钟信号,所述i时钟信号和所述参考时钟信号各自具有第一频率;正交相位(q)时钟生成电路,用于基于所述参考时钟信号、上升时间控制信号和下降时间控制信号生成q时钟信号,所述q时钟信号具有所述第一频率;以及控制电路,用于基于所述i时钟信号和所述q时钟信号生成所述上升时间控制信号和所述下降时间控制信号。

3、在本公开的其它方面中,公开了用于正交时钟生成的其它电路和技术。示例正交时钟生成器包括:同相(i)时钟生成电路,用于通过延迟参考时钟信号来生成i时钟信号,所述i时钟信号和所述参考时钟信号各自具有第一频率;正交相位(q)时钟生成电路,用于通过延迟和调整所述参考时钟信号的上升时间和下降时间来生成q时钟信号,所述q时钟信号具有所述第一频率并且相对于所述i时钟信号具有90°的相位偏移;以及控制电路,所述控制电路用于至少部分地基于所述i时钟信号和所述q时钟信号来确定用于调整所述q时钟信号的上升时间和下降时间的上升时间控制信号和下降时间控制信号。

4、在本公开的另外的方面中,公开了用于双轨正交时钟生成的电路和技术。示例双轨正交时钟生成器包括:同相(i)时钟生成电路,用于基于非反相参考时钟信号和反相参考时钟信号来生成非反相i时钟信号和反相i时钟信号,所述非反相i时钟信号、所述反相i时钟信号、所述非反相参考时钟信号和所述反相参考时钟信号各自具有第一频率;正交相位q时钟生成电路,其用于基于所述非反相参考时钟信号、所述反相参考时钟信号、所述非反相i时钟信号和所述反相q时钟信号生成非反相q时钟信号和反相q时钟信号,其中所述非反相q时钟信号和所述反相q时钟信号具有所述第一频率;以及控制电路,所述控制电路用于生成用于调整所述非反相q时钟信号和所述反相q时钟信号的上升时间和下降时间的上升时间控制信号和下降时间控制信号,其中所述上升时间控制信号和所述下降时间控制信号是基于所述非反相i时钟信号和所述反相q时钟信号生成的。

技术特征:

1.一种正交时钟生成器,包括:

2.根据权利要求1所述的正交时钟生成器,其中所述i时钟生成电路包括被配置为延迟所述参考时钟信号的延迟电路。

3.根据权利要求1所述的正交时钟生成器,其中所述q时钟生成电路包括多个q时钟延迟单元,每个q时钟延迟单元耦合到所述上升时间控制信号和所述下降时间控制信号。

4.根据权利要求3所述的正交时钟生成器,其中每个q时钟延迟单元包括:

5.根据权利要求1所述的正交时钟生成器,其中所述控制电路包括差分放大器,所述差分放大器包括:

6.根据权利要求5所述的正交时钟生成器,其中所述共模信号由放大器生成,所述放大器具有用于接收表示所述电源电压的50%的恒定电压信号的反相输入、用于接收表示所述q时钟信号的平均值的信号的非反相输入、以及用于提供所述输出共模电压信号的输出端子。

7.根据权利要求1所述的正交时钟生成器,其中所述控制电路被进一步配置为至少部分地基于所述q时钟信号的占空比与所述正交时钟生成器的电源电压的50%之间的差来确定所述上升时间控制信号和所述下降时间控制信号。

8.一种正交时钟生成器,包括:

9.根据权利要求8所述的正交时钟生成器,其中所述q时钟生成电路包括多个q时钟延迟单元,每个q时钟延迟单元耦合到所述上升时间控制信号和所述下降时间控制信号。

10.根据权利要求8所述的正交时钟生成器,其中当所述上升时间控制信号增大时,所述上升时间延迟增大,并且当所述上升时间控制信号减小时,所述上升时间延迟减小。

11.根据权利要求8所述的正交时钟生成器,其中当所述下降时间控制信号增大时,所述下降时间延迟减小,并且当所述下降时间控制信号减小时,所述下降时间延迟增大。

12.根据权利要求8所述的正交时钟生成器,其中所述控制电路被配置为至少部分地基于所述i时钟信号与所述q时钟信号之间的所述相位偏移来确定所述上升时间控制信号和所述下降时间控制信号。

13.根据权利要求8所述的正交时钟生成器,其中所述控制电路被配置为基于所述i时钟信号与反相q时钟信号之间的逻辑与非来确定所述i时钟信号与所述q时钟信号之间的所述相位偏移。

14.根据权利要求8所述的正交时钟生成器,其中所述控制电路被进一步配置为至少部分地基于所述q时钟信号的占空比与所述正交时钟生成器的电源电压的50%之间的差来确定所述上升时间控制信号和所述下降时间控制信号。

15.一种双轨正交时钟生成器,包括:

16.根据权利要求15所述的双轨正交时钟生成器,其中所述i时钟生成电路包括第一i延迟电路和第二i延迟电路,所述第一i延迟电路被配置为延迟所述非反相参考时钟信号以生成所述非反相i时钟信号,所述第二i延迟电路被配置为延迟所述反相参考时钟信号以生成所述反相i时钟信号。

17.根据权利要求15所述的双轨正交时钟生成器,其中所述q时钟生成电路包括:

18.根据权利要求17所述的双轨正交时钟生成器,其中每个第一q时钟延迟单元和每个第二q时钟延迟单元包括:

19.根据权利要求15所述的双轨正交时钟生成器,其中所述控制电路包括差分放大器,所述差分放大器包括:

20.根据权利要求19所述的双轨正交时钟生成器,其中所述输出共模电压信号由放大器生成,所述放大器具有用于接收表示所述电源电压的50%的恒定电压信号的反相输入、用于接收表示所述q时钟信号的平均值的信号的非反相输入、以及用于提供所述输出共模电压信号的输出端子。

技术总结

公开了正交时钟生成电路和技术。示例正交时钟生成器包括:同相(I)时钟生成电路,用于基于参考时钟信号生成I时钟信号,所述I时钟信号和所述参考时钟信号各自具有第一频率;正交相位(Q)时钟生成电路,用于基于所述参考时钟信号、上升时间控制信号和下降时间控制信号生成Q时钟信号,所述Q时钟信号具有所述第一频率;以及控制电路,用于基于所述I时钟信号和所述Q时钟信号生成所述上升时间控制信号和所述下降时间控制信号。

技术研发人员:C·S·R·艾雅,崔宰源

受保护的技术使用者:辛纳普蒂克斯公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!