半导体元件的制作方法

本申请案主张美国第17/824,010及17/824,487号专利申请案的优先权(即优先权日为“2022年5月25日”),其内容以全文引用的方式并入本文中。本公开是关于一种半导体元件,特别是关于一种包含具有突出部的字元线的半导体元件。

背景技术:

1、随着电子工业的快速成长,集成电路(ic)的发展已经实现了高性能及小型化。ic材料及设计的技术进步产生了几世代的ic,每一世代的电路都比上一世代更小、更复杂。

2、动态随机存取存储器(dram)元件为一种随机存取存储器,其将数据的每一位元存储于集成电路内各别的电容中。通常,dram排列成每个单元一个电容及晶体管的方形阵列。已开发出用于4f2的dram单元的一种垂直晶体管,其中f代表光微影最小特征宽度或临界尺寸(cd)。然而,近来,随着字元线间距持续缩小,dram制造商面临着缩小存储器单元面积的巨大挑战。例如,位元线的通道容易与字元线接触,进而造成因光微影制程的覆盖误差而导致短路。

3、上文的“先前技术”说明仅是提供背景技术,并未承认上文的“先前技术”说明揭示本公开的标的,不构成本公开的先前技术,且上文的“先前技术”的任何说明均不应作为本案的“先前技术”的任一部分,不构成本公开的先前技术。

技术实现思路

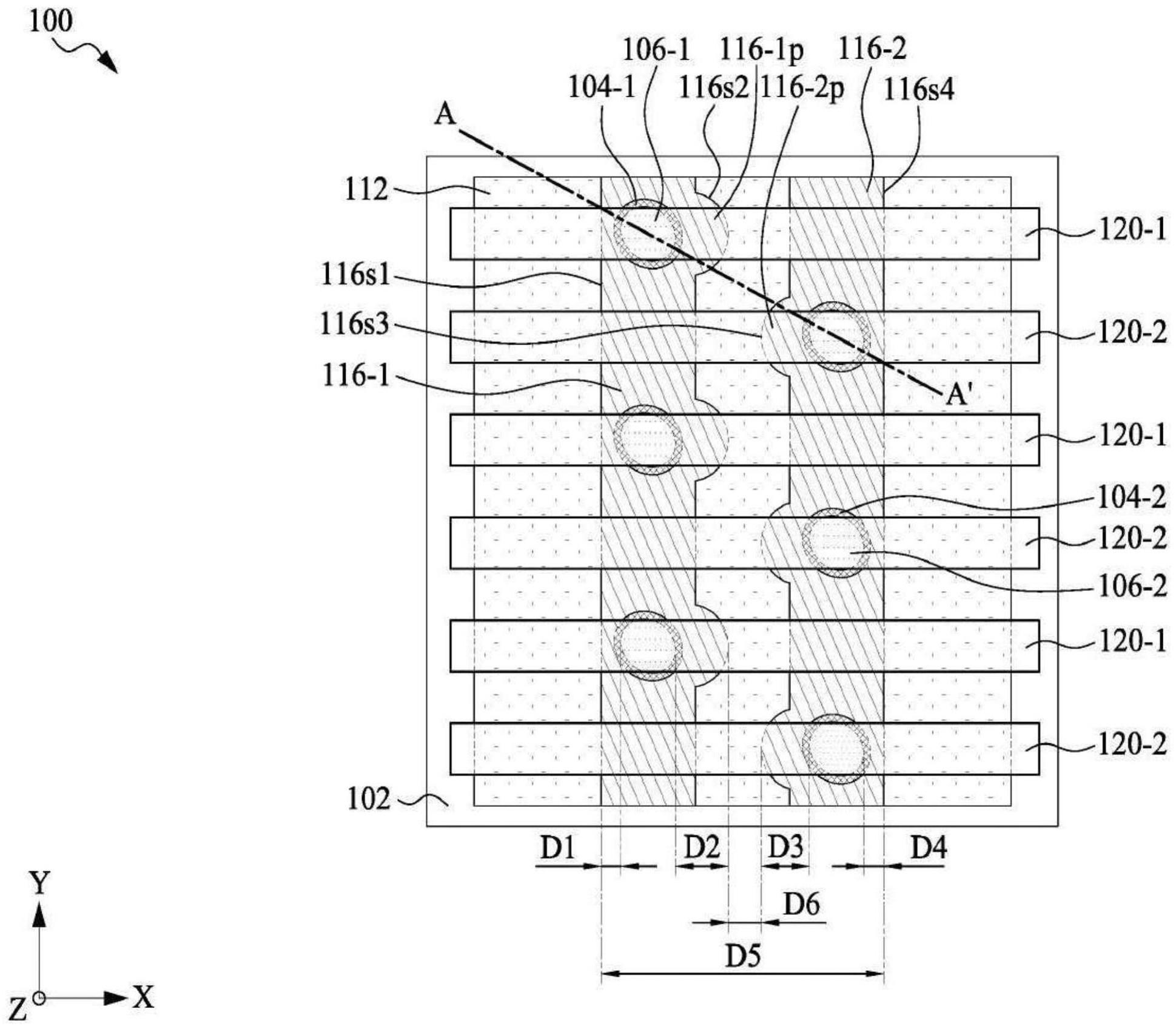

1、本公开的一方面提供一种半导体元件,该半导体元件包含一基板、一介电层、一第一金属化层、一第一通道层、一第二金属化层及一第二通道层。该介电层设置于该基板上,该第一金属化层设置于该介电层内且沿着一第一方向延伸,该第一通道层被该第一金属化层环绕,该第二金属化层设置于该介电层内且沿着该第一方向延伸,该第二通道层被该第二金属化层环绕,其中该第一金属化层包含朝向该第二金属化层突出的一第一突出部。

2、本公开的另一方面提供另一种半导体元件,该半导体元件包含一底部基板、一第一底部单元、一顶部基板、一第一顶部单元及一共享位元线。该第一底部单元包括设置于该底部基板内的一第一底部电容,该第一底部单元也包含设置在该底部基板上并沿着一第一方向延伸的一第一底部字元线,该第一底部单元还包括被该第一底部字元线环绕的一第一底部通道层。该第一顶部单元包括设置于该顶部基板内的一第一顶部电容,该第一顶部单元也包含设置在该顶部基板上并沿着该第一方向延伸的一第一顶部字元线,该第一顶部单元还包括被该第一顶部字元线环绕的一第一顶部通道层。该共享位元线设置于该第一底部单元和该第一顶部单元之间,并沿着大致上垂直于该第一方向的一第二方向延伸。

3、本公开的另一方面提供一种半导体元件的制造方法,该方法包含提供一基板。该方法也包含在该基板上形成一导电层。该方法还包含图案化该导电层以形成沿着一第一方向延伸的一第一金属化层及一第二金属化层,其中该第一金属化层包含朝向该第二金属化层突出的一第一突出部。另外,该方法包含在该第一金属化层内形成一第一通道层,且在该第二金属化层内形成一第二通道层。

4、在一些实施例中,该第一通道层及该第二通道层的形成包括:在该第一金属化层内形成一第一开口且在该第二金属化层内形成一第二开口,其中该第一开口沿着大致上垂直于该第一方向的一第二方向与该第一突出部重叠;以及在该第一开口内形成该第一通道层,且在该第二开口内形成该第二通道层。

5、在一些实施例中,该第一开口沿着该第二方向与该第二开口错位。

6、在一些实施例中,该导电层的图案化还包括形成该第二金属化层的一第二突出部分,且该第二突出部朝向该第一金属化层突出。

7、在一些实施例中,该第一通道层沿着大致上垂直于该第一方向的一第二方向与该第一突出部重叠。

8、在一些实施例中,该第二通道层沿着该第二方向与该第二突出部重叠。

9、在一些实施例中,该第一通道层沿着该第二方向与该第二通道层错位。

10、在一些实施例中,该第一金属化层具有一第一侧壁及与该第一侧壁相对的一第二侧壁,该第二侧壁面向该第二金属化层,且该第一侧壁与该第一通道层之间的一第一距离不同于该第二侧壁与该第一通道层之间的一第二距离。

11、在一些实施例中,该第二距离大于该第一距离。

12、在一些实施例中,该第二金属化层具有一第三侧壁及一第四侧壁,该第三侧壁面向该第一金属化层,且该第三侧壁与该第二通道层之间的一第三距离不同于该第四侧壁与该第二通道层之间的一第四距离。

13、在一些实施例中,该第三距离大于该第四距离。

14、在一些实施例中,该第一金属化层的该第一侧壁与该第二金属化层的该第四侧壁之间的一第五距离沿着该第一方向为一致的。

15、在一些实施例中,该第一金属化层的该第二侧壁与该第二金属化层的该第三侧壁之间的一第六距离沿着该第一方向变化。

16、本公开的实施例提供一种半导体元件,半导体元件可包含具有突出部的字元线。突出部可允许将字元线图案化以形成其中形成通道层的开口时相对较大的重叠误差,其可防止字元线与通道层之间的漏电流。

17、上文已相当广泛地概述本公开的特征及技术优点,使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其他特征和优点将描述于下文。本公开所属技术领域中具有通常知识者应了解,可相当容易地利用下文揭示的概念与特定实施例作为修改或设计其他结构或制程而实现与本公开相同的目的。本公开所属技术领域中具有通常知识者亦应了解,这类等效建构无法脱离后附的权利要求所界定的本公开的精神和范围。

技术特征:

1.一种半导体元件,包括:

2.如权利要求1所述的半导体元件,其中该第二金属化层包括朝向该第一金属化层突出的一第二突出部。

3.如权利要求2所述的半导体元件,其中该第一突出部沿着大致上垂直于该第一方向的一第二方向与该第二突出部错位。

4.如权利要求2所述的半导体元件,其中该第一通道层沿着大致上垂直于该第一方向的一第二方向与该第一突出部重叠。

5.如权利要求4所述的半导体元件,其中该第二通道层沿着该第二方向与该第二突出部重叠。

6.如权利要求5所述的半导体元件,其中该第一通道层沿着该第二方向与该第二通道层错位。

7.如权利要求1所述的半导体元件,其中该第一金属化层具有一第一侧壁及与该第一侧壁相对的一第二侧壁,该第二侧壁面向该第二金属化层,且该第一侧壁与该第一通道层之间的一第一距离不同于该第二侧壁与该第一通道层之间的一第二距离。

8.如权利要求7所述的半导体元件,其中该第二距离大于该第一距离。

9.如权利要求7所述的半导体元件,其中该第二金属化层具有一第三侧壁及一第四侧壁,该第三侧壁面向该第一金属化层,且该第三侧壁与该第二通道层之间的一第三距离不同于该第四侧壁与该第二通道层之间的一第四距离。

10.如权利要求9所述的半导体元件,其中该第三距离大于该第四距离。

11.如权利要求9所述的半导体元件,其中该第一金属化层的该第一侧壁与该第二金属化层的该第四侧壁之间的一第五距离沿着该第一方向为一致的。

12.如权利要求9所述的半导体元件,其中该第一金属化层的该第二侧壁与该第二金属化层的该第三侧壁之间的一第六距离沿着该第一方向变化。

技术总结

本公开提供一种半导体元件。该半导体元件包含一基板、一介电层、一第一金属化层、一第一通道层、一第二金属化层及一第二通道层。该介电层设置于该基板上,该第一金属化层设置于该介电层内且沿着一第一方向延伸,该第一通道层被该第一金属化层环绕,该第二金属化层设置于该介电层内且沿着该第一方向延伸,该第二通道层被该第二金属化层环绕,其中该第一金属化层包含朝向该第二金属化层突出的一第一突出部。

技术研发人员:郭锦德

受保护的技术使用者:南亚科技股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!