本公开的各种实施方式总体涉及一种半导体存储器装置和制造该半导体存储器装置的方法,更具体地,涉及一种三维(3d)半导体存储器装置和制造该3d半导体存储器装置的方法。

背景技术:

1、半导体存储器装置包括能够存储数据的存储器单元。三维(3d)半导体存储器装置可以包括3d存储器单元阵列。

2、为了提高3d存储器单元阵列的集成度,可以增加存储器单元叠层的数量。随着存储器单元叠层的数量增加,可能更容易发生图案之间的未对准,并且操作可靠性可能劣化。

技术实现思路

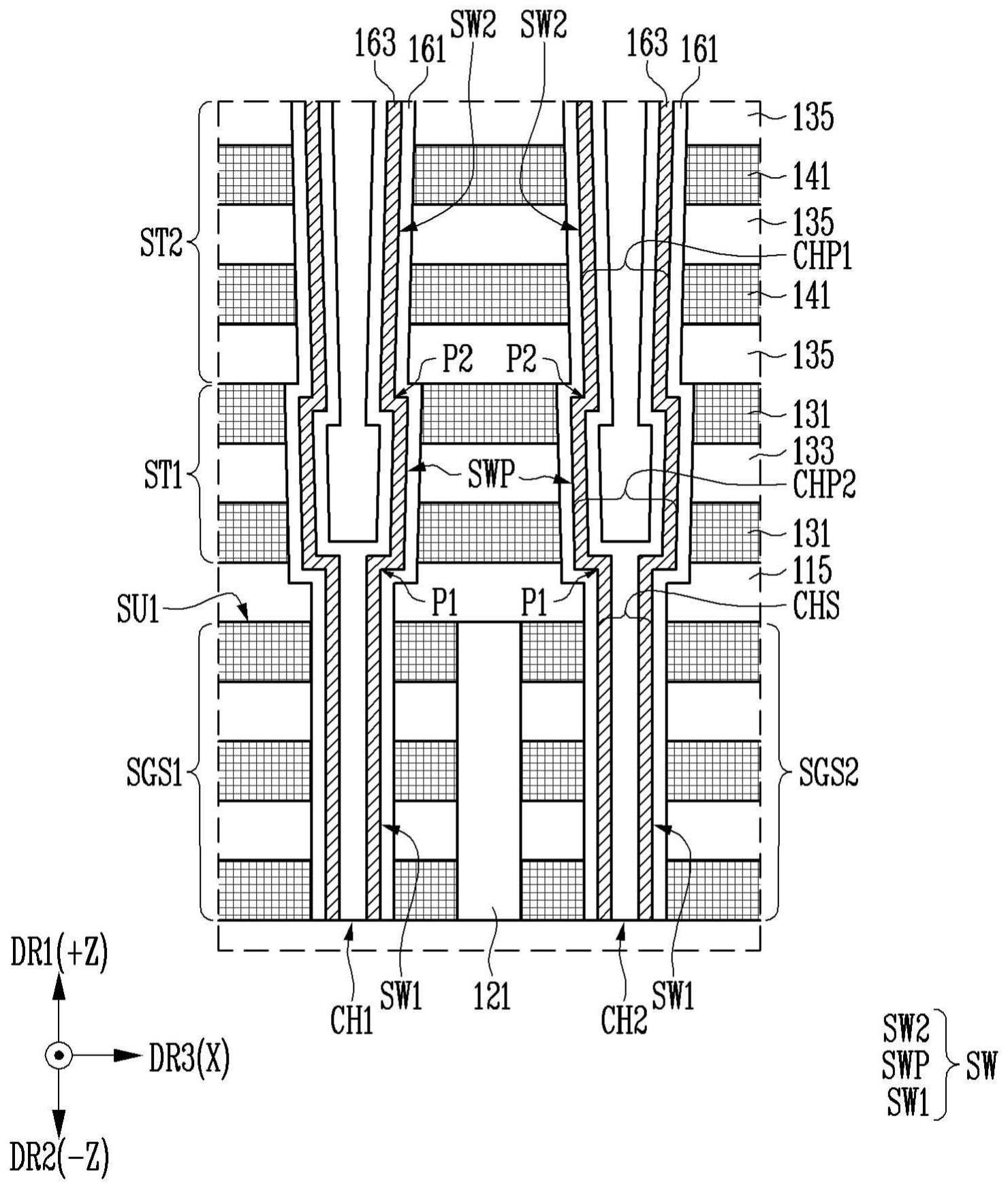

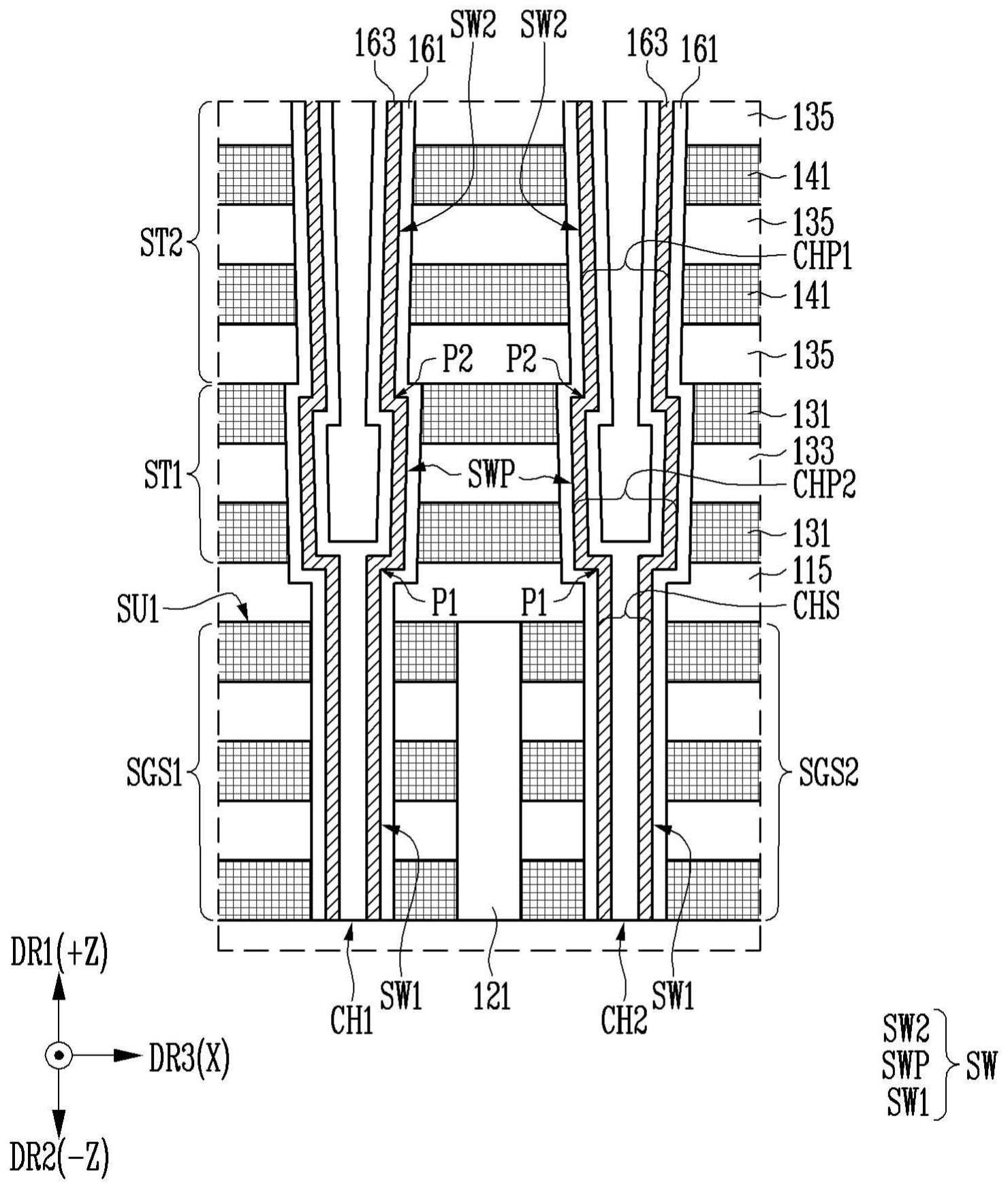

1、本公开的一个实施方式可以提供一种半导体存储器装置。该半导体存储器装置可以包括:第一选择栅极结构,其包括面向第一方向的第一表面和面向与第一方向相反的第二方向的第二表面,第一表面和第二表面沿第三方向延伸;第二选择栅极结构,其沿第三方向与第一选择栅极结构相邻;子块绝缘层,其插置在第一选择栅极结构和第二选择栅极结构之间;多个导电图案,其层叠在第一选择栅极结构的第一表面上,以沿第一方向彼此间隔开,并且沿第三方向延伸以与子块绝缘层和第二选择栅极结构交叠;第一沟道结构,其穿透第一选择栅极结构和多个导电图案;以及第二沟道结构,其穿透第二选择栅极结构和多个导电图案,其中,第一沟道结构和第二沟道结构中的每一个的侧壁包括第一拐点,该第一拐点设置在位于多个导电图案和子块绝缘层之间的高度处。

2、本公开的一个实施方式可以提供一种半导体存储器装置。该半导体存储器装置可以包括:水平掺杂半导体图案;第一沟道结构和第二沟道结构,二者接触水平掺杂半导体图案并且沿第一方向延伸;子块结构,其包括围绕第一沟道结构的第一选择栅极结构、围绕第二沟道结构的第二选择栅极结构以及设置在第一选择栅极结构和第二选择栅极结构之间的子块绝缘层;第一层叠体,其包括交替层叠在子块结构上的第一导电图案和第一层间绝缘层;以及第二层叠体,其包括交替层叠在第一层叠体上的第二导电图案和第二层间绝缘层,其中,第一沟道结构和第二沟道结构中的每一个的侧壁包括第一拐点,该第一拐点设置在位于第一层叠体和子块绝缘层之间的高度处。

3、本公开的一个实施方式可以提供一种制造半导体存储器装置的方法。该方法可以包括:形成初步选择结构;形成穿过初步选择结构的子狭缝;在子狭缝中形成子块绝缘层;在初步选择结构和子块绝缘层上形成第一初步层叠体;在第一初步层叠体上形成第二初步层叠体;在子狭缝的两侧形成穿过初步选择结构、第一初步层叠体和第二初步层叠体的第一沟道孔和第二沟道孔,其中,第一沟道孔和第二沟道孔中的每一个包括第一拐点,第一拐点位于在第一初步层叠体和子块绝缘层之间的高度处;分别在第一沟道孔和第二沟道孔中形成第一沟道结构和第二沟道结构;以及形成穿过初步选择结构、第一初步层叠体和第二初步层叠体的狭缝。

技术特征:1.一种半导体存储器装置,所述半导体存储器装置包括:

2.根据权利要求1所述的半导体存储器装置,其中,所述第一沟道结构和所述第二沟道结构中的每一个的所述侧壁还包括:

3.根据权利要求2所述的半导体存储器装置,其中,所述第一沟道结构和所述第二沟道结构中的每一个的所述侧壁还包括:

4.根据权利要求2所述的半导体存储器装置,其中,所述多个导电图案包括:

5.根据权利要求4所述的半导体存储器装置,其中,所述第一沟道结构和所述第二沟道结构中的每一个包括:

6.根据权利要求5所述的半导体存储器装置,其中,所述选择沟道组件被形成为比所述第二沟道组件和所述第一沟道组件中的每一个更窄。

7.根据权利要求1所述的半导体存储器装置,其中,所述第一沟道结构和所述第二沟道结构中的每一个包括:

8.根据权利要求7所述的半导体存储器装置,所述半导体存储器装置还包括:

9.一种半导体存储器装置,所述半导体存储器装置包括:

10.根据权利要求9所述的半导体存储器装置,其中,所述第一沟道结构和所述第二沟道结构中的每一个包括:

11.根据权利要求10所述的半导体存储器装置,其中,

12.根据权利要求10所述的半导体存储器装置,其中,所述沟道层包括管沟道组件,所述管沟道组件延伸以围绕所述水平掺杂半导体图案的侧壁、顶表面和底表面。

13.根据权利要求12所述的半导体存储器装置,其中,所述水平掺杂半导体图案和所述管沟道组件中的每一个包括n型杂质。

14.根据权利要求12所述的半导体存储器装置,其中,所述水平掺杂半导体图案和所述管沟道组件中的每一个包括p型杂质。

15.根据权利要求14所述的半导体存储器装置,所述半导体存储器装置还包括:

16.根据权利要求15所述的半导体存储器装置,其中,所述水平掺杂半导体图案、所述管沟道组件和所述垂直半导体图案的与所述源极接触结构相邻的相应部分包括n型杂质。

17.根据权利要求12所述的半导体存储器装置,所述半导体存储器装置还包括:

18.根据权利要求17所述的半导体存储器装置,所述半导体存储器装置还包括:

19.根据权利要求17所述的半导体存储器装置,所述半导体存储器装置还包括:

20.根据权利要求10所述的半导体存储器装置,其中,

21.一种制造半导体存储器装置的方法,所述方法包括以下步骤:

22.根据权利要求21所述的方法,其中,所述第一沟道孔和所述第二沟道孔中的每一个还包括比所述第一拐点更远离所述初步选择结构的第二拐点。

23.根据权利要求21所述的方法,其中,形成所述第一沟道孔和所述第二沟道孔的步骤包括以下步骤:

24.根据权利要求23所述的方法,其中,形成所述第一沟道孔和所述第二沟道孔的步骤还包括以下步骤:

25.根据权利要求21所述的方法,其中,

26.根据权利要求21所述的方法,其中,

27.根据权利要求26所述的方法,其中,形成所述第一沟道孔和所述第二沟道孔的步骤包括以下步骤:

28.根据权利要求27所述的方法,其中,形成所述第一沟道孔和所述第二沟道孔的步骤还包括以下步骤:

29.根据权利要求28所述的方法,所述方法还包括以下步骤:

30.根据权利要求29所述的方法,其中,形成所述第一沟道结构和所述第二沟道结构的步骤包括以下步骤:

31.根据权利要求30所述的方法,所述方法还包括以下步骤:

32.根据权利要求30所述的方法,所述方法还包括以下步骤:

33.根据权利要求32所述的方法,其中,

34.根据权利要求21所述的方法,其中,

35.根据权利要求34所述的方法,所述方法还包括以下步骤:

36.根据权利要求35所述的方法,其中,形成所述第一沟道结构和所述第二沟道结构的步骤包括以下步骤:

37.根据权利要求36所述的方法,所述方法还包括以下步骤:

技术总结本文可以提供一种半导体存储器装置和制造该半导体存储器装置的方法。该半导体存储器装置可以包括:子块绝缘层,其插置在第一选择栅极结构和第二选择栅极结构之间;多个导电图案,其层叠在第一选择栅极结构和第二选择栅极结构上以彼此间隔开;以及沟道结构,其穿透第一选择栅极结构和第二选择栅极结构中的一个以及多个导电图案,该沟道结构包括位于在子块绝缘层和多个导电图案之间的高度处的拐点。

技术研发人员:崔康植

受保护的技术使用者:爱思开海力士有限公司

技术研发日:技术公布日:2024/1/15