应用于ADCIP核的数据转换方法、系统、终端及存储介质与流程

本发明涉及数据处理,尤其涉及应用于adc ip核的数据转换方法、系统、终端及存储介质。

背景技术:

1、adc:模数转换器,通常是指一个将模拟信号转变为数字信号的电子元件。通常的模数转换器是把经过与标准量比较处理后的模拟量转换成以二进制数值表示的离散信号的转换器。

2、ip核:知识产权核(intellectual property core),是指某一方提供的,形式为逻辑单元、芯片设计的可重用模块。

3、verilog:verilog是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

4、现有技术在进行adc数据转换过程中,会因为干扰,电压波动等情况出现模拟数值异常波动、尖刺等现象,为了解决该技术问题现提出应用于adc ip核的数据转换方法、系统、终端及存储介质。

技术实现思路

1、为了解决上述现有技术中存在的技术问题,本发明提供了一种应用于adc ip核的数据转换方法、系统、终端及存储介质,通过自主设计的verilog代码实现了提高数据转换准确性的功能,避免了adc ip因为模拟信号电涌、尖刺出现的数字数据转换突变,提高了数据的有效性和准确性,本方案结构清晰,灵活可靠,可重复利用。

2、为实现上述目的,本发明实施例提供了如下的技术方案:

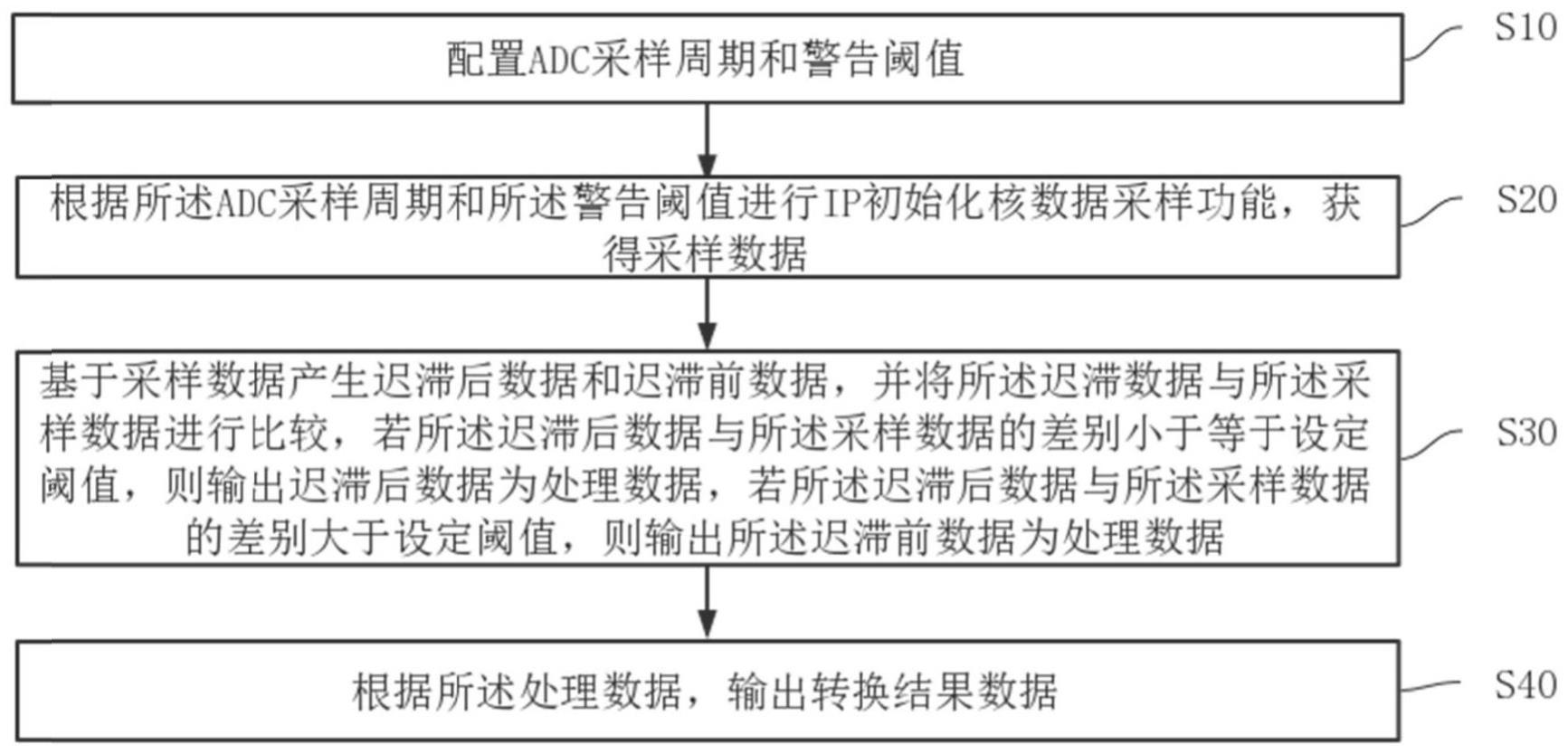

3、第一方面,在本发明提供的一个实施例中,提供了应用于adc ip核的数据转换方法,该方法包括以下步骤:

4、配置adc采样周期和警告阈值;

5、根据所述adc采样周期和所述警告阈值进行ip初始化核数据采样功能,获得采样数据;

6、基于采样数据产生迟滞后数据和迟滞前数据,并将所述迟滞数据与所述采样数据进行比较,若所述迟滞后数据与所述采样数据的差别小于等于设定阈值,则输出迟滞后数据为处理数据,若所述迟滞后数据与所述采样数据的差别大于设定阈值,则输出所述迟滞前数据为处理数据;

7、根据所述处理数据,输出转换结果数据。

8、作为本发明的进一步方案,所述迟滞后数据和迟滞前数据是通过两个反相器延迟不少于一个的时钟周期后得到。

9、作为本发明的进一步方案,所述adc采样周期和警告阈值储存在寄存器中。

10、作为本发明的进一步方案,所述寄存器包括数据寄存器、阈值配置寄存器、迟滞阈值配置寄存器、0x0c时钟控制器、数据寄存器和迟滞阈值配置寄存器。

11、作为本发明的进一步方案,所述寄存器配置包括:配置数据寄存器、阈值配置寄存器、迟滞阈值配置寄存器、0x0c时钟控制器、数据寄存器和迟滞阈值配置寄存器。

12、作为本发明的进一步方案,配置控制寄存器0x00:0x00的31:24,15:9,5:4位为reserved,23:16位为选择是否使能通道,23~16位分别对应channel 7~0,置1为使能,置0为跳过,可选择使能还是跳过;

13、位7:6为参考电压选择,根据需要选择00:2.5v,01:1.2v,10:外部电压,11:外部电压;

14、3:1位为工作模式选择,可配置000:断电模式,001:待机模式,111:正常模式;

15、位0为启用模块信号,配置时置0。

16、作为本发明的进一步方案,配置中断寄存器0x04:31:24,15:8位为保留位,23:16位分别配置chamnel 7~0的中断使能,置1为使能;7:0位为读取中断状态位,配置时需全写0清除。

17、第二方面,在本发明提供的又一个实施例中,提供了应用于adc ip核的数据转换方法系统,该系统包括:采用控制模块、寄存器、迟滞阈值模和adc ip模块;

18、所述采用控制模块,用于ip初始化核数据采样功能,获取采样数据;

19、所述寄存器,用于配置adc采样周期和警告阈值;

20、所述迟滞阈值模,用于根据采样数据产生迟滞后数据和迟滞前数据;

21、所述adc ip模块,用于将所述迟滞数据与所述采样数据进行比较,若所述迟滞后数据与所述采样数据的差别小于等于设定阈值,则输出迟滞后数据为处理数据,若所述迟滞后数据与所述采样数据的差别大于设定阈值,则输出所述迟滞前数据为处理数据,根据所述处理数据,输出转换结果数据。

22、第三方面,在本发明提供的又一个实施例中,提供了一种终端,包括存储器和处理器,所述存储器存储有计算机程序,所述处理器加载并执行所述计算机程序时实现应用于adc ip核的数据转换方法的步骤。

23、第四方面,在本发明提供的再一个实施例中,提供了一种存储介质,存储有计算机程序,所述计算机程序被处理器加载并执行时实现所述应用于adc ip核的数据转换方法的步骤。

24、本发明提供的技术方案,具有如下有益效果:

25、本发明提供的应用于adc ip核的数据转换方法、系统、终端及存储介质,提高数据转换准确性的功能,避免了adc ip因为模拟信号电涌、尖刺出现的数字数据转换突变,提高了数据的有效性和准确性,本方案结构清晰,灵活可靠,可重复利用。

26、本发明的这些方面或其他方面在以下实施例的描述中会更加简明易懂。应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本发明。

技术特征:

1.一种应用于adc ip核的数据转换方法,其特征在于,该方法包括:配置adc采样周期和警告阈值;

2.如权利要求1所述的应用于adc ip核的数据转换方法,其特征在于,所述迟滞后数据和迟滞前数据是通过两个反相器延迟不少于一个的时钟周期后得到。

3.如权利要求1所述的应用于adc ip核的数据转换方法,其特征在于,所述adc采样周期和警告阈值储存在寄存器中。

4.如权利要求3所述的应用于adc ip核的数据转换方法,其特征在于,所述寄存器包括数据寄存器、阈值配置寄存器、迟滞阈值配置寄存器、0x0c时钟控制器、数据寄存器和迟滞阈值配置寄存器。

5.如权利要求4所述的应用于adc ip核的数据转换方法,其特征在于,所述寄存器配置包括:配置数据寄存器、阈值配置寄存器、迟滞阈值配置寄存器、0x0c时钟控制器、数据寄存器和迟滞阈值配置寄存器。

6.如权利要求5所述的应用于adc ip核的数据转换方法,其特征在于,配置控制寄存器0x00:0x00的31:24,15:9,5:4位为reserved,23:16位为选择是否使能通道,23~16位分别对应channel 7~0,置1为使能,置0为跳过,可选择使能还是跳过;

7.如权利要求6所述的应用于adc ip核的数据转换方法,其特征在于,配置中断寄存器0x04:31:24,15:8位为保留位,23:16位分别配置chamnel 7~0的中断使能,置1为使能;7:0位为读取中断状态位,配置时需全写0清除。

8.一种应用于adc ip核的数据转换方法系统,其特征在于,该系统包括:采用控制模块、寄存器、迟滞阈值模和adc ip模块;

9.一种终端,包括存储器和处理器,所述存储器存储有计算机程序,所述处理器加载并执行所述计算机程序时实现如权利要求1-7任一项所述的应用于adc ip核的数据转换方法的步骤。

10.一种存储介质,存储有计算机程序,所述计算机程序被处理器加载并执行时实现如权利要求1-7任一项所述的应用于adc ip核的数据转换方法的步骤。

技术总结

本发明涉及数据处理技术领域,具体涉及应用于ADC IP核的数据转换方法、系统、终端及存储介质。该方法包括以下步骤:配置ADC采样周期和警告阈值;根据所述ADC采样周期和所述警告阈值进行IP初始化核数据采样功能,获得采样数据;基于采样数据产生迟滞后数据和迟滞前数据,并将所述迟滞数据与所述采样数据进行比较,若所述迟滞后数据与所述采样数据的差别小于等于设定阈值,则输出迟滞后数据为处理数据,若所述迟滞后数据与所述采样数据的差别大于设定阈值,则输出所述迟滞前数据为处理数据,本发明提高数据转换准确性的功能,避免了ADC IP因为模拟信号电涌、尖刺出现的数字数据转换突变,提高了数据的有效性和准确性。

技术研发人员:龙治宇

受保护的技术使用者:山东云海国创云计算装备产业创新中心有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!