逻辑门电路的制作方法

本申请涉及芯片存储器存储,特别是涉及一种逻辑门电路。

背景技术:

1、当前大数据时代,数据量的高速增长对芯片算力与能效提出了更高的要求,而传统存算分离的冯-诺伊曼架构限制了算力与能效的进一步提升。因此,亟需发展出基于新型非易失性存储器的新型存算架构。铁电存储器是利用铁电材料的极化翻转实现0/1存储的存储技术,其基本构成单元为铁电场效应晶体管(ferroelectric field effecttransistor,fefet)。图1是相关技术中铁电晶体管的结构示意图,如图1所示,铁电晶体管由栅极、沟道和衬底构成,沟道的两端分别设置有源极和漏极,栅极和沟道之间由上至下依次设置有铁电层和界面层。在栅极上施加正电压或负电压,且施加在铁电材料上的电压超过矫顽电压vc时,会导致铁电极化正向或负向翻转,铁电材料中的极化电荷会在沟道吸引电性相反的电荷,改变晶体管的阈值电压,铁电晶体管在进行编程和擦除时的极化状态如图1中的(a)、(b)所示。在对铁电晶体管进行编程或擦除操作后,通过改变铁电晶体管衬底的偏置电压vsub,可以调节铁电晶体管的阈值电压,从而做到逻辑门的切换。但是对逻辑门进行逻辑切换时,若想长时间保持某一逻辑功能,需要对铁电晶体管衬底长时间施加偏压,导致逻辑门电路工作能耗高。

2、针对相关技术中存在逻辑门电路工作能耗高的问题,目前还没有提出有效的解决方案。

技术实现思路

1、在本实施例中提供了一种逻辑门电路,以解决相关技术中逻辑门电路工作能耗高的问题。

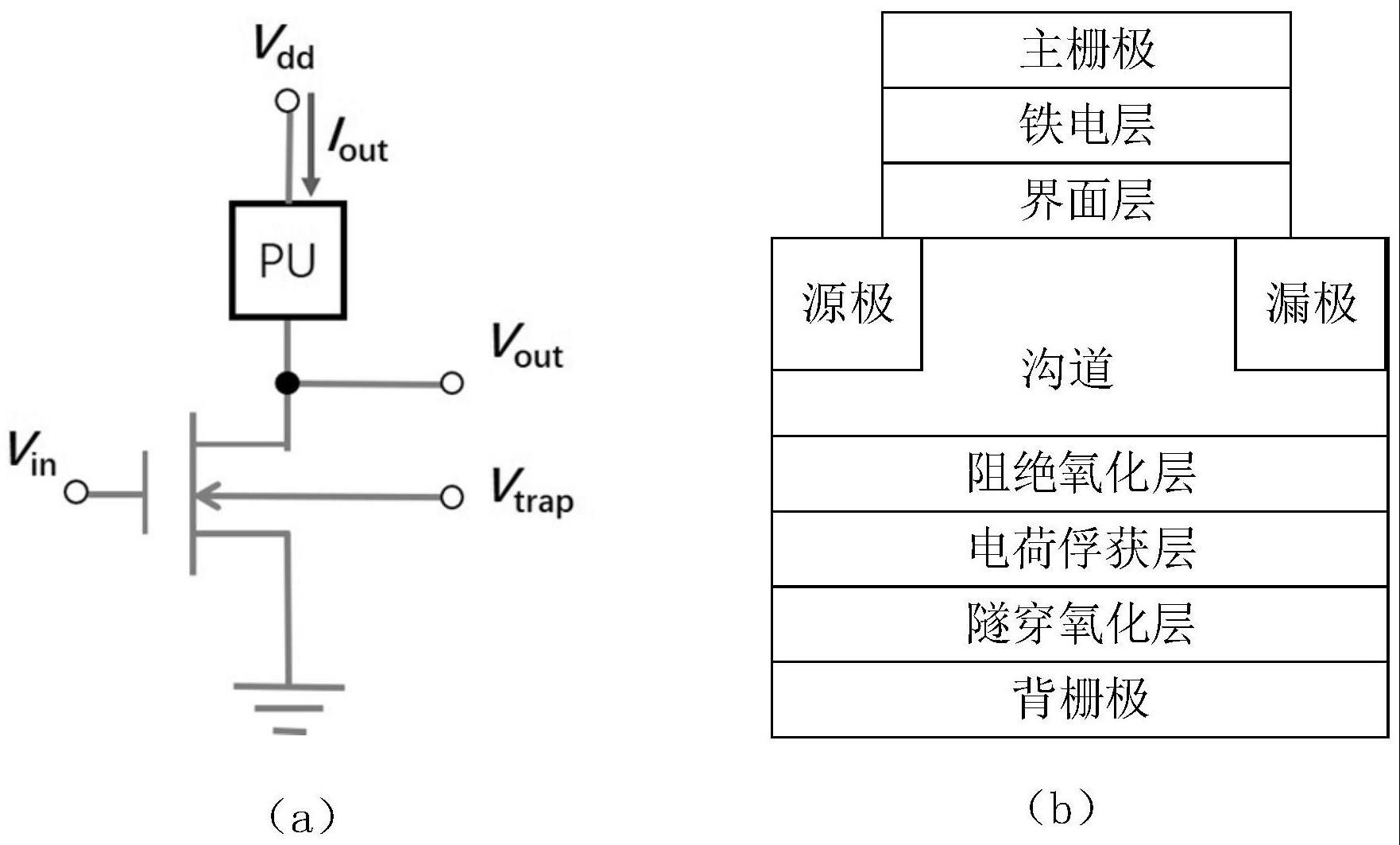

2、本实施例提供了一种逻辑门电路,包括:上拉电阻和铁电晶体管,所述铁电晶体管内部由上至下依次设置有主栅极、沟道和背栅极,其中,所述沟道的两端分别设置有源极和漏极,所述主栅极和所述沟道之间由上至下依次设置有铁电层和界面层,所述沟道和所述背栅极之间由上至下依次设置有阻绝氧化层、电荷俘获层和隧穿氧化层;所述上拉电阻与所述漏极连接。

3、在其中的一些实施例中,制成所述阻绝氧化层的材料包括al2o3,制成所述电荷俘获层的材料包括si3n4,制成所述隧穿氧化层的材料包括sio2。

4、在其中的一些实施例中,所述阻绝氧化层通过原子层沉积法生长一层al2o3形成;所述电荷俘获层通过化学气相沉积法生长一层si3n4形成;所述隧穿氧化层通过原子层沉积法生长一层sio2形成。

5、在其中的一些实施例中,制成所述铁电层的材料包括hfzrox,制成所述界面层的材料包括sio2。

6、在其中的一些实施例中,所述铁电层通过原子层沉积法生长一层hfzrox形成,所述界面层通过臭氧氧化法生长一层sio2形成。

7、在其中的一些实施例中,当所述铁电晶体管的电荷俘获层保持在电中性状态时,所述铁电晶体管构成第一逻辑门。

8、在其中的一些实施例中,当向所述铁电晶体管的背栅极施加第一预设电压时,所述铁电晶体管的电荷俘获层处于负电荷俘获态,所述铁电晶体管所实现的功能从第一逻辑门切换至第二逻辑门,且在撤去所述第一预设电压后,所述铁电晶体管保持所述第二逻辑门的功能。

9、在其中的一些实施例中,对于n型铁电晶体管,所述第一逻辑门为“与非”门,所述第二逻辑门为“或非”门;对于p型铁电晶体管,所述第一逻辑门为“或”门,所述第二逻辑门为“与”门。

10、在其中的一些实施例中,当向所述铁电晶体管的主栅极施加第二预设电压时,所述铁电晶体管发生铁电极化正向翻转,所述铁电晶体管的阈值电压变小。

11、在其中的一些实施例中,当向所述铁电晶体管的主栅极施加第三预设电压时,所述铁电晶体管发生铁电极化负向翻转,所述铁电晶体管的阈值电压变大。

12、与相关技术相比,在本实施例中提供的逻辑门电路,包括:上拉电阻和铁电晶体管,铁电晶体管内部由上至下依次设置有主栅极、沟道和背栅极,其中,沟道的两端分别设置有源极和漏极,主栅极和沟道之间由上至下依次设置有铁电层和界面层,沟道和背栅极之间由上至下依次设置有阻绝氧化层、电荷俘获层和隧穿氧化层;上拉电阻与漏极连接。通过本申请,解决了相关技术中逻辑门电路工作能耗高的问题,降低了逻辑门电路的工作能耗。

13、本申请的一个或多个实施例的细节在以下附图和描述中提出,以使本申请的其他特征、目的和优点更加简明易懂。

技术特征:

1.一种逻辑门电路,其特征在于,包括:上拉电阻和铁电晶体管,所述铁电晶体管内部由上至下依次设置有主栅极、沟道和背栅极,其中,所述沟道的两端分别设置有源极和漏极,所述主栅极和所述沟道之间由上至下依次设置有铁电层和界面层,所述沟道和所述背栅极之间由上至下依次设置有阻绝氧化层、电荷俘获层和隧穿氧化层;所述上拉电阻与所述漏极连接。

2.根据权利要求1所述的逻辑门电路,其特征在于,制成所述阻绝氧化层的材料包括al2o3,制成所述电荷俘获层的材料包括si3n4,制成所述隧穿氧化层的材料包括sio2。

3.根据权利要求2所述的逻辑门电路,其特征在于,所述阻绝氧化层通过原子层沉积法生长一层al2o3形成;所述电荷俘获层通过化学气相沉积法生长一层si3n4形成;所述隧穿氧化层通过原子层沉积法生长一层sio2形成。

4.根据权利要求1所述的逻辑门电路,其特征在于,制成所述铁电层的材料包括hfzrox,制成所述界面层的材料包括sio2。

5.根据权利要求4所述的逻辑门电路,其特征在于,所述铁电层通过原子层沉积法生长一层hfzrox形成,所述界面层通过臭氧氧化法生长一层sio2形成。

6.根据权利要求1所述的逻辑门电路,其特征在于,当所述铁电晶体管的电荷俘获层保持在电中性状态时,所述铁电晶体管构成第一逻辑门。

7.根据权利要求6所述的逻辑门电路,其特征在于,当向所述铁电晶体管的背栅极施加第一预设电压时,所述铁电晶体管的电荷俘获层处于负电荷俘获态,所述铁电晶体管所实现的功能从第一逻辑门切换至第二逻辑门,且在撤去所述第一预设电压后,所述铁电晶体管保持所述第二逻辑门的功能。

8.根据权利要求7所述的逻辑门电路,其特征在于,对于n型铁电晶体管,所述第一逻辑门为“与非”门,所述第二逻辑门为“或非”门;对于p型铁电晶体管,所述第一逻辑门为“或”门,所述第二逻辑门为“与”门。

9.根据权利要求6所述的逻辑门电路,其特征在于,当向所述铁电晶体管的主栅极施加第二预设电压时,所述铁电晶体管发生铁电极化正向翻转,所述铁电晶体管的阈值电压变小。

10.根据权利要求6所述的逻辑门电路,其特征在于,当向所述铁电晶体管的主栅极施加第三预设电压时,所述铁电晶体管发生铁电极化负向翻转,所述铁电晶体管的阈值电压变大。

技术总结

本申请涉及一种逻辑门电路,包括:上拉电阻和铁电晶体管,铁电晶体管内部由上至下依次设置有主栅极、沟道和背栅极,其中,沟道的两端分别设置有源极和漏极,主栅极和沟道之间由上至下依次设置有铁电层和界面层,沟道和背栅极之间由上至下依次设置有阻绝氧化层、电荷俘获层和隧穿氧化层;上拉电阻与漏极连接。通过本申请,解决了相关技术中逻辑门电路工作能耗高的问题,降低了逻辑门电路的工作能耗。

技术研发人员:许嘉诚,金成吉,顾佳妮,陈冰,刘欢,玉虓,韩根全

受保护的技术使用者:之江实验室

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!