一种使能电路

本发明属于模拟集成电路,具体涉及一种使能电路。

背景技术:

1、使能控制信号几乎在所有的芯片应用中都是至关重要的,通常芯片外部会给进一个使能信号,芯片内部的使能电路将此信号处理后用来控制芯片整体开始工作。而传统的使能电路通常只能简单的处理电平信号,即外部使能信号为高电平就控制芯片启动,使能信号为低就控制芯片关闭。而在某些应用中,芯片外部没有条件产生持续的电平使能信号,只能产生一个脉冲信号进行使能,因此传统的使能电路无法适应这类应用。另外如果只是简单的用触发器来对外部使能信号的上升沿(或下降沿)进行检测,那么又很难保证在电平使能的应用场景下,使能信号从有效电平跳为无效电平后系统能够正常关闭。综上所述,传统的使能电路,无法兼顾电平使能和脉冲使能两种应用场景,应用范围较窄。

技术实现思路

1、针对传统使能电路无法兼顾电平使能和脉冲使能两种应用场景,本发明提出了一种可兼顾两种使能形式的使能电路。通过先对使能信号的上升沿进行检测,直接控制芯片启动,与此同时对外部使能信号进行检测,若检测为电平信号,则使能信号无效后就关闭芯片;若检测为脉冲信号,则使能无效后仍保持芯片开启,直到检测到下一个使能信号的脉冲时再关闭芯片。

2、本发明的技术方案为:

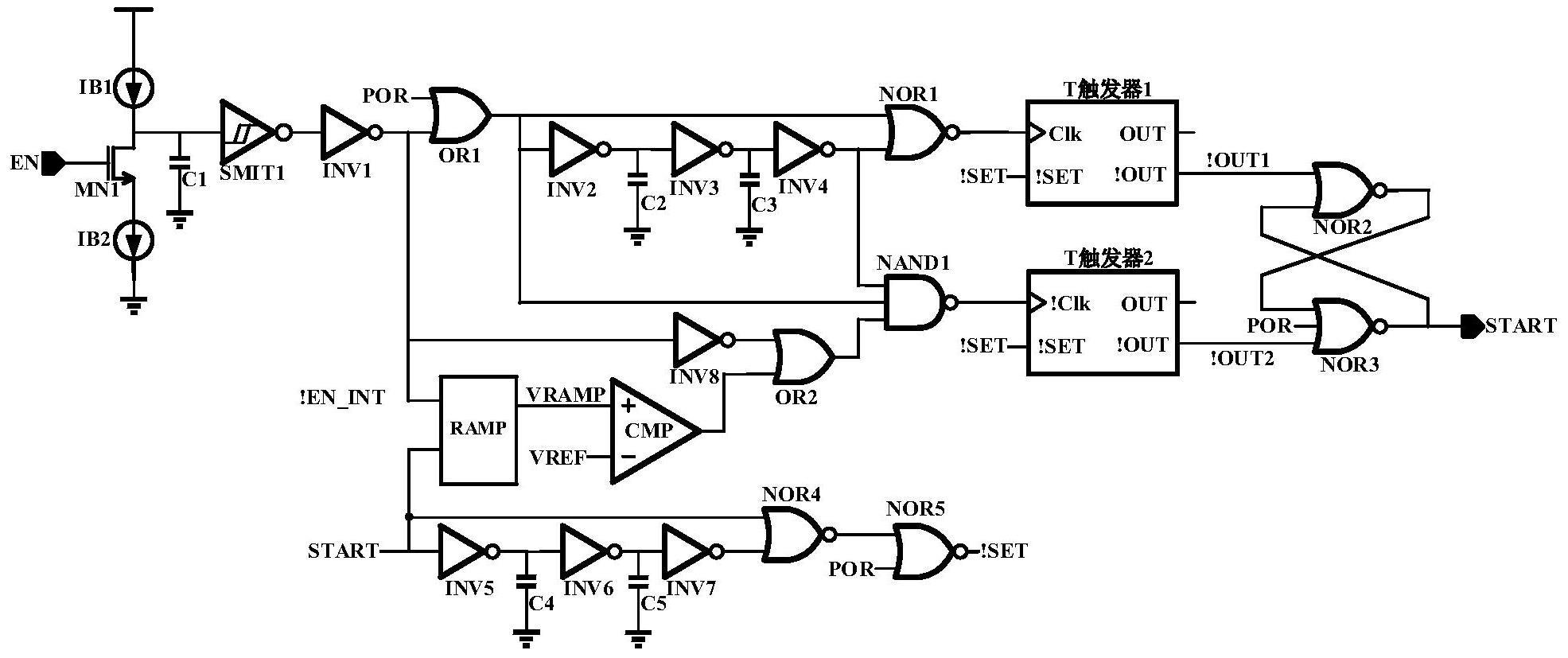

3、一种使能电路,包括第一nmos管mn1、第一电流源ib1、第二电流源ib2、第一电容c1、第二电容c2、第三电容c3、第四电容c4、第五电容c5、第一施密特触发器smit1、第一反相器inv1、第二反相器inv2、第三反相器inv3、第四反相器inv4、第五反相器inv5、第六反相器inv6、第七反相器inv7、第八反相器inv8、第一或门or1、第二或门or2、第一或非门nor1、第二或非门nor2、第三或非门nor3、第四或非门nor4、第五或非门nor5、比较器cmp、第一与非门nand1、ramp模块、第一t触发器和第二t触发器;其中,第一nmos管mn1的栅极接使能信号,其漏极接第一电流源ib1的一端、第一电容c1的一端和第一施密特触发器smit1的输入端,第一nmos管mn1的源极接第二电流源ib2的一端,第一电流源ib1的另一端接电源,第二电流源ib2的另一端、第一电容c1的另一端接地;第一施密特触发器smit1的输出端接第一反相器inv1的输入端,第一反相器inv1的输出端接第一或门or1的一个输入端、第八反相器inv8的输入端和ramp模块的一个输入端;第一或门or1的另一个输入端接复位信号,第一或门or1的输出端接第一或非门nor1的一个输入端、第二反相器inv2的输入端和第一与非门nand1的第一输入端;第二反相器inv2的输出端接第二电容c2的一端和第三反相器inv3的输入端,第三反相器inv3的输出端接第三电容c3的一端和第四反相器inv4的输入端,第四反相器inv4的输出端接第一或非门nor1的另一个输入端、第一与非门nand1的第二输入端;第二电容c2的另一端和第三电容c3的另一端接地;第一或非门nor1的输出端接第一t触发器的时钟信号输入端,第一t触发器的置位信号端接第五或非门nor5的输出端,第一t触发器的反向输出端接第二或非门nor2的一个输入端,第二或非门nor2的另一个输入端接第三或非门nor3的输出端;第一与非门nand1的输出端接第二t触发器的时钟信号端,第二t触发器的置位信号端接第五或非门nor5的输出端,第二t触发器的反向输出端接第三或非门nor3的第一输入端,第三或非门nor3的第二输入端接复位信号,第三或非门nor3的第三输入端接第二或非门nor2的输出端,第三或非门nor3的输出端为使能电路的输出端;第一t触发器为上升沿有效,第二t触发器为下降沿有效;第八反相器inv8的输出端接第二或门or2的一个输入端,第二或门or2的另一个输入端接比较器的输出端,第二或门or2的输出端接第一与非门nand1的第三输入端;ramp模块的另一个输入端接第三或非门nor3的输出端,ramp模块的输出端输出vramp电压到比较器的正输入端,比较器的负输入端接基准电压;第五反相器inv5的输入端接第三或非门nor3的输出端,第五反相器inv5的输出端接第四电容c4的一端和第六反相器inv6的输入端,第六反相器inv6的输出端接第五电容c5的一端和第七反相器inv7的输入端,第七反相器inv7的输出端接第四或非门nor4的一个输入端,第四电容c4的另一端和第五电容c5的另一端接地;第四或非门nor4的另一个输入端接三或非门nor3的输出端,第四或非门nor4的输出端接第五或非门nor5的一个输入端,第五或非门nor5的另一个输入端接复位信号。

4、本发明的有益效果为:可以检测出外部使能信号是电平形式还是脉冲形式,从而可以兼顾两种使能模式。

技术特征:

1.一种使能电路,其特征在于,包括第一nmos管mn1、第一电流源ib1、第二电流源ib2、第一电容c1、第二电容c2、第三电容c3、第四电容c4、第五电容c5、第一施密特触发器smit1、第一反相器inv1、第二反相器inv2、第三反相器inv3、第四反相器inv4、第五反相器inv5、第六反相器inv6、第七反相器inv7、第八反相器inv8、第一或门or1、第二或门or2、第一或非门nor1、第二或非门nor2、第三或非门nor3、第四或非门nor4、第五或非门nor5、比较器cmp、第一与非门nand1、ramp模块、第一t触发器和第二t触发器;其中,第一nmos管mn1的栅极接使能信号,其漏极接第一电流源ib1的一端、第一电容c1的一端和第一施密特触发器smit1的输入端,第一nmos管mn1的源极接第二电流源ib2的一端,第一电流源ib1的另一端接电源,第二电流源ib2的另一端、第一电容c1的另一端接地;第一施密特触发器smit1的输出端接第一反相器inv1的输入端,第一反相器inv1的输出端接第一或门or1的一个输入端、第八反相器inv8的输入端和ramp模块的一个输入端;第一或门or1的另一个输入端接复位信号,第一或门or1的输出端接第一或非门nor1的一个输入端、第二反相器inv2的输入端和第一与非门nand1的第一输入端;第二反相器inv2的输出端接第二电容c2的一端和第三反相器inv3的输入端,第三反相器inv3的输出端接第三电容c3的一端和第四反相器inv4的输入端,第四反相器inv4的输出端接第一或非门nor1的另一个输入端、第一与非门nand1的第二输入端;第二电容c2的另一端和第三电容c3的另一端接地;第一或非门nor1的输出端接第一t触发器的时钟信号输入端,第一t触发器的置位信号端接第五或非门nor5的输出端,第一t触发器的反向输出端接第二或非门nor2的一个输入端,第二或非门nor2的另一个输入端接第三或非门nor3的输出端;第一与非门nand1的输出端接第二t触发器的时钟信号端,第二t触发器的置位信号端接第五或非门nor5的输出端,第二t触发器的反向输出端接第三或非门nor3的第一输入端,第三或非门nor3的第二输入端接复位信号,第三或非门nor3的第三输入端接第二或非门nor2的输出端,第三或非门nor3的输出端为使能电路的输出端;第一t触发器为上升沿有效,第二t触发器为下降沿有效;第八反相器inv8的输出端接第二或门or2的一个输入端,第二或门or2的另一个输入端接比较器的输出端,第二或门or2的输出端接第一与非门nand1的第三输入端;ramp模块的另一个输入端接第三或非门nor3的输出端,ramp模块的输出端输出vramp电压到比较器的正输入端,比较器的负输入端接基准电压;第五反相器inv5的输入端接第三或非门nor3的输出端,第五反相器inv5的输出端接第四电容c4的一端和第六反相器inv6的输入端,第六反相器inv6的输出端接第五电容c5的一端和第七反相器inv7的输入端,第七反相器inv7的输出端接第四或非门nor4的一个输入端,第四电容c4的另一端和第五电容c5的另一端接地;第四或非门nor4的另一个输入端接三或非门nor3的输出端,第四或非门nor4的输出端接第五或非门nor5的一个输入端,第五或非门nor5的另一个输入端接复位信号。

技术总结

本发明属于模拟集成电路技术领域,具体涉及一种使能电路。本发明提出了一种可兼顾两种使能形式的使能电路。通过先对使能信号的上升沿进行检测,直接控制芯片启动,与此同时对外部使能信号进行检测,若检测为电平信号,则使能信号无效后就关闭芯片;若检测为脉冲信号,则使能无效后仍保持芯片开启,直到检测到下一个使能信号的脉冲时再关闭芯片。

技术研发人员:王卓,吴徽,何金阳,杨阳,周泽坤,张波

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!