电路板结构及其制作方法与流程

本申请涉及电路板制作,尤其涉及一种内埋电感的电路板结构及其制作方法。

背景技术:

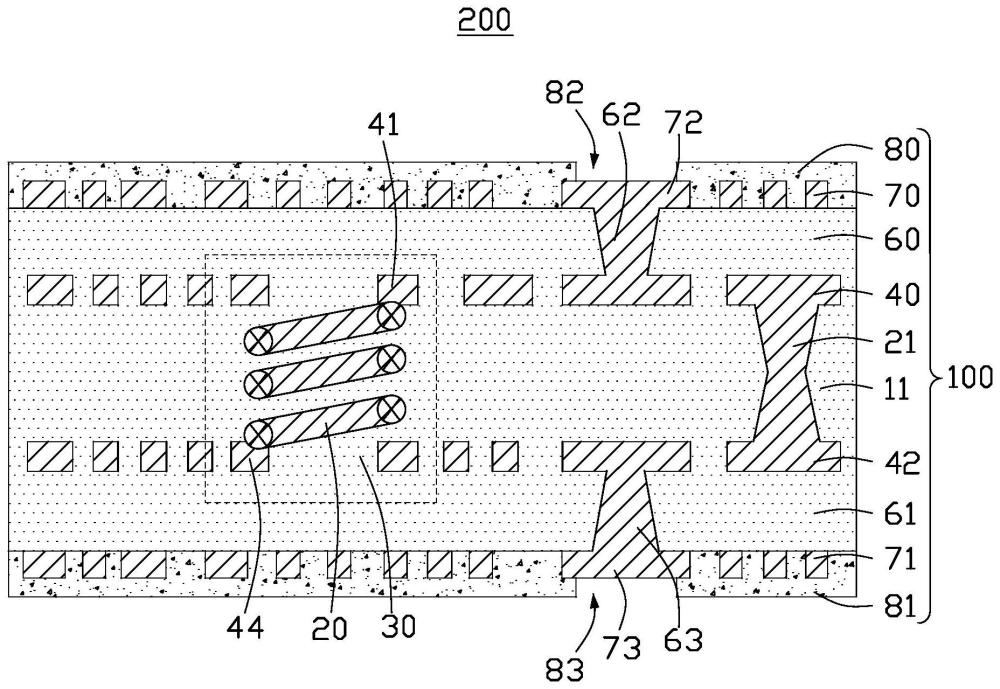

1、传统工艺通常将电感组件封装在电路板上,如图1所示,电路板结构200’包括电路基板100’和设置于电路基板100’上的电感组件20’。电感组件20’包括本体21’和电连接于本体21’的多个引脚22’,电路基板100’对应贯穿设有多个插接孔r,多个引脚22’对应设于插接孔r内。由于电感组件20’的尺寸较大,导致最终产品的厚度较厚。并且,插接孔r的存在还将导致电路基板100’内的布线空间缩小。另外,该工艺还需对电感组件20’进行后续封装,制程繁琐。

技术实现思路

1、为了解决上述问题,本申请的目的在于提供一种内埋电感的电路板结构的制作方法,该制作方法通过在制作电路板过程中直接形成电感线圈,制作过程简单,电感占用布线空间小,内埋的方式不增加电路板结构的整体厚度,且无需后续封装制程。

2、另外,本申请的另一目的还在于提供一种采用上述制作方法制备得到的内埋电感的电路板结构。

3、本申请一实施例提供一种电路板结构的制作方法,包括以下步骤:

4、提供一双面覆铜板,所述双面覆铜板包括基材层和设置于所述基材层相对两侧的第一铜层和第二铜层,所述双面覆铜板贯穿设有至少一通孔;

5、于所述通孔的内壁形成螺纹槽,所述第一铜层和所述第二铜层分别露出于所述螺纹槽的两端;

6、于所述螺纹槽内形成电感线圈,所述电感线圈的相对两端分别电连接所述第一铜层和第二铜层;以及

7、图形化所述第一铜层以形成第一线路层,图形化所述第二铜层以形成第二线路层,所述电感线圈的相对两端分别电连接所述第一线路层和第二线路层,获得电路板结构。

8、本申请还提供一种电路板结构,包括电路基板和设于所述电路基板内的电感线圈,所述电路基板包括基材层和设于所述基材层相对两侧的第一线路层和第二线路层,所述基材层贯穿设有一通孔,所述通孔的内壁设有螺纹槽,所述电感线圈设于所述螺纹槽,所述电感线圈的相对两端分别电连接所述第一线路层和第二线路层。

9、相较于现有技术中在电路板表面设置电感组件或将电感元件内埋于电路板的方式,本申请中提供的电路板结构的制作方法通过在基材层中开设通孔,于所述通孔的内壁设置螺纹槽,然后于螺纹槽内形成电感线圈,获得电路板结构。在电路板制作过程中同步完成电感线圈的制作,所述电感线圈的占用空间小,可有效节省电路板结构的布线空间,并可减少最终产品的厚度,使其更便于携带。该制作方法制程简单、减少封装制程,且不存在封装过程中会出现的接触不良问题。

技术特征:

1.一种电路板结构的制作方法,其特征在于,包括以下步骤:

2.如权利要求1所述的制作方法,其特征在于,采用攻丝工艺于所述通孔的内壁形成所述螺纹槽。

3.如权利要求1所述的制作方法,其特征在于,步骤“于所述螺纹槽内形成电感线圈”还包括:

4.如权利要求1所述的制作方法,其特征在于,步骤“图形化所述第一铜层以形成第一线路层,图形化所述第二铜层以形成第二线路层”后,还包括:

5.如权利要求1所述的制作方法,其特征在于,所述双面覆铜板还贯穿设有至少一导通孔;

6.如权利要求1所述的制作方法,其特征在于,还包括:

7.如权利要求1所述的制作方法,其特征在于,还包括:

8.一种电路板结构,其特征在于,包括电路基板和设于所述电路基板内的电感线圈,所述电路基板包括基材层和设于所述基材层相对两侧的第一线路层和第二线路层,所述基材层贯穿设有一通孔,所述通孔的内壁设有螺纹槽,所述电感线圈设于所述螺纹槽,所述电感线圈的相对两端分别电连接所述第一线路层和第二线路层。

9.如权利要求8所述的电路板结构,其特征在于,所述通孔内设有填充树脂;所述电感线圈的表面与所述通孔的内壁大致平齐。

10.如权利要求8所述的电路板结构,其特征在于,所述电路基板还包括第一绝缘层、第二绝缘层、第三线路层和第四线路层,所述第一绝缘层设置于所述第一线路层背离所述基材层的一侧,所述第二绝缘层设置于所述第二线路层背离所述基材层的一侧,所述第一绝缘层包覆所述第一线路层,所述第二绝缘层包覆所述第二线路层;

技术总结

本申请提供一种电路板结构的制作方法,包括以下步骤:提供一双面覆铜板,所述双面覆铜板包括基材层和设置于基材层相对两侧的第一铜层和第二铜层,所述双面覆铜板贯穿设有至少一通孔;于通孔的内壁形成螺纹槽,所述第一铜层和所述第二铜层分别露出于螺纹槽的两端;于螺纹槽内形成电感线圈;以及图形化第一铜层以形成第一线路层,图形化第二铜层以形成第二线路层,所述电感线圈的相对两端分别电连接所述第一线路层和第二线路层,获得电路板结构。该制作方法在制作电路板的过程中直接形成电感线圈,制程简单、无需后续封装制程,且电感线圈占用空间小,有利于节省电路板的布线空间,且能够降低产品厚度。本申请还提供一种电路板结构。

技术研发人员:傅志杰,林海涛

受保护的技术使用者:宏启胜精密电子(秦皇岛)有限公司

技术研发日:

技术公布日:2024/8/20

- 还没有人留言评论。精彩留言会获得点赞!