一种应用于高压工艺中的使能电路及芯片的制作方法

本发明涉及集成电路设计与应用,特别是涉及一种应用于高压工艺中的使能电路及芯片。

背景技术:

1、使能电路负责控制使能信号的输入和输出,通常与芯片或电路的使能端连接,使能电路基于使能信号控制芯片或电路的开启状态。当使能信号的电压接近40伏特的高压时,如何将40伏特的使能信号精准地、稳定地转化成可供芯片或电路开启的使能信号,同时避免毛刺干扰对后级的芯片或电路的安全性带来消极影响,是使能电路设计与应用的重点。

2、应该注意,上面对技术背景的介绍只是为了方便对本申请的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本申请的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种应用于高压工艺中的使能电路及芯片,用于解决现有技术中将高压的使能信号精准地、稳定地转化成可供芯片或电路开启的使能信号实现起来较为困难的问题。

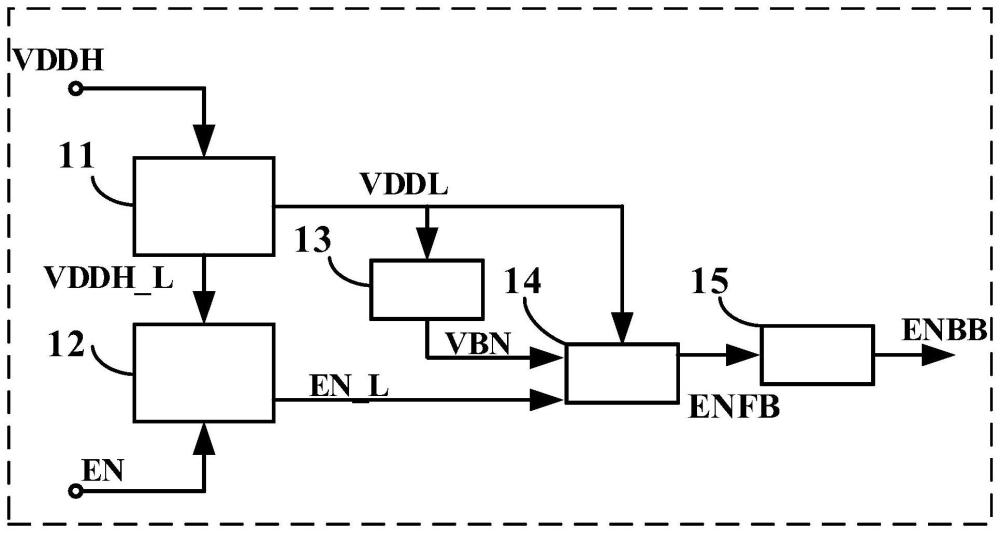

2、为实现上述目的及其他相关目的,本发明提供一种应用于高压工艺中的使能电路,所述应用于高压工艺中的使能电路至少包括:第一转换模块、第二转换模块、基准模块、比较模块及整形模块,其中:

3、所述第一转换模块的输入端与第一信号连接,通过对所述第一信号的转换操作,生成用于提供电能的第二信号及用于提供驱动的第三信号;

4、所述第二转换模块的输入端与第一使能信号及所述第三信号连接,通过对所述第一使能信号的转换操作,生成第二使能信号;

5、所述基准模块的输入端与所述第一转换模块的输出端连接,基于所述第二信号提供的电能生成基准信号;

6、所述比较模块的输入端与所述基准模块的输出端及所述第二转换模块的输出端连接,通过对所述第二使能信号与所述基准信号的比较操作,生成对应的第三使能信号;

7、所述整形模块的输入端与所述比较模块的输出端连接,通过对所述第三使能信号的整形操作,生成控制后级负载开启的第四使能信号。

8、可选地,所述第一转换模块包括:第一电阻、第一nmos功率管、第一稳压二极管及第一电容,其中:所述第一电阻的第一端与所述第一信号连接,其中,基于所述第一电阻的第二端生成所述第三信号;所述第一nmos功率管的漏极与所述第一电阻的第一端连接,所述第一nmos功率管的栅极与所述第一电阻的第二端连接,其中,基于所述第一nmos功率管的源极生成所述第二信号;所述第一稳压二极管的负极与所述第一nmos功率管的栅极连接,所述第一稳压二极管的正极与参考地连接;所述第一电容连接于所述第一nmos功率管的源极与参考地之间。

9、可选地,所述第一信号的电压范围包括大于0伏特且小于等于40伏特。

10、可选地,所述第一nmos功率管的耐压值大于40伏特。

11、可选地,所述基准模块包括:第二电阻及第二nmos功率管,其中:所述第二nmos功率管的漏极与栅极连接,所述第二nmos功率管的源极与参考地连接,其中,基于所述第二nmos功率管的栅极生成所述基准信号;所述第二电阻连接于所述第二信号与所述第二nmos功率管的漏极之间。

12、可选地,所述第二转换模块包括:第三nmos功率管及第四nmos功率管,其中:所述第三nmos功率管的漏极与所述第一使能信号连接,所述第三nmos功率管的栅极与所述第三信号连接,其中,基于所述第三nmos功率管的源极生成所述第二使能信号;所述第四nmos功率管的漏极与所述第三nmos功率管的源极连接,所述第四nmos功率管的栅极与所述第二nmos功率管的栅极连接,所述第四nmos功率管的源极与参考地连接。

13、可选地,所述第一使能信号的电压范围包括大于0伏特且小于等于40伏特。

14、可选地,所述第三nmos功率管的耐压值大于40伏特。

15、可选地,所述比较模块包括:第一pmos功率管、第二pmos功率管、第五nmos功率管、第六nmos功率管、第七nmos功率管、第八nmos功率管及第一非门,其中:所述第一pmos功率管的源极与所述第二信号连接;所述第二pmos功率管的源极与所述第一pmos功率管的源极连接,所述第二pmos功率管的栅极与所述第一pmos功率管的栅极连接,所述第二pmos功率管的漏极与所述第二pmos功率管的栅极连接;所述第五nmos功率管的漏极与所述第一pmos功率管的漏极连接,所述第五nmos功率管的栅极与所述第三nmos功率管的源极连接;所述第六nmos功率管的漏极与所述第五nmos功率管的源极连接,所述第六nmos功率管的栅极与所述第五nmos功率管的栅极连接,所述第六nmos功率管的源极与参考地连接;所述第七nmos功率管的漏极与所述第六nmos功率管的漏极连接,所述第七nmos功率管的源极与参考地连接;所述第八nmos功率管的漏极与所述第二pmos功率管的漏极连接,所述第八nmos功率管的栅极与所述第四nmos功率管的栅极连接,所述第八nmos功率管的源极与参考地连接;所述第一非门的输入端与所述第五nmos功率管的漏极连接,所述第一非门的输出端与所述第七nmos功率管的栅极连接,其中,基于所述第一非门的输出端生成所述第三使能信号。

16、可选地,所述整形模块包括第二非门及第三非门,其中:所述第二非门的输入端与所述第三使能信号连接;所述第三非门的输入端与所述第二非门的输出端连接。

17、为实现上述目的及其他相关目的,本发明提供一种芯片,所述芯片包括所述应用于高压工艺中的使能电路,所述芯片输出用于控制后级负载开启的所述第四使能信号。

18、如上所述,本发明的一种应用于高压工艺中的使能电路及芯片,具有以下有益效果:

19、1)本发明的应用于高压工艺中的使能电路及芯片,能够将40伏特的使能信号精准地、稳定地转化成可供芯片或电路开启的使能信号,同时能够抵抗高压信号中的毛刺信号对后级的芯片或电路的干扰。

20、2)本发明的应用于高压工艺中的使能电路及芯片,结构简单,操作简便,具有广泛的适用性。

技术特征:

1.一种应用于高压工艺中的使能电路,其特征在于,所述应用于高压工艺中的使能电路至少包括:第一转换模块、第二转换模块、基准模块、比较模块及整形模块,其中:

2.根据权利要求1所述的应用于高压工艺中的使能电路,其特征在于:所述第一转换模块包括:第一电阻、第一nmos功率管、第一稳压二极管及第一电容,其中:所述第一电阻的第一端与所述第一信号连接,其中,基于所述第一电阻的第二端生成所述第三信号;所述第一nmos功率管的漏极与所述第一电阻的第一端连接,所述第一nmos功率管的栅极与所述第一电阻的第二端连接,其中,基于所述第一nmos功率管的源极生成所述第二信号;所述第一稳压二极管的负极与所述第一nmos功率管的栅极连接,所述第一稳压二极管的正极与参考地连接;所述第一电容连接于所述第一nmos功率管的源极与参考地之间。

3.根据权利要求1所述的应用于高压工艺中的使能电路,其特征在于:所述第一信号的电压范围包括大于0伏特且小于等于40伏特。

4.根据权利要求2所述的应用于高压工艺中的使能电路,其特征在于:所述第一nmos功率管的耐压值大于40伏特。

5.根据权利要求1所述的应用于高压工艺中的使能电路,其特征在于:所述基准模块包括:第二电阻及第二nmos功率管,其中:所述第二nmos功率管的漏极与栅极连接,所述第二nmos功率管的源极与参考地连接,其中,基于所述第二nmos功率管的栅极生成所述基准信号;所述第二电阻连接于所述第二信号与所述第二nmos功率管的漏极之间。

6.根据权利要求5所述的应用于高压工艺中的使能电路,其特征在于:所述第二转换模块包括:第三nmos功率管及第四nmos功率管,其中:所述第三nmos功率管的漏极与所述第一使能信号连接,所述第三nmos功率管的栅极与所述第三信号连接,其中,基于所述第三nmos功率管的源极生成所述第二使能信号;所述第四nmos功率管的漏极与所述第三nmos功率管的源极连接,所述第四nmos功率管的栅极与所述第二nmos功率管的栅极连接,所述第四nmos功率管的源极与参考地连接。

7.根据权利要求1所述的应用于高压工艺中的使能电路,其特征在于:所述第一使能信号的电压范围包括大于0伏特且小于等于40伏特。

8.根据权利要求6所述的应用于高压工艺中的使能电路,其特征在于:所述第三nmos功率管的耐压值大于40伏特。

9.根据权利要求6所述的应用于高压工艺中的使能电路,其特征在于:所述比较模块包括:第一pmos功率管、第二pmos功率管、第五nmos功率管、第六nmos功率管、第七nmos功率管、第八nmos功率管及第一非门,其中:所述第一pmos功率管的源极与所述第二信号连接;所述第二pmos功率管的源极与所述第一pmos功率管的源极连接,所述第二pmos功率管的栅极与所述第一pmos功率管的栅极连接,所述第二pmos功率管的漏极与所述第二pmos功率管的栅极连接;所述第五nmos功率管的漏极与所述第一pmos功率管的漏极连接,所述第五nmos功率管的栅极与所述第三nmos功率管的源极连接;所述第六nmos功率管的漏极与所述第五nmos功率管的源极连接,所述第六nmos功率管的栅极与所述第五nmos功率管的栅极连接,所述第六nmos功率管的源极与参考地连接;所述第七nmos功率管的漏极与所述第六nmos功率管的漏极连接,所述第七nmos功率管的源极与参考地连接;所述第八nmos功率管的漏极与所述第二pmos功率管的漏极连接,所述第八nmos功率管的栅极与所述第四nmos功率管的栅极连接,所述第八nmos功率管的源极与参考地连接;所述第一非门的输入端与所述第五nmos功率管的漏极连接,所述第一非门的输出端与所述第七nmos功率管的栅极连接,其中,基于所述第一非门的输出端生成所述第三使能信号。

10.根据权利要求1所述的应用于高压工艺中的使能电路,其特征在于:所述整形模块包括第二非门及第三非门,其中:所述第二非门的输入端与所述第三使能信号连接;所述第三非门的输入端与所述第二非门的输出端连接。

11.一种芯片,其特征在于:所述芯片包括:如根据权利要求1-10任意一项所述的应用于高压工艺中的使能电路,所述芯片输出用于控制后级负载开启的所述第四使能信号。

技术总结

本发明提供一种应用于高压工艺中的使能电路包括:第一转换模块的输入端与第一信号连接,通过对第一信号的转换操作,生成第二信号及第三信号;第二转换模块通过对第一使能信号的转换操作,生成第二使能信号;基准模块基于第二信号提供的电能生成基准信号;比较模块的输入端通过对第二使能信号与基准信号的比较操作,生成对应的第三使能信号;整形模块通过对第三使能信号的整形操作,生成控制后级负载开启的第四使能信号。能够将40伏特的使能信号精准地、稳定地转化成可供芯片或电路开启的使能信号,同时能够抵抗高压信号中的毛刺信号对后级的芯片或电路的干扰。结构简单,操作简便,具有广泛的适用性。

技术研发人员:陈翔,张海潮

受保护的技术使用者:湖南芯力特电子科技有限公司

技术研发日:

技术公布日:2024/8/27

- 还没有人留言评论。精彩留言会获得点赞!