一种宽带高速多模可编程分频器

本发明涉及一种可编程分频器,特别是涉及一种宽带高速多模可编程分频器。

背景技术:

1、无线通信系统、有线接口系统等都需要基于锁相环的频率综合器或时钟发生器提供载波/本振信号或时钟信号。高性能的分频器是锁相环系统中必不可少的一个关键模块。在现代通信系统中,为了符合不同的协议标准和地区的要求,锁相环被要求提供不同的输出频率,一方面需要压控振荡器能够产生宽范围的频率输出,另一方面要求分频器能够工作在宽频带,并且具有不同的分频比能力。而为了增强分频器的灵活性,往往需要采用可编程的分频器技术。

2、目前实现可编程分频器技术主要有三种形式:基于相位开关的可编程分频器、基于脉冲吞咽技术的可编程分频器、基于2/3分频器的多模分频器。传统的可编程分频器工作频率范围受到限制,大多是工作在几百兆赫兹的频率带宽内,随着现代电子信息技术的发展,特别是毫米波雷达系统的应用中,采用调频连续波的工作体制,系统的带宽直接决定了毫米波雷达系统的测距精度,测速精度等系统性能,因此要求分频器能供工作在很大的带宽范围,达到几ghz的频率带宽,目前已有的77ghz毫米波雷达,工作带宽范围达到了4ghz左右。已有的技术在扩展频率范围时通过设计两组工作频率在不同范围的分频器,然后通过开关进行切换以适应不同的频率范围需求,往往受到功耗和面积的制约,极大的增加了设计和制作成本。

技术实现思路

1、本发明所要解决的技术问题是提供一种宽带高速多模可编程分频器,能够拓宽工作的频率范围,同时降低电路的复杂度、功耗和面积。

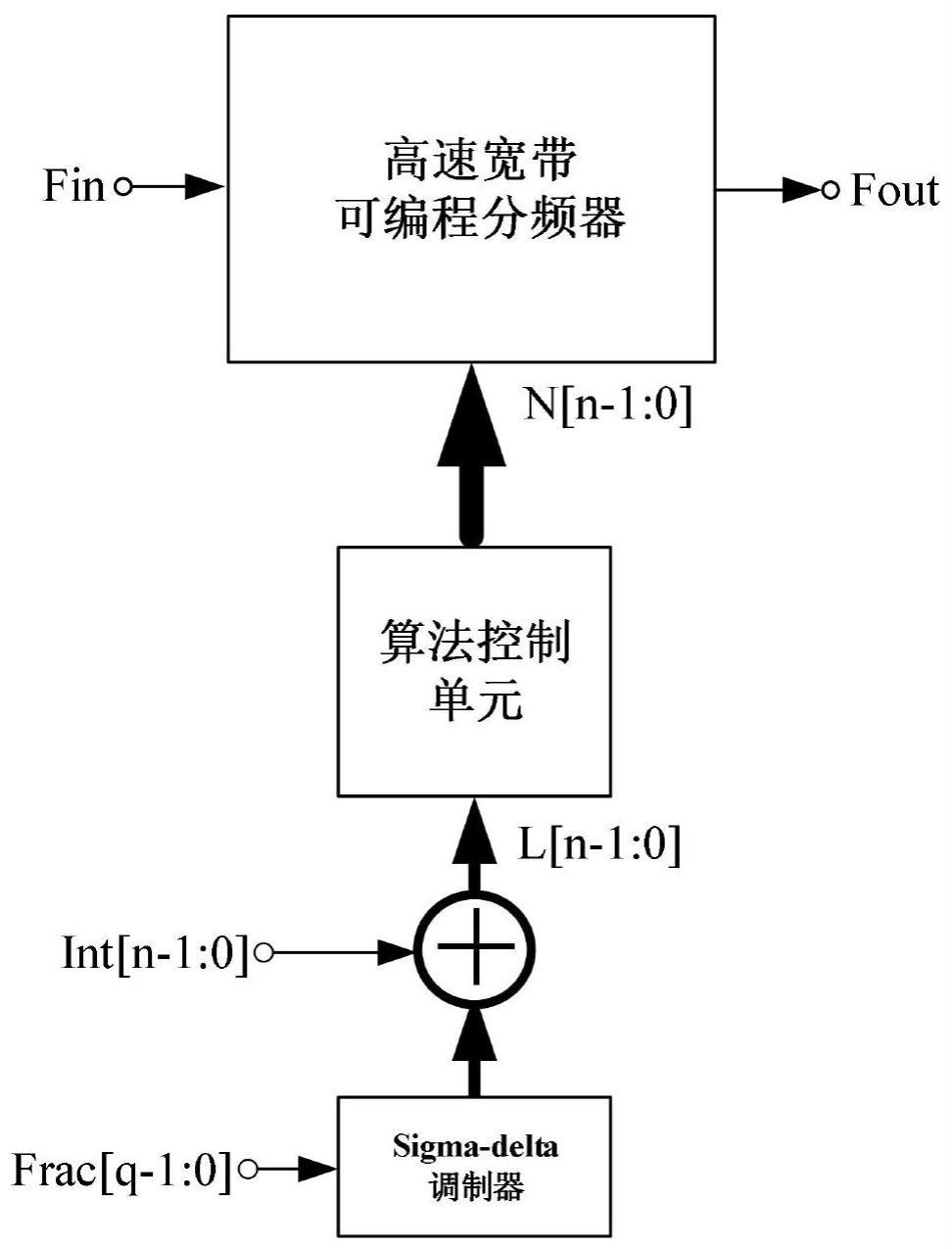

2、本发明解决其技术问题所采用的技术方案是:提供一种宽带高速多模可编程分频器,包括可编程分频器模块、sigma-delta调制器模块、加法器模块和算法控制模块;所述可编程分频器模块包括预分频器、p计数器和吞脉冲s计数器;所述预分频器集成了m/m+1以及2m/2m+1的分频功能,使得在输入频率成倍数增加的情况下,经过预分频器处理后的输出频率一样,不增加p计数器和s计数器的工作频率范围,降低设计难度;所述sigma-delta调制器用于产生-3~4的随机数;所述加法器用于将所述随机数与外部数字输入int[n:0]相加;所述算法控制模块用于控制所述吞脉冲s计数器的工作位数以及基于所述加法器的输出l[n-1:0]进行处理满足所述可编程分频器模块的逻辑要求。

3、所述p计数器包括若干依次连接的d触发器单元,与所述预分频器的输出相连的低位d触发器单元为基于tspc结构的d触发器单元,与所述预分频器的输出相连的高位d触发器单元为基于逻辑门的静态d触发器单元。

4、所述m为2的次幂值,所述p计数器的位数大于或等于m,所述p计数器的位数减一大于所述吞脉冲s计数器的位数,并且所述吞脉冲s计数器的位数为log2m,最高位为log2m-1位;所述p计数器的位数大于或等log2m+1,最低位为log2m位。

5、所述算法控制模块包括:输入信号判断单元,用于判断输入信号的频率是否超过阈值;第一处理单元,用于在输入信号的频率超过阈值时,控制所述预分频器采用2m/2m+1的分频功能,控制所述吞脉冲s计数器以第一工作位数k进行工作,并将所述加法器的输出l[n-1:0]中的l[n-1:k]作为第一控制字信号送入所述p计数器,将所述加法器的输出l[n-1:0]中的l[k-1:0]作为第二控制字信号送入到所述吞脉冲s计数器;第二处理单元,用于在输入信号的频率未超过阈值时,控制所述预分频器采用m/m+1的分频功能,控制所述吞脉冲s计数器以第二工作位数r进行工作,所述第二工作位数r小于第一工作位数k,并将所述吞脉冲s计数器的第三位置零,将所述加法器的输出l[n-1:0]中的l[r-1:0]作为第一控制字信号送入所述吞脉冲s计数器,将所述加法器的输出l[n-1:0]中的l[n-2:r]作为第二控制字信号送入所述p计数器,并舍去加法器的输出l[n-1:0]中的l[n-1]。

6、经过所述预分频器处理后,如果输入信号频率存在两倍关系,所述预分频器的输出信号频率相同,这样不会增加p计数器和s计数器的工作频率范围,降低设计难度。

7、有益效果

8、由于采用了上述的技术方案,本发明与现有技术相比,具有以下的优点和积极效果:本发明针对宽频带,多分频比的应用需求,提出了一种宽带多模可编程分频器,通过算法控制优化,保障了集成多组预分频器多模可编程宽带分频器二进制代码变化对ps计数器的有效控制,实现了同时具有整数和小数分频的分频器,避免了传统架构中需要使用两组或多组工作在不同频率范围下的分频器,降低了硬件制作成本和电路的复杂度,并且针对功耗进行了优化,配置的可编程位数能够实现大范围的分频比,满足大多数的应用场景需求,大大地增强了分频器的应用灵活性和通用性。

技术特征:

1.一种宽带高速多模可编程分频器,其特征在于,包括可编程分频器模块、sigma-delta调制器模块、加法器模块和算法控制模块;所述可编程分频器模块包括预分频器、p计数器和吞脉冲s计数器;所述预分频器集成了m/m+1以及2m/2m+1的分频功能;所述sigma-delta调制器用于产生-3~4的随机数;所述加法器用于将所述随机数与外部数字输入int[n:0]相加;所述算法控制模块用于控制所述吞脉冲s计数器的工作位数以及基于所述加法器的输出l[n-1:0]进行处理满足所述可编程分频器模块的逻辑要求。

2.根据权利要求1所述的宽带高速多模可编程分频器,其特征在于,所述p计数器包括若干依次连接的d触发器单元,与所述预分频器的输出相连的低位d触发器单元为基于tspc结构的d触发器单元,与所述预分频器的输出相连的高位d触发器单元为基于逻辑门的静态d触发器单元。

3.根据权利要求1所述的宽带高速多模可编程分频器,其特征在于,所述m为2的次幂值,所述p计数器的位数大于或等于m,所述p计数器的位数减一大于所述吞脉冲s计数器的位数,并且所述吞脉冲s计数器的位数为log2m,最高位为log2m-1位;所述p计数器的位数大于或等log2m+1,最低位为log2m位。

4.根据权利要求1所述的宽带高速多模可编程分频器,其特征在于,所述算法控制模块包括:输入信号判断单元,用于判断输入信号的频率是否超过阈值;第一处理单元,用于在输入信号的频率超过阈值时,控制所述预分频器采用2m/2m+1的分频功能,控制所述吞脉冲s计数器以第一工作位数k进行工作,并将所述加法器的输出l[n-1:0]中的l[n-1:k]作为第一控制字信号送入所述p计数器,将所述加法器的输出l[n-1:0]中的l[k-1:0]作为第二控制字信号送入到所述吞脉冲s计数器;第二处理单元,用于在输入信号的频率未超过阈值时,控制所述预分频器采用m/m+1的分频功能,控制所述吞脉冲s计数器以第二工作位数r进行工作,所述第二工作位数r小于第一工作位数k,并将所述吞脉冲s计数器的第三位置零,将所述加法器的输出l[n-1:0]中的l[r-1:0]作为第一控制字信号送入所述吞脉冲s计数器,将所述加法器的输出l[n-1:0]中的l[n-2:r]作为第二控制字信号送入所述p计数器,并舍去加法器的输出l[n-1:0]中的l[n-1]。

5.根据权利要求4所述的宽带高速多模可编程分频器,其特征在于,经过所述预分频器处理后,如果输入信号频率存在两倍关系,所述预分频器的输出信号频率相同。

技术总结

本发明涉及一种宽带高速多模可编程分频器,包括可编程分频器模块、sigma‑delta调制器模块、加法器模块和算法控制模块;所述可编程分频器模块包括预分频器、P计数器和吞脉冲S计数器;所述预分频器集成了M/M+1以及2M/2M+1的分频功能;所述sigma‑delta调制器用于产生‑3~4的随机数;所述加法器用于将所述随机数与外部数字输入Int[n:0]相加;所述算法控制模块用于控制所述吞脉冲S计数器的工作位数以及基于所述加法器的输出L[n‑1:0]进行处理满足所述可编程分频器模块的逻辑要求。本发明能够拓宽分频器工作的频率范围,同时降低电路的复杂度、功耗和面积。

技术研发人员:伍锡安,田彤

受保护的技术使用者:中国科学院上海微系统与信息技术研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!