缓冲器电路及半导体结构的制作方法

本发明涉及半导体,尤其涉及一种缓冲器电路及半导体结构。

背景技术:

1、缓冲器电路(buffer circuit)是芯片和处理器设计中最常用的数字电路(digital circuit)之一。缓冲器操作(或运行、工作)以接收输入信号并输出保持该输入信号所具有的特性但具有更好的驱动能力的输出信号。在中央处理器(central processingunit,cpu)、图形处理器(graphics processing unit,gpu)和加速处理器(acceleratedprocessing unit,apu)等高速应用中,信号延迟(signal delay)量(amount)是评估性能的重要指针。因此,需要高速运行的缓冲器电路来增强高速应用的性能。

技术实现思路

1、有鉴于此,本发明提供一种缓冲器电路及半导体结构,以解决上述问题。

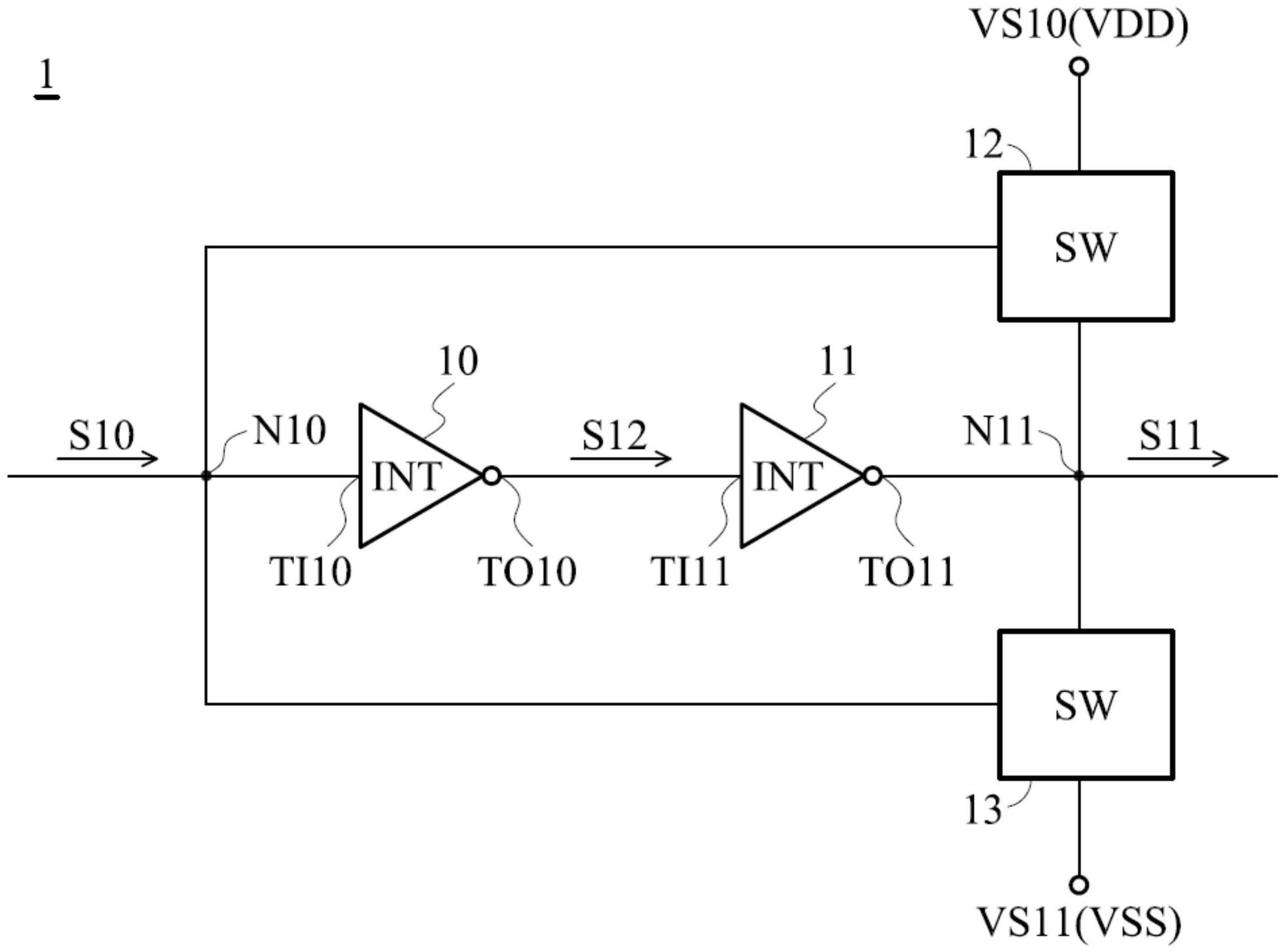

2、根据本发明的第一方面,公开一种缓冲器电路,用于在输入节点接收输入信号并在输出节点输出输出信号,包括:

3、第一反相器,耦接到该输入节点以接收该输入信号,将该输入信号反相以产生反相输入信号;

4、第二反相器,具有接收该反相输入信号的输入端子和耦接到该输出节点的输出端子;

5、第一开关,耦接在第一电压源端子和该输出节点之间并由该输入信号控制;以及

6、第二开关,耦接在该输出节点和第二电压源端子之间并由该输入信号控制,

7、其中,第一电压提供给该第一电压源端子,并且第二电压提供给该第二电压源端子,

8、响应于该输入信号从第二电平切换到第一电平,该第一开关导通以将该输出节点预充电至该第一电压,并且

9、响应于该输入信号从该第一电平转变为该第二电平,该第二开关导通以将该输出节点预放电至该第二电压。

10、根据本发明的第二方面,公开一种缓冲器电路的半导体结构,包括:

11、基板;

12、p型扩散区,形成于该基板上并平行于第一方向延伸;

13、n型扩散区,形成于基板上,与该p型扩散区间隔开,并平行于该第一方向延伸;

14、第一多晶硅区,形成于该p型扩散区和该n型扩散区上方,平行于第二方向延伸并跨越该p型扩散区和该n型扩散区,其中,该第一方向垂直于该第二个方向;

15、第一导电段,平行于该第一方向延伸;以及

16、第二导电段,与该第一导电段间隔开并平行于该第一方向延伸,

17、其中该p型扩散区包括第一p型扩散部,设置于该第一多晶硅区的第一侧,且该第一p型扩散部电连接至该第二导电段,

18、其中,该n型扩散区包括设置在该第一多晶硅区的该第一侧的第一n型扩散部,该第一n型扩散部与该第一导电段电连接,以及

19、其中,提供给该第一导电段的第一电压高于提供给该第二导电段的第二电压。

20、本发明的缓冲器电路由于包括:第一反相器,耦接到输入节点以接收输入信号,将输入信号反相以产生反相输入信号;第二反相器,具有接收该反相输入信号的输入端子和耦接到该输出节点的输出端子;第一开关,耦接在第一电压源端子和该输出节点之间并由该输入信号控制;以及第二开关,耦接在该输出节点和第二电压源端子之间并由该输入信号控制,其中,第一电压提供给该第一电压源端子,并且第二电压提供给该第二电压源端子,响应于该输入信号从第二电平切换到第一电平,该第一开关导通以将该输出节点预充电至该第一电压,并且响应于该输入信号从该第一电平转变为该第二电平,该第二开关导通以将该输出节点预放电至该第二电压。本发明提供的缓冲器电路可以根据输入信号的电压电平对输出信号进行预充电或预放电;因此,即使缓冲器电路的输出节点耦接重负载,输出信号仍可快速地达到预定电压电平以响应输入信号的电压电平的切换,从而实现缓冲器电路的高速运行。

技术特征:

1.一种缓冲器电路,用于在输入节点接收输入信号并在输出节点输出输出信号,其特征在于,包括:

2.如权利要求1所述的缓冲器电路,其特征在于:

3.如权利要求1或2所述的缓冲器电路,其特征在于,提供给该第一电压源端的该第一电压高于提供给该第二电压源端的该第二电压。

4.如权利要求1所述的缓冲器电路,其特征在于:

5.如权利要求4所述的缓冲器电路,其特征在于:

6.如权利要求4所述的缓冲器电路,其特征在于,该第一n型晶体管及该第二n型晶体管与该第一p型晶体管及该第二p型晶体管为金属氧化物半导体晶体管。

7.如权利要求1所述的缓冲器电路,其特征在于,该第二反相器包括:

8.如权利要求2所述的缓冲器电路,其特征在于,该第一n型晶体管与该第一p型晶体管为金属氧化物半导体晶体管。

9.如权利要求1所述的缓冲器电路,其特征在于,提供给该第一电压源端的该第一电压高于提供给该第二电压源端的该第二电压。

10.一种缓冲器电路的半导体结构,其特征在于,包括:

11.如权利要求10所述的半导体结构,其特征在于,还包括:

12.如权利要求10所述的半导体结构,其特征在于,还包括:

13.如权利要求10所述的半导体结构,其特征在于,还包括:

14.如权利要求13所述的半导体结构,其特征在于,还包括:

15.如权利要求13所述的半导体结构,其特征在于:

16.如权利要求13所述的半导体结构,其特征在于:

17.如权利要求16所述的半导体结构,其特征在于,还包括:

技术总结

本发明公开一种缓冲器电路,包括:第一反相器;第二反相器;第一开关;以及第二开关,第一电压提供给该第一电压源端子,并且第二电压提供给该第二电压源端子,响应于该输入信号从第二电平切换到第一电平,该第一开关导通以将该输出节点预充电至该第一电压,并且响应于该输入信号从该第一电平转变为该第二电平,该第二开关导通以将该输出节点预放电至该第二电压。本发明提供的缓冲器电路可以根据输入信号的电压电平对输出信号进行预充电或预放电;因此,即使缓冲器电路的输出节点耦接重负载,输出信号仍可快速地达到预定电压电平以响应输入信号的电压电平的切换,从而实现缓冲器电路的高速运行。

技术研发人员:游皓翔,杨任航

受保护的技术使用者:联发科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!