半导体结构、存储器及其制作方法、电子设备与流程

本技术涉及存储器领域,具体而言,本技术涉及一种半导体结构、存储器及其制作方法、电子设备。

背景技术:

1、mram(magnetoresistive random access memory,磁阻随机存取存储器)利用流经磁性隧道结中不同的自旋极化电流来驱动软磁体磁化方向的改变来实现写入功能,其具有dram(dynamic random access memory,动态随机存储器)的高集成度,以及sram(staticrandom-access memory,静态随机存取存储器)的高速读写能力,还具有闪存的非易失性,是最有可能代替dram的先进存储技术。

2、目前,传统的mram存储单元是由一个磁性隧道结(magnetic tunnel junction,mtj)和一个选择晶体管耦合构成。

3、通常情况下,由于mram存储单元需要大的写入电流和小的读出电流,为了提高mram存储器的读写稳定性,可以减小选择晶体管的尺寸以减小读出电流,以提高读稳定性,但也会因此减小写入电流,降低了写稳定性。相反,若增加选择晶体管的尺寸,可以增加写入电流,提高了写稳定性,但这样也会增加读出电流,降低了读稳定性,所以无法通过改变晶体管的尺寸来达到同时需要大的写电流和小的读电流的需求,因为通过改变晶体管的尺寸来改善读写的电流大小,可能会造成存储器件读写的失败。

技术实现思路

1、本技术提出一种半导体结构、存储器及其制作方法、电子设备。

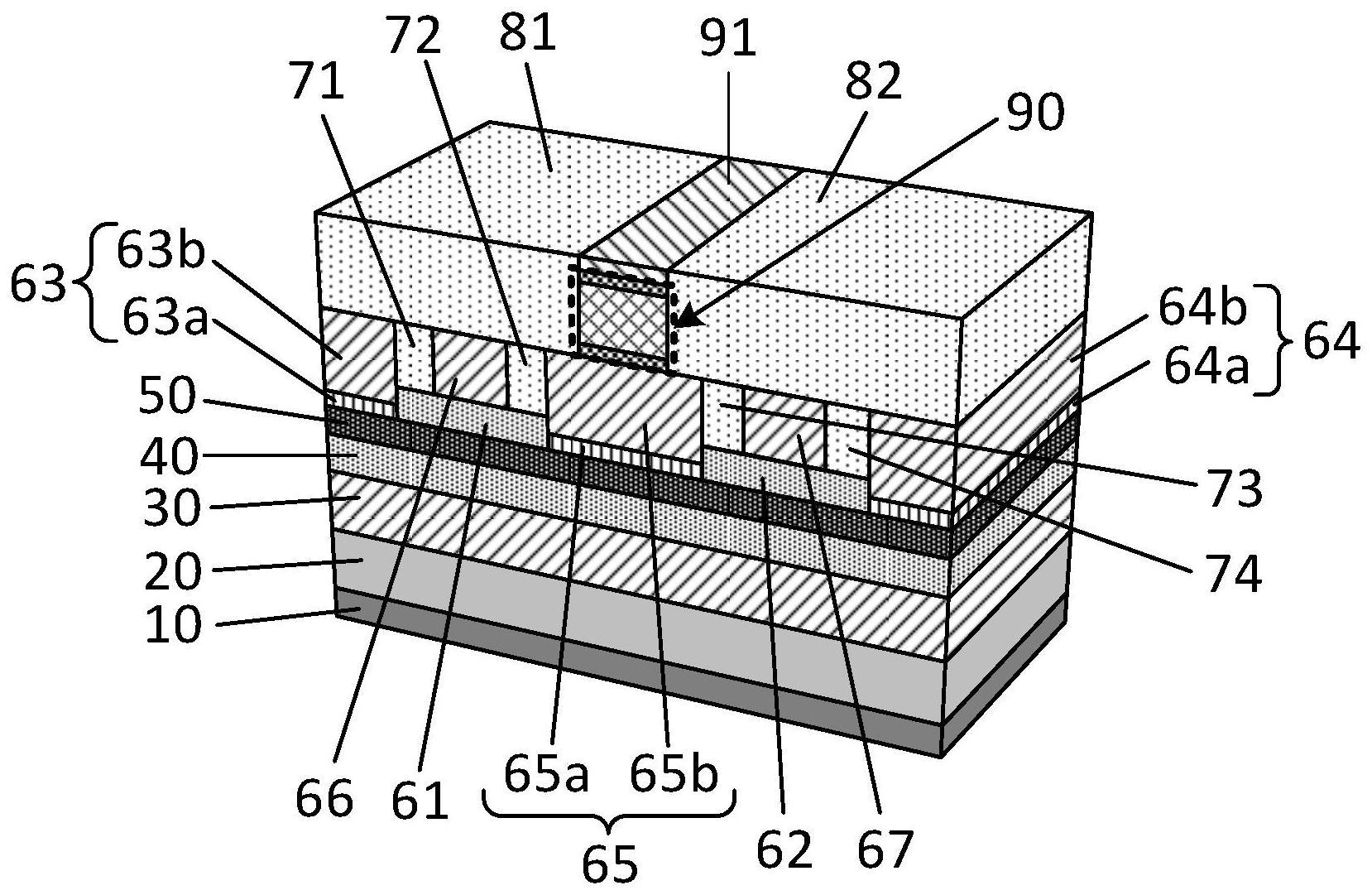

2、第一方面,本技术实施例提供了一种半导体结构,包括:

3、衬底;

4、背栅,位于衬底的一侧;

5、半导体层,位于背栅远离衬底的一侧,半导体层与背栅叠层设置且绝缘;

6、漏极,位于半导体层远离衬底的一侧,且在衬底上的正投影与半导体层在衬底上的正投影交叠;

7、磁性隧道结,位于漏极远离衬底的一侧,且与漏极接触;

8、位于半导体层远离衬底一侧的第一源极、第一栅极、第二源极和第二栅极,第一源极和第一栅极位于漏极的一侧,第二源极和第二栅极位于漏极的另一侧,且第一源极、第一栅极、第二源极和第二栅极分别在衬底上的正投影均与半导体层在衬底上的正投影交叠。

9、在一种可能的实现方式中,第一栅极和第二栅极关于漏极的垂直平分线对称设置;

10、第一源极和第二源极关于漏极的垂直平分线对称设置;

11、第一栅极和第二栅极靠近垂直平分线,第一源极和第二源极远离垂直平分线。

12、在一种可能的实现方式中,还包括:

13、第一绝缘介质层,位于第一源极与第一栅极之间;

14、第二绝缘介质层,位于第一栅极与漏极之间;

15、第三绝缘介质层,位于漏极与第二栅极之间;

16、第四绝缘介质层,位于第二栅极与第二源极之间;

17、第一栅介电层,位于背栅与半导体层之间;

18、第二栅介电层,位于第一栅极与半导体层之间;

19、第三栅介电层,位于第二栅极与半导体层之间。

20、在一种可能的实现方式中,第一源极、第二源极和漏极均包括两个导电层,且两个导电层叠层设置且接触。

21、在一种可能的实现方式中,半导体层的材料包括氧化铟镓锌。

22、在一种可能的实现方式中,还包括:位线,位于磁性隧道结远离衬底的一侧,且与磁性隧道结接触。

23、在一种可能的实现方式中,还包括:

24、第五绝缘介质层,位于第一源极和第一栅极远离衬底的一侧,且完全覆盖第一源极和第一栅极,且与磁性隧道结和位线接触;

25、第六绝缘介质层,位于第二源极和第二栅极远离衬底的一侧,且完全覆盖第二源极和第二栅极,且与磁性隧道结和位线接触;

26、第五绝缘介质层上表面和第六绝缘介质层的上表面,均与位线的上表面齐平。

27、第二方面,本技术实施例提供了一种存储器,包括如第一方面任一的半导体结构。

28、第三方面,本技术实施例提供了一种电子设备,包括如第二方面的存储器。

29、第四方面,本技术实施例提供了一种存储器的制作方法,包括:

30、提供一衬底;

31、在衬底的一侧依次制作背栅和半导体层;

32、在制作有半导体层的衬底上,制作第一源极、第一栅极、漏极、第二源极和第二栅极;第一源极和第一栅极位于漏极的一侧,第二源极和第二栅极位于漏极的另一侧,且第一源极、第一栅极、第二源极和第二栅极分别在衬底上的正投影均与半导体层在衬底上的正投影交叠;

33、在制作有第一源极、第一栅极、漏极、第二源极和第二栅极的衬底上,制作磁性隧道结;磁性隧道结与漏极接触。

34、在一种可能的实现方式中,在衬底的一侧依次制作背栅和半导体层,包括:

35、在衬底上依次沉积第一绝缘介质膜层、第一导电膜层、第一栅介电膜层、半导体膜层、第二栅介电膜层和第二绝缘介质膜层,形成背栅和半导体层。

36、在一种可能的实现方式中,在制作有半导体层的衬底上,制作第一源极、第一栅极、漏极、第二源极和第二栅极,包括:

37、基于图案化工艺,去除部分第二栅介电膜层和第二绝缘介质膜层,形成第一栅介电层、第二栅介电层、第一沟槽、第二沟槽和第三沟槽;其中,第一沟槽的位置与待形成第一源极的位置对应,第二沟槽的位置与待形成漏极的位置对应,第三沟槽的位置与待形成第二源极的位置对应,且第一沟槽、第二沟槽和第三沟槽的位置处均暴露出半导体层;

38、在第一沟槽、第二沟槽和第三沟槽内分别沉积第二导电膜层和第三导电膜层,形成第一源极、漏极和第二源极;

39、基于图案化工艺,去除部分第二绝缘介质膜层,形成暴露出部分第二栅介电膜层的第四沟槽和第五沟槽;

40、在第四沟槽和第五沟槽内沉积第四导电膜层,形成第一栅极和第二栅极;

41、沉积第三绝缘介质膜层。

42、在一种可能的实现方式中,还包括制作位线;以及在制作有第二栅极的衬底上,制作磁性隧道结和位线,具体包括:

43、基于图案化工艺,去除与漏极的位置对应位置处的部分第三绝缘介质膜层,形成暴露出部分漏极的第六沟槽;

44、在第六沟槽内依次沉积磁性隧道结膜层和第五导电膜层,形成磁性隧道结和位线。

45、本技术实施例提供的技术方案,至少具有如下有益效果:

46、本技术实施例提供的半导体结构包括一个磁性隧道结和两个晶体管,在衬底上依次设置背栅和半导体层,并在半导体层的上方,以及漏极的两侧分别设置一个栅极和一个源极,两个晶体管共用一个背栅,背栅控制两个晶体管的阈值电压,漏极两侧的两个栅极分别控制导电沟道的开启和关闭,能够实现存储单元较小的读出电流和较大的写入电流,相对于传统的mram存储单元,能够提升mram存储单元读写稳定性,减少读出电流和写入电流在器件结构尺寸需求上的冲突。具体的,当读出时,利用背栅控制两个晶体管的阈值电压,并通过其中一个栅极控制导电沟道开启,另一个栅极控制导电沟道关闭,使得一个晶体管开启,另一个晶体管关闭,其尺寸较小,读出电流较小,从而提高了读稳定性;而当写入时,利用背栅控制两个晶体管的阈值电压,并通过两个栅极均控制导电沟道开启,使得两个晶体管均开启,使得写入电流流经两个晶体管,从而增强了写入电流,提高了写稳定性。而且,由于两个晶体管共用一个背栅,能够节约面积,通过采用双栅控制,能够提高晶体管的控制能力,进一步提高读写稳定性。

47、本技术附加的方面和优点将在下面的描述中部分给出,这些将从下面的描述中变得明显,或通过本技术的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!