ETOXNOR型闪存器件及其制备方法与流程

本申请涉及闪存器件制造,具体涉及一种etox nor型闪存器件及其制备方法。

背景技术:

1、目前,etox nor型闪存器件的沟槽spacer(侧墙结构)loop采用典型的o-n-o-n(hto-sin1-teos-sin2)结构,结构相对较复杂,形成u型hto+l型sin1+弧形teos+弧形sin2的侧墙结构,后续还会去除弧形sin2,增大了furnace的产能(机台产能),也增加了对应(刻蚀)去除的流程,生产成本较大,cycle time(周期)较长。

2、etox nor型闪存器件x方向shrink(缩小)到更小节点(4xnm)时,y方向pitchshrink较多,为增大沟槽中的层间介质层填充窗口及ct工艺窗口,o-n-o-n四层膜层沉积的空间有限,过度沉积(沉积过厚的)hto-sin1-teos-sin2不利于存储区域器件的可靠性,也不利于外围逻辑区域mosfet器件承受hv generation电路及switch电路等电路的高压。

技术实现思路

1、本申请提供了一种etox nor型闪存器件及其制备方法,可以解决etox nor型闪存器件中,沟槽侧墙结构较为复杂导致生产成本较大以及生产周期较长、过厚的沟槽侧墙结构影响存储区域器件的可靠性,也影响外围逻辑区域mosfet器件承受hv generation电路及switch电路等电路的高压等问题中的至少一个问题。

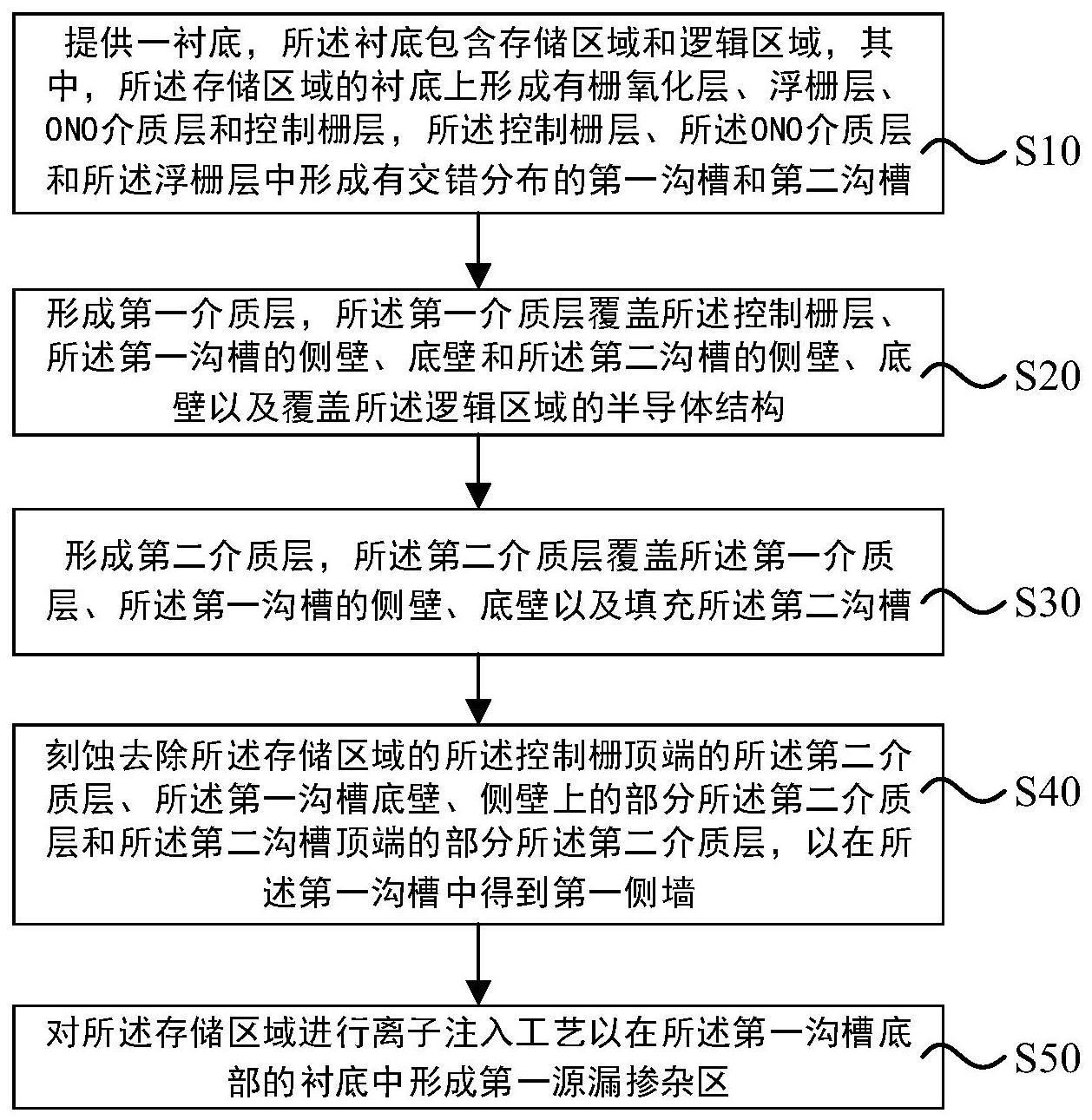

2、一方面,本申请实施例提供了一种etox nor型闪存器件的制备方法,包括:

3、提供一衬底,所述衬底包含存储区域和逻辑区域,其中,所述存储区域的衬底上形成有栅氧化层、浮栅层、ono介质层和控制栅层,所述控制栅层、所述ono介质层和所述浮栅层中形成有交错分布的第一沟槽和第二沟槽;

4、形成第一介质层,所述第一介质层覆盖所述控制栅层、所述第一沟槽的侧壁、底壁和所述第二沟槽的侧壁、底壁以及覆盖所述逻辑区域的半导体结构;

5、形成第二介质层,所述第二介质层覆盖所述第一介质层、所述第一沟槽的侧壁、底壁以及填充所述第二沟槽;

6、刻蚀去除所述存储区域的所述控制栅顶端的所述第二介质层、所述第一沟槽底壁、侧壁上的部分所述第二介质层和所述第二沟槽顶端的部分所述第二介质层,以在所述第一沟槽中得到第一侧墙;

7、对所述存储区域进行离子注入工艺以在所述第一沟槽底部的衬底中形成第一源漏掺杂区。

8、可选的,在所述etox nor型闪存器件的制备方法中,所述第一介质层的厚度为

9、可选的,在所述etox nor型闪存器件的制备方法中,所述第二介质层的厚度为

10、可选的,在所述etox nor型闪存器件的制备方法中,形成所述第一侧墙层之后,所述第一源漏掺杂区顶端的所述第一沟槽在宽度上的尺寸为

11、可选的,在所述etox nor型闪存器件的制备方法中,所述第一介质层为氧化硅层。

12、可选的,在所述etox nor型闪存器件的制备方法中,所述第二介质层为氮化硅层。

13、可选的,在所述etox nor型闪存器件的制备方法中,所述逻辑区域的半导体结构包括:所述栅氧化层和多晶硅栅极,所述栅氧化层覆盖所述逻辑区域的衬底,所述多晶硅栅极覆盖所述栅氧化层,所述多晶硅栅极中形成有多个间隔分布的第三沟槽。

14、可选的,在所述etox nor型闪存器件的制备方法中,在对所述存储区域进行离子注入工艺以在所述第一沟槽底部的衬底中形成第一源漏掺杂区之后,所述etox nor型闪存器件的制备方法还包括:

15、刻蚀去除所述逻辑区域的所述多晶硅栅极顶端的所述第二介质层和所述第一介质层、所述第三沟槽底壁、侧壁上的部分所述第二介质层,以在所述第三沟槽中得到第二侧墙;同时,刻蚀去除所述存储区域的所述控制栅顶端的所述第一介质层。

16、可选的,在所述etox nor型闪存器件的制备方法中,在形成所述第二侧墙之后,所述etox nor型闪存器件的制备方法还包括:

17、对所述逻辑区域进行离子注入工艺以在所述第三沟槽底部的衬底中形成第二源漏掺杂区。

18、另一方面,本申请实施例还提供了一种etox nor型闪存器件,包括:

19、衬底,所述衬底包含存储区域和逻辑区域,其中,所述存储区域的衬底上形成有栅氧化层、浮栅层、ono介质层和控制栅层,所述控制栅层、所述ono介质层和所述浮栅层中形成有交错分布的第一沟槽和第二沟槽;

20、第一介质层,所述第一介质层覆盖所述第一沟槽的侧壁、底壁和所述第二沟槽的侧壁、底壁以及覆盖所述逻辑区域的半导体结构;

21、第二介质层,所述第二介质层位于所述第二沟槽中;

22、第一侧墙,所述第一侧墙覆盖所述第一沟槽的侧壁和部分底壁;

23、第一源漏掺杂区,所述第一源漏掺杂区位于所述第一沟槽底部的衬底中。

24、本申请技术方案,至少包括如下优点:

25、本申请通过形成第一介质层和第二介质层,将第二沟槽(sas(self-alignsource)区域)填满;接着刻蚀去除存储区域的第一沟槽底壁、侧壁上的部分所述第二介质层以在所述第一沟槽中得到第一侧墙;最后对存储区域进行离子注入工艺以在第一沟槽底部的衬底中形成第一源漏掺杂区。本申请工艺简单,省去传统制备工艺中的侧墙结构的另外两层介质层淀积及相应的去除过程(步骤),降低了生产成本,缩短了器件制备周期。

26、进一步的,本申请制备方法中形成的第一侧墙的总厚度比传统制备工艺中形成的o-n-o-n结构的侧墙的总厚度薄,并且,本申请的第一侧墙底部没有传统制备工艺中的l型氮化硅,可以为后续在第一沟槽中填充介质层增加了填充窗口,同时,也增大了ct工艺窗口,利于小节点(4xnm node)etox nor型闪存器件的制造,也有利于存储区域器件的可靠性,也不影响外围逻辑区域mosfet器件承受hv generation电路及switch电路等电路的高压。

技术特征:

1.一种etox nor型闪存器件的制备方法,其特征在于,包括:

2.根据权利要求1所述的etox nor型闪存器件的制备方法,其特征在于,所述第一介质层的厚度为

3.根据权利要求1所述的etox nor型闪存器件的制备方法,其特征在于,所述第二介质层的厚度为

4.根据权利要求1所述的etox nor型闪存器件的制备方法,其特征在于,形成所述第一侧墙之后,所述第一源漏掺杂区顶端的所述第一沟槽在宽度上的尺寸为

5.根据权利要求1所述的etox nor型闪存器件的制备方法,其特征在于,所述第一介质层为氧化硅层。

6.根据权利要求1所述的etox nor型闪存器件的制备方法,其特征在于,所述第二介质层为氮化硅层。

7.根据权利要求1所述的etox nor型闪存器件的制备方法,其特征在于,所述逻辑区域的半导体结构包括:所述栅氧化层和多晶硅栅极,所述栅氧化层覆盖所述逻辑区域的衬底,所述多晶硅栅极覆盖所述栅氧化层,所述多晶硅栅极中形成有多个间隔分布的第三沟槽。

8.根据权利要求7所述的etox nor型闪存器件的制备方法,其特征在于,在对所述存储区域进行离子注入工艺以在所述第一沟槽底部的衬底中形成第一源漏掺杂区之后,所述etox nor型闪存器件的制备方法还包括:

9.根据权利要求8所述的etox nor型闪存器件的制备方法,其特征在于,在形成所述第二侧墙之后,所述etox nor型闪存器件的制备方法还包括:

10.一种etox nor型闪存器件,其特征在于,包括:

技术总结

本发明提供一种ETOX NOR型闪存器件及其制备方法,其中制备方法包括:提供包含存储区域和逻辑区域的衬底,存储区域的衬底上形成有栅氧化层、浮栅层、ONO介质层和控制栅层以及第一沟槽和第二沟槽;形成第一介质层;形成第二介质层;刻蚀去除存储区域的第一沟槽底壁、侧壁上的部分第二介质层以在第一沟槽中得到第一侧墙;对存储区域进行离子注入工艺以在第一沟槽底部的衬底中形成第一源漏掺杂区。本申请通过沉积第一介质层和第二介质层以将第二沟槽填满,并减薄第二介质层以在第一沟槽中得到第一侧墙,本申请工艺简单,省去传统制备工艺中的侧墙结构中的另外两层介质层淀积及相应的去除步骤,降低了生产成本,缩短了器件制备周期。

技术研发人员:杜怡行,王壮壮,姚春,王虎

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!