电平移位器电路、相应的装置和方法与流程

本说明书涉及电平移位器电路,并且更具体地涉及基于电容器的电平移位器电路。

背景技术:

1、通过使用高达电平移位器电路中的缓冲器的最大电压范围两倍的低压器件,可以优化缓冲器的性能和面积。共源共栅结构通常用于扩展涉及驱动电压的快速移位的金属氧化物半导体(mos)器件的电压范围。可以使用升压时钟将电压移位应用于共源共栅缓冲器。然而,这种方法很难适用于连续模式。

技术实现思路

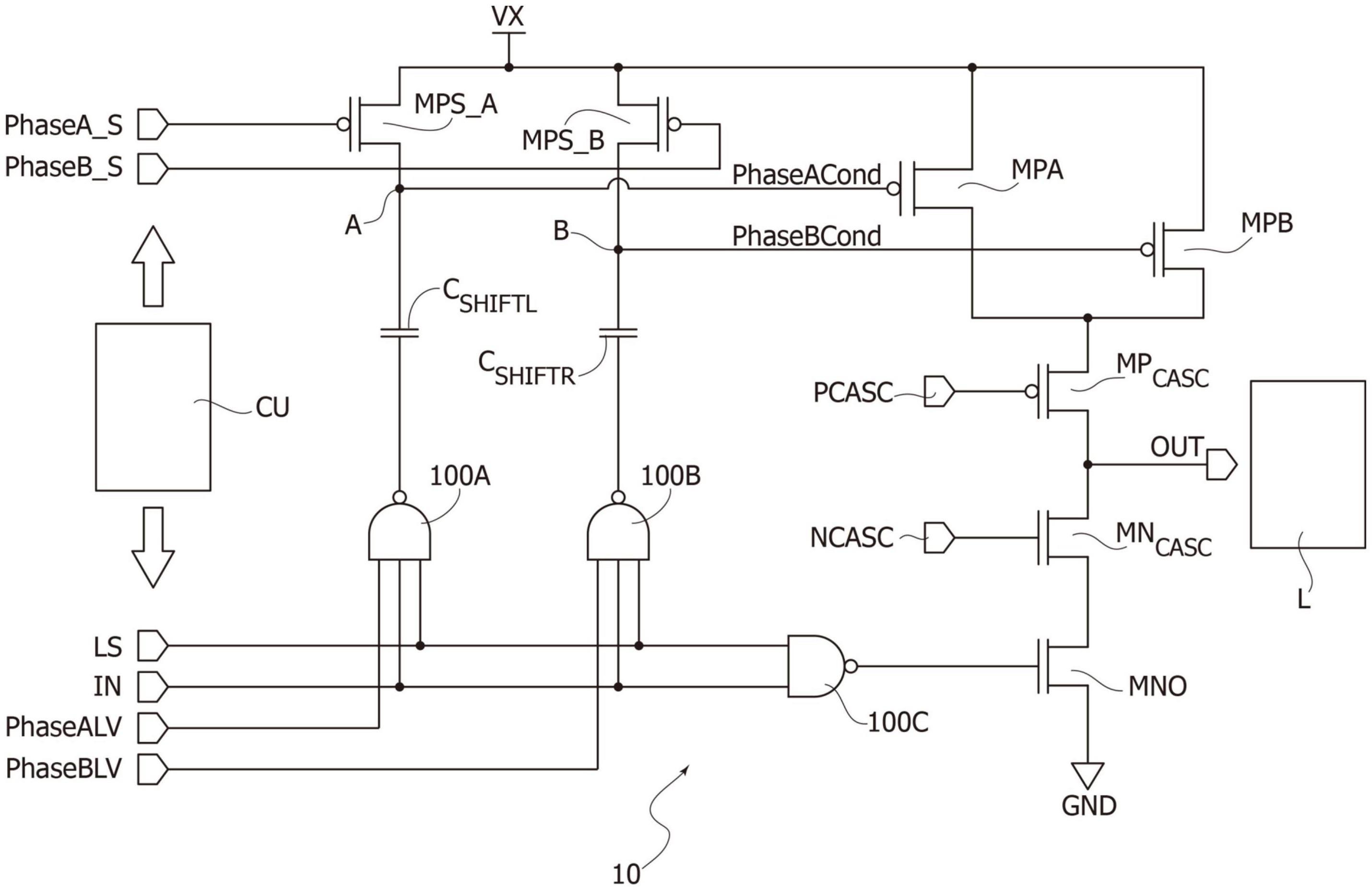

1、在一个实施例中,一种装置包括:至少一个输入节点,被配置为接收在输入电平域中的输入信号;输出电路。所述输出电路包括:输出节点,被配置为提供输出电平域中的输出信号,其中,所述输出电平域相对于所述输入电平域移位;第一驱动节点,被配置为接收第一逻辑信号;第二驱动节点,被配置为接收第二逻辑信号,其中,所述输出信号根据所述第一逻辑信号和所述第二逻辑信号中的至少一个而具有所述输出电平域中的第一输出电平或第二输出电平。所述装置包括:第一移位电容器,耦合到所述第一驱动节点;第二移位电容器,耦合到所述第二驱动节点;电容器刷新电路。所述电容器刷新电路包括:第一刷新晶体管,具有控制端子以及穿过所述第一刷新晶体管的第一刷新电流路径,第一刷新电流路径经由所述第一驱动节点位于电源节点和所述第一移位电容器之间,所述第一刷新电流路径被配置为响应于施加到所述第一刷新晶体管的控制端子的第一刷新信号而变得导通。所述电容器刷新电路包括:第一逻辑电路,被配置为响应于第一移位刷新信号,促进经由所述第一刷新电流路径对所述第一移位电容器的充电,所述第一移位刷新信号相对于施加到所述第一刷新晶体管的控制端子的第一刷新信号移位。所述电容器刷新电路包括:第二刷新晶体管,具有控制端子以及穿过所述第二刷新晶体管的第二刷新电流路径,所述第二刷新电流路径经由所述第二驱动节点位于电源节点和所述第二移位电容器之,所述第二刷新电流路径被配置为响应于施加到所述第二刷新晶体管的控制端子的第二刷新信号而变得导通。所述电容器刷新电路包括:第二逻辑电路,被配置为响应于第二移位刷新信号,促进经由所述第二刷新电流路径对所述第二移位电容器的充电,所述第二移位刷新信号相对于施加到所述第二刷新晶体管的控制端子的第二刷新信号移位。

2、在一个实施例中,一种方法包括:利用电路的输入节点接收输入电平域中的输入信号;利用所述电路的输出电路的输出节点提供输出电平域中的输出信号,所述输出电平域相对于所述输入电平域移位;利用所述输出电路的第一驱动节点接收第一逻辑信号。所述方法包括:利用所述输出电路的第二驱动节点接收第二逻辑信号,其中,所述输出信号根据所述第一逻辑信号和所述第二逻辑信号中的至少一个而具有所述输出电平域中的第一输出电平或第二输出电平;通过将第一刷新信号施加到第一刷新晶体管的控制端子,使所述第一刷新晶体管的第一刷新电流路径导通,所述第一刷新电流路径耦合在电源节点和第一移位电容器之间,所述第一移位电容器耦合到所述第一驱动节点。所述方法包括:利用第一逻辑电路,响应于相对于所述第一刷新信号移位的第一移位刷新信号,经由所述第一刷新电流路径对所述第一移位电容器充电;通过将第二刷新信号施加到第二刷新晶体管的控制端子,使所述第二刷新晶体管的第二刷新电流路径导通,所述第二刷新电流路径耦合在所述电源节点与第二移位电容器之间,所述第二移位电容器耦合到所述第二驱动节点。所述方法包括:利用第二逻辑电路,响应于相对于所述第二刷新信号移位的第二移位刷新信号,经由所述第二刷新电流路径对所述第一移位电容器充电。

3、在一个实施例中,一种装置包括:输入节点,被配置为接收输入电平域中的输入信号;电源端子,被配置为提供电源电压;输出电路。所述输出电路包括:第一共源共栅晶体管;第二共源共栅晶体管;第一驱动晶体管,耦合在高电源节点和所述第一共源共栅晶体管之间,并且具有被配置为接收第一逻辑信号的控制端子。所述输出电路包括:第二驱动晶体管,与所述第一驱动晶体管并联耦合,并且具有被配置为接收第二逻辑信号的控制端子;输出节点,耦合在所述第一共源共栅晶体管和所述第二共源共栅晶体管之间,并且被配置为提供输出电平域中的输出信号,所述输出电平域相对于所述输入电平域移位。

4、在一个实施例中,诸如通用(gp)微控制器的低压电子装置使用连续操作模式。

5、本文中呈现的示例有助于电容电平移位中的连续操作模式,其中,在用于将输入电压传播到例如更高电压域的电容器上产生移位电压。

6、本文中呈现的示例涉及在共源共栅缓冲器的情况下,为两个p沟道金属氧化物半导体(pmos)晶体管,或在电压域移位的情况下,为与非端口。

7、在这两种情况下,电容器上的电压以在输入信号和刷新时钟之间没有施加严格的同步约束的方式刷新。

8、可以仅使用低电压(lv)mos组件来实施这里呈现的示例。

9、由于电容器移位,这有利于有效的电压域变化和移位电压的快速传播时间。

10、由于不响应电平移位而出现交叉开关(crossbar)电流,因此同样有助于实现低功耗。

技术特征:

1.一种装置,包括:

2.根据权利要求1所述的装置,其中所述第一逻辑电路包括第一逻辑门,所述第一逻辑门被配置为接收所述第一移位刷新信号作为输入,其中所述第一移位电容器位于所述第一驱动节点和所述第一逻辑门的中间,其中所述第二逻辑电路包括第二逻辑门,所述第二逻辑门被配置为接收所述第二移位刷新信号作为输入,其中所述第二移位电容器位于所述第二驱动节点和所述第二逻辑门的中间。

3.根据权利要求1所述的装置,其中所述第一逻辑电路包括接收所述第一移位刷新信号作为输入的第一与非门,其中所述第二逻辑电路包括接收所述第二移位刷新信号作为输入的第二与非门。

4.根据权利要求1所述的装置,包括:

5.根据权利要求4所述的装置,其中位于电源节点与参考节点之间的所述电流线路包括穿过第三驱动晶体管的电流路径,所述第三驱动晶体管位于所述第二共源共栅晶体管和所述参考节点的中间,穿过所述第三驱动晶体管的所述电流路径响应于所述输入信号被断言而变为导通。

6.根据权利要求1所述的装置,其中所述输出电路包括输出逻辑门,所述输出逻辑门具有逻辑输入,所述逻辑输入耦合到所述第一驱动节点和所述第二驱动节点,以从所述第一驱动节点和所述第二驱动节点接收所述第一逻辑信号和所述第二逻辑信号,其中所述输出信号响应于所述第一逻辑信号和所述第二逻辑信号中的至少一个逻辑信号被断言而具有所述输出电平域中的所述第一输出电平或所述第二输出电平。

7.根据权利要求6所述的装置,其中所述输出逻辑门被布置在电源节点与参考节点之间,其中所述电源节点和所述参考节点提供相对于所述输入电平域移位的所述输出电平域中的所述第一输出电平和所述第二输出电平。

8.根据权利要求6所述的装置,其中所述输出逻辑门包括与非门,所述与非门具有逻辑输入,所述与非门的逻辑输入耦合到所述第一驱动节点和所述第二驱动节点,以从所述第一驱动节点和所述第二驱动节点接收所述第一逻辑信号和所述第二逻辑信号。

9.根据权利要求1所述的装置,其中所述电容器刷新电路被配置为使所述第一刷新晶体管和所述第二刷新晶体管交替导通,其中:

10.根据权利要求1所述的装置,其中所述电容器刷新电路被配置为防止所述第一刷新晶体管和所述第二刷新晶体管同时导通。

11.根据权利要求1所述的装置,包括电负载,所述电负载耦合到所述输出电路中的所述输出节点,以从所述输出节点接收相对于所述输入电平域移位的所述输出电平域中的所述输出信号。

12.一种方法,包括:

13.根据权利要求12所述的方法,包括交替地使所述第一刷新晶体管和所述第二刷新晶体管导通。

14.根据权利要求13所述的方法,其中在所述第一刷新晶体管导通的情况下,所述第一移位电容器的第一端子经由所述第一驱动节点被耦合到所述电源节点,所述第一移位电容器的第二端子被所述第一逻辑电路带到高逻辑值,其中在所述第二刷新晶体管导通的情况下,所述第二移位电容器的第一端子经由所述第二驱动节点被耦合到所述电源节点,所述第二移位电容器的第二端子被所述第二逻辑电路带到高逻辑值。

15.一种装置,包括:

16.根据权利要求15所述的装置,包括:

17.根据权利要求16所述的装置,包括:

18.根据权利要求17所述的装置,其中所述第一逻辑电路包括第一与非门,并且所述第二逻辑电路包括第二与非门。

19.根据权利要求15所述的装置,其中所述输出电路包括耦合在所述第二共源共栅晶体管与地之间的低侧驱动器晶体管。

20.根据权利要求15所述的装置,包括耦合到所述输出节点的负载。

技术总结

电平移位器电路接收输入电平域中的一个或多个输入信号,并且包括在输出节点处提供相对于所述输入电平域移位的输出电平域中的输出信号。所述电路包括输出电路,所述输出电路包括接收第一逻辑信号和第二逻辑信号的第一驱动节点和第二驱动节点,使得所述输出信号根据第一逻辑信号和第二逻辑信号中的至少一个而具有输出电平域中的第一输出电平或第二输出电平。所述电路包括耦合到第一驱动节点和第二驱动节点的第一移位电容器和第二移位电容器以及电容器刷新电路。

技术研发人员:A·康特,M·鲁塔,M·彼萨萨勒,T·茹阿诺

受保护的技术使用者:意法半导体股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!