一种半导体结构及其制备方法与流程

本公开涉及半导体,尤其涉及一种半导体结构及其制备方法。

背景技术:

1、三维存储器(3d nand)由于高存储密度、高稳定性和成熟的制备工艺而成为存储器闪存的主流结构,但是三维存储器在刻蚀时,由于对准问题,底部常出现没有打开的情况,导致沟道(channel)电流下降,甚至源极线(source line)断开的情况,随着3d nand堆叠层数的增加,这一情况变的尤为严重,亟需新的方法解决。

技术实现思路

1、有鉴于此,本公开实施例提供一种半导体结构及其制备方法。

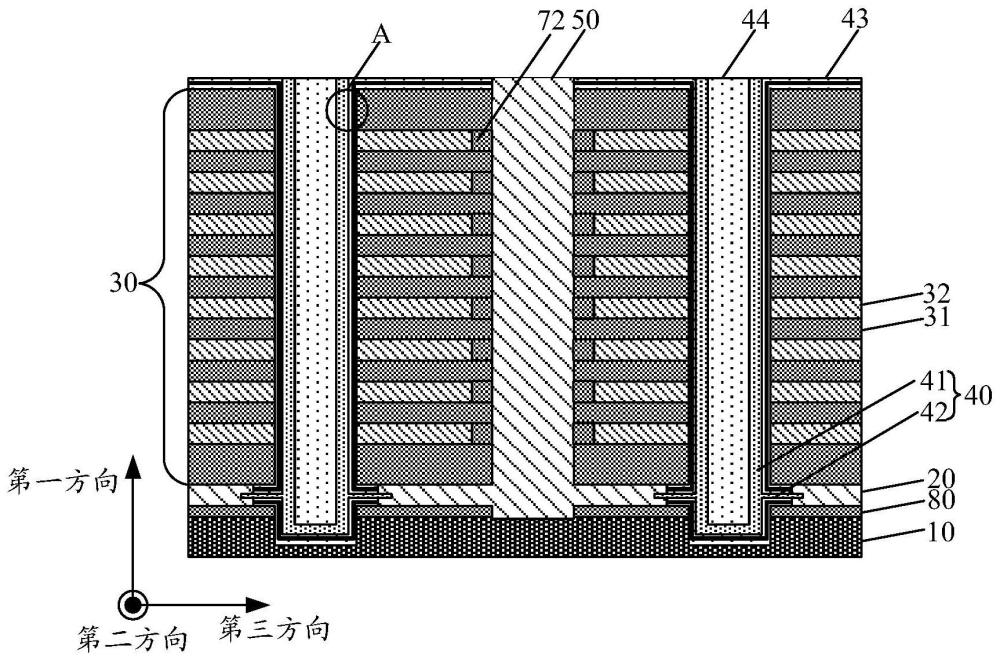

2、根据本公开实施例的第一方面,提供了一种半导体结构,包括:

3、衬底;

4、位于所述衬底上的叠层结构;

5、第一沟道层,所述第一沟道层形成在所述叠层结构中,且沿所述第一方向延伸,所述叠层结构环绕所述第一沟道层,其中,所述第一方向为垂直于所述衬底平面的方向;

6、第二沟道层,所述第二沟道层在所述第一方向上贯穿所述叠层结构;

7、连接层,所述连接层位于所述衬底与所述叠层结构之间,所述第一沟道层同时形成在所述连接层中,所述第一沟道层和所述第二沟道层通过所述连接层连接。

8、在一些实施例中,所述第一沟道层包括第一子部和第二子部,所述第一子部在所述第一方向上贯穿所述叠层结构,所述第二子部沿横向形成在所述连接层中,且与所述连接层连接。

9、在一些实施例中,还包括:

10、功能层,所述功能层形成在所述叠层结构中,且沿所述第一方向延伸,并位于所述叠层结构和所述第一沟道层之间;

11、所述功能层包括沿所述第一沟道层的径向向内的方向依次设置的阻挡层、电荷存储层和隧穿层。

12、在一些实施例中,还包括:

13、第一绝缘层,位于所述衬底和所述连接层之间。

14、在一些实施例中,所述叠层结构包括交替堆叠的支撑层和栅极层;

15、所述半导体结构还包括:第二绝缘层,位于所述栅极层靠近所述第二沟道层的一端。

16、在一些实施例中,还包括:

17、外延层,位于所述第二沟道层的下方,与所述第二沟道层接触连接。

18、在一些实施例中,所述第二沟道层与所述连接层的材料相同。

19、根据本公开实施例的第二方面,提供一种半导体结构的制备方法,包括:

20、提供衬底;

21、在所述衬底上依次形成初始连接层和初始叠层结构;

22、沿第一方向刻蚀所述初始叠层结构和所述初始连接层,形成第一沟道孔,其中,所述第一方向为垂直于所述衬底平面的方向;

23、沿横向刻蚀所述第一沟道孔两侧的部分所述初始连接层,形成第二沟道孔;

24、在所述第一沟道孔和所述第二沟道孔内形成第一沟道层;

25、沿所述第一方向刻蚀所述初始叠层结构和所述初始连接层,形成第一沟槽;

26、去除所述初始连接层,形成第一间隙;

27、在同一步骤中,在所述第一间隙内形成连接层,以及在所述第一沟槽内形成第二沟道层,所述第一沟道层和所述第二沟道层通过所述连接层连接。

28、在一些实施例中,还包括:

29、在形成所述第一沟道层之前,形成功能层;所述形成功能层包括:

30、形成覆盖所述第一沟道孔和所述第二沟道孔表面的阻挡层;

31、形成覆盖所述阻挡层的表面电荷存储层;

32、形成覆盖所述电荷存储层表面的隧穿层。

33、在一些实施例中,所述第一沟道层包括位于所述第一沟道孔内的第一子部和位于所述第二沟道孔内的第二子部;

34、所述方法还包括:在形成所述第一间隙后,去除所述第二沟道孔内的部分所述功能层,暴露所述第二沟道孔内的所述第二子部,以使所述第二子部与所述连接层连接。

35、在一些实施例中,还包括:

36、在形成所述初始连接层和所述初始叠层结构之前,在所述衬底上形成第一绝缘层。

37、在一些实施例中,所述初始叠层结构包括交替堆叠的支撑层和牺牲层;

38、所述方法还包括:

39、在形成所述第一沟槽之后;

40、刻蚀去除所述初始叠层结构中的所述牺牲层,形成第二间隙;

41、在所述第一沟槽和所述第二间隙内形成初始栅极结构;

42、回刻蚀去除所述第一沟槽内的所述初始栅极结构,以及所述第二间隙内的部分所述初始栅极结构,以使所述第二间隙内保留的所述初始栅极结构形成为栅极层;其中,所述栅极层和所述支撑层形成为叠层结构。

43、在一些实施例中,还包括:

44、在所述第二间隙被回刻蚀去除部分所述初始栅极结构处形成第二绝缘层。

45、在一些实施例中,所述第一沟槽暴露出所述衬底的部分表面和所述初始连接层的部分表面;

46、所述方法还包括:

47、在形成所述第一沟槽之后,在暴露出的所述衬底的表面以及暴露出的所述初始连接层的表面形成第四绝缘层。

48、在一些实施例中,还包括:

49、在形成所述第二沟道层之前,在所述第一沟槽的底部形成外延层;所述外延层与所述第二沟道层连接。

50、本公开实施例中,第一沟道层也形成在连接层中,并通过连接层连接第一沟道层和第二沟道层,使第一沟道层和第二沟道层并不通过衬底进行连接,如此,避免了底部衬底没有打开,导致第一沟道层和第二沟道层与衬底连接存在问题,进而引起沟道电流下降,以及源极线断开的情况。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,

3.根据权利要求1所述的半导体结构,其特征在于,还包括:

4.根据权利要求1所述的半导体结构,其特征在于,还包括:

5.根据权利要求1所述的半导体结构,其特征在于,

6.根据权利要求1所述的半导体结构,其特征在于,还包括:

7.根据权利要求1所述的半导体结构,其特征在于,

8.一种半导体结构的制备方法,其特征在于,包括:

9.根据权利要求8所述的方法,其特征在于,还包括:

10.根据权利要求9所述的方法,其特征在于,

11.根据权利要求8所述的方法,其特征在于,还包括:

12.根据权利要求8所述的方法,其特征在于,

13.根据权利要求12所述的方法,其特征在于,还包括:

14.根据权利要求8所述的方法,其特征在于,

15.根据权利要求8所述的方法,其特征在于,还包括:

技术总结

本公开实施例公开了一种半导体结构及其制备方法,其中,半导体结构包括:衬底;位于衬底上的叠层结构;第一沟道层,第一沟道层形成在叠层结构中,且沿第一方向延伸,叠层结构环绕第一沟道层,其中,第一方向为垂直于衬底平面的方向;第二沟道层,第二沟道层在第一方向上贯穿叠层结构;连接层,连接层位于衬底与叠层结构之间,第一沟道层同时形成在连接层中,第一沟道层和第二沟道层通过连接层连接。

技术研发人员:郭帅,刘忠明

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/11/18

- 还没有人留言评论。精彩留言会获得点赞!