半导体结构及其制造方法、存储系统与流程

本申请涉及半导体,更具体地,涉及半导体结构及制造半导体结构的方法、存储系统。

背景技术:

1、随着人工智能、大数据、物联网、移动通信、移动设备和云存储领域的兴起和发展,对诸如三维半导体存储器件等半导体结构的存储密度的要求也越来越高,然而随着半导体结构中堆叠层数的增加,沟道孔的刻蚀深度也相应地增加,这对沟道孔的刻蚀工艺提出了更高的要求。

技术实现思路

1、本申请提出的实施方式可解决或部分解决上述背景技术部分提出的不足或现有技术中的其它不足。

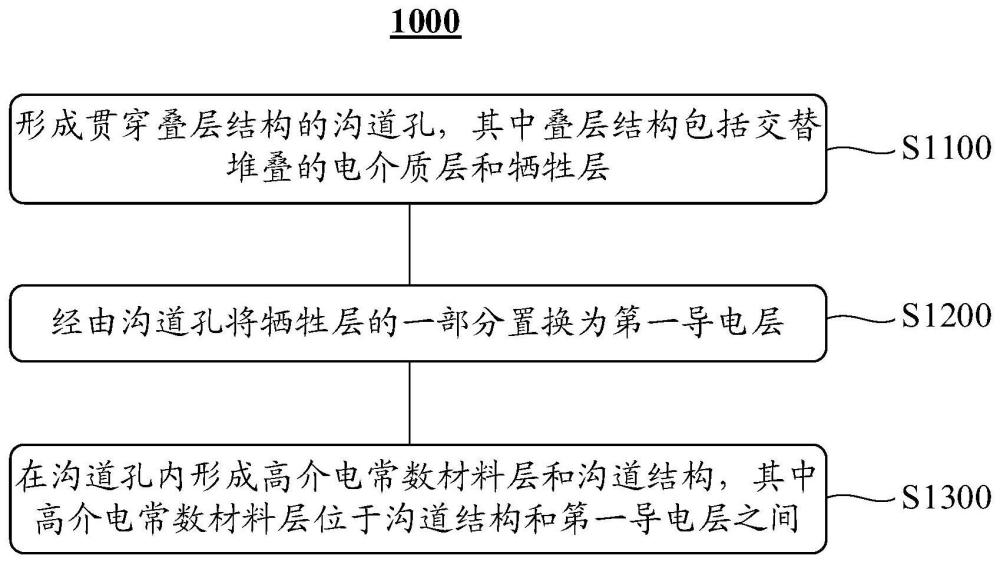

2、本申请提供了一种制造半导体结构的方法。该方法包括:形成贯穿叠层结构的沟道孔,其中所述叠层结构包括交替堆叠的电介质层和牺牲层;经由所述沟道孔将所述牺牲层的一部分置换为第一导电层;以及在所述沟道孔内形成高介电常数材料层和沟道结构,其中所述高介电常数材料层位于所述沟道结构和所述第一导电层之间。

3、在一个实施方式中,经由所述沟道孔将所述牺牲层的一部分置换为第一导电层,包括:经由所述沟道孔回刻所述牺牲层,并在去除部分所述牺牲层所形成的空隙内形成第一导电层。

4、在一个实施方式中,所述牺牲层的材料包括半导体材料,经由所述沟道孔将所述牺牲层的一部分置换为第一导电层,包括:在所述沟道孔内形成与所述牺牲层接触的过渡导电层,其中所述过渡导电层与所述牺牲层的一部分反应生成第一导电层;以及去除所述过渡导电层。

5、在一个实施方式中,所述牺牲层靠近所述过渡导电层的部分,与所述过渡导电层反应并改变为所述第一导电层。

6、在一个实施方式中,所述方法还包括:形成贯穿所述叠层结构的栅极间隙;经由所述栅极间隙去除剩余的所述牺牲层,形成牺牲间隙;以及在所述牺牲间隙内形成第二导电层,所述第二导电层与所述第一导电层连接。

7、在一个实施方式中,所述第二导电层和所述第一导电层的材料包括金属。

8、在一个实施方式中,所述方法还包括:形成贯穿所述叠层结构的栅极间隙;经由所述栅极间隙去除剩余的所述牺牲层的至少一部分,形成牺牲间隙;以及在所述牺牲间隙内形成第二导电层。

9、在一个实施方式中,所述第一导电层的材料包括金属硅化物。

10、在一个实施方式中,在所述沟道孔内形成高介电常数材料层和沟道结构,包括:在所述沟道孔的内壁上形成所述高介电常数材料层;以及在所述高介电常数材料层的内侧形成所述沟道结构,其中所述沟道结构由外向内依次包括:阻挡层、电荷捕获层、隧穿层和沟道层。

11、在一个实施方式中,在所述牺牲间隙内形成第二导电层,包括:在所述牺牲间隙内依次形成阻隔层和所述第二导电层,其中所述阻隔层位于所述电介质层和所述第二导电层之间。

12、在一个实施方式中,所述方法还包括:经由所述栅极间隙回刻所述第二导电层,并在回刻的所述第二导电层的部分填充绝缘材料。

13、在一个实施方式中,在去除所述牺牲层所形成的空隙内形成第一导电层,包括:在去除所述牺牲层所形成的空隙内依次形成隔离层和第一导电层,其中所述隔离层位于所述电介质层和所述第一导电层之间。

14、本申请另一方面提供了一种半导体结构。该半导体结构包括:堆叠结构,包括交替堆叠的电介质层和栅极层;多个沟道结构,贯穿所述堆叠结构;以及高介电常数材料层,位于所述沟道结构和所述堆叠结构之间,且沿堆叠方向延伸。

15、在一个实施方式中,所述栅极层由金属材料形成。

16、在一个实施方式中,所述半导体结构还包括:位于所述栅极层和所述电介质层之间的阻隔层。

17、在一个实施方式中,所述栅极层的第一部分环绕所述高介电常数材料层,所述第一部分与所述栅极层的其它部分的材料不同。

18、在一个实施方式中,所述第一部分的材料包括金属硅化物。

19、在一个实施方式中,所述其它部分包括:第二部分,与所述第一部分连接,其中所述第二部分的材料包括金属。

20、在一个实施方式中,所述半导体结构还包括贯穿所述堆叠结构的栅极间隙结构,所述其它部分包括:第二部分,靠近所述栅极间隙结构,其中所述第二部分的材料包括金属,所述其它部分的剩余部分的材料包括多晶硅。

21、在一个实施方式中,所述半导体结构还包括:位于所述其它部分和所述电介质层之间的阻隔层。

22、本申请另一方面提供了一种存储系统,该存储系统包括至少一个三维存储器,每个所述三维存储器包括如上述的半导体结构;以及控制器,耦接至所述半导体结构,用于控制所述三维存储器存储数据。

23、在本申请的一个或多个实施方式中,通过在沟道孔内形成高介电常数材料层和沟道结构,既有利于增大沟道孔的工艺窗口,增加沟道孔贯穿的叠层结构的堆叠数量,降低深孔刻蚀的工艺难度;又有利于将高介电常数材料层用作沟道结构和后续由牺牲层置换形成的第二导电层之间的隔离层,可以减少第二导电层的电子泄露,提高半导体结构的可靠性。

24、在本申请的一个或多个实施方式中,通过将牺牲层的一部分置换为第一导电层,既有利于将第一导电层用作后续去除牺牲层的刻蚀停止层,以减小在去除牺牲层的过程中对高介电常数材料层造成损坏;又有利于将第一导电层用作后续用于控制每一层存储单元的控制栅的一部分。

技术特征:

1.一种制造半导体结构的方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,经由所述沟道孔将所述牺牲层的一部分置换为第一导电层,包括:

3.根据权利要求1所述的方法,其特征在于,所述牺牲层的材料包括半导体材料,经由所述沟道孔将所述牺牲层的一部分置换为第一导电层,包括:

4.根据权利要求3所述的方法,其特征在于,所述牺牲层靠近所述过渡导电层的部分,与所述过渡导电层反应并改变为所述第一导电层。

5.根据权利要求2所述的方法,其特征在于,所述方法还包括:

6.根据权利要求5所述的方法,其特征在于,所述第二导电层和所述第一导电层的材料包括金属。

7.根据权利要求3所述的方法,其特征在于,所述方法还包括:

8.根据权利要求7所述的方法,其特征在于,所述第一导电层的材料包括金属硅化物。

9.根据权利要求1-8中任一项所述的方法,其特征在于,在所述沟道孔内形成高介电常数材料层和沟道结构,包括:

10.根据权利要求5或7所述的方法,其特征在于,在所述牺牲间隙内形成第二导电层,包括:

11.根据权利要求5或7所述的方法,其特征在于,所述方法还包括:

12.根据权利要求2所述的方法,其特征在于,在去除所述牺牲层所形成的空隙内形成第一导电层,包括:

13.一种半导体结构,其特征在于,包括:

14.根据权利要求13所述的半导体结构,其特征在于,所述栅极层由金属材料形成。

15.根据权利要求14所述的半导体结构,其特征在于,所述半导体结构还包括:

16.根据权利要求13所述的半导体结构,其特征在于,所述栅极层的第一部分环绕所述高介电常数材料层,所述第一部分与所述栅极层的其它部分的材料不同。

17.根据权利要求16所述的半导体结构,其特征在于,所述第一部分的材料包括金属硅化物。

18.根据权利要求16所述的半导体结构,其特征在于,所述其它部分包括:

19.根据权利要求16所述的半导体结构,其特征在于,所述半导体结构还包括贯穿所述堆叠结构的栅极间隙结构,所述其它部分包括:

20.根据权利要求16所述的半导体结构,其特征在于,所述半导体结构还包括:

21.一种存储系统,其特征在于,包括:

技术总结

本申请提供了一种半导体结构及其制造方法、存储系统。该制造半导体结构的方法包括:形成贯穿叠层结构的沟道孔,其中所述叠层结构包括交替堆叠的电介质层和牺牲层;经由所述沟道孔将所述牺牲层的一部分置换为第一导电层;以及在所述沟道孔内形成高介电常数材料层和沟道结构,其中所述高介电常数材料层位于所述沟道结构和所述第一导电层之间。

技术研发人员:谢景涛,颜丙杰,王迪,周文犀

受保护的技术使用者:长江存储科技有限责任公司

技术研发日:

技术公布日:2024/11/26

- 还没有人留言评论。精彩留言会获得点赞!