半导体装置的制作方法

本公开的示例实施例涉及一种半导体装置。

背景技术:

1、正在开发能够在需要数据存储的数据存储系统中存储大容量数据的半导体装置,并且研究了增加半导体装置的数据存储容量的方法。例如,作为增加半导体装置的数据存储容量的方法,已提出了包括三维布置的存储器单元而非二维布置的存储器单元的半导体装置。

技术实现思路

1、本公开的示例实施例是提供一种具有改进的集成密度和大规模生产率的半导体装置。

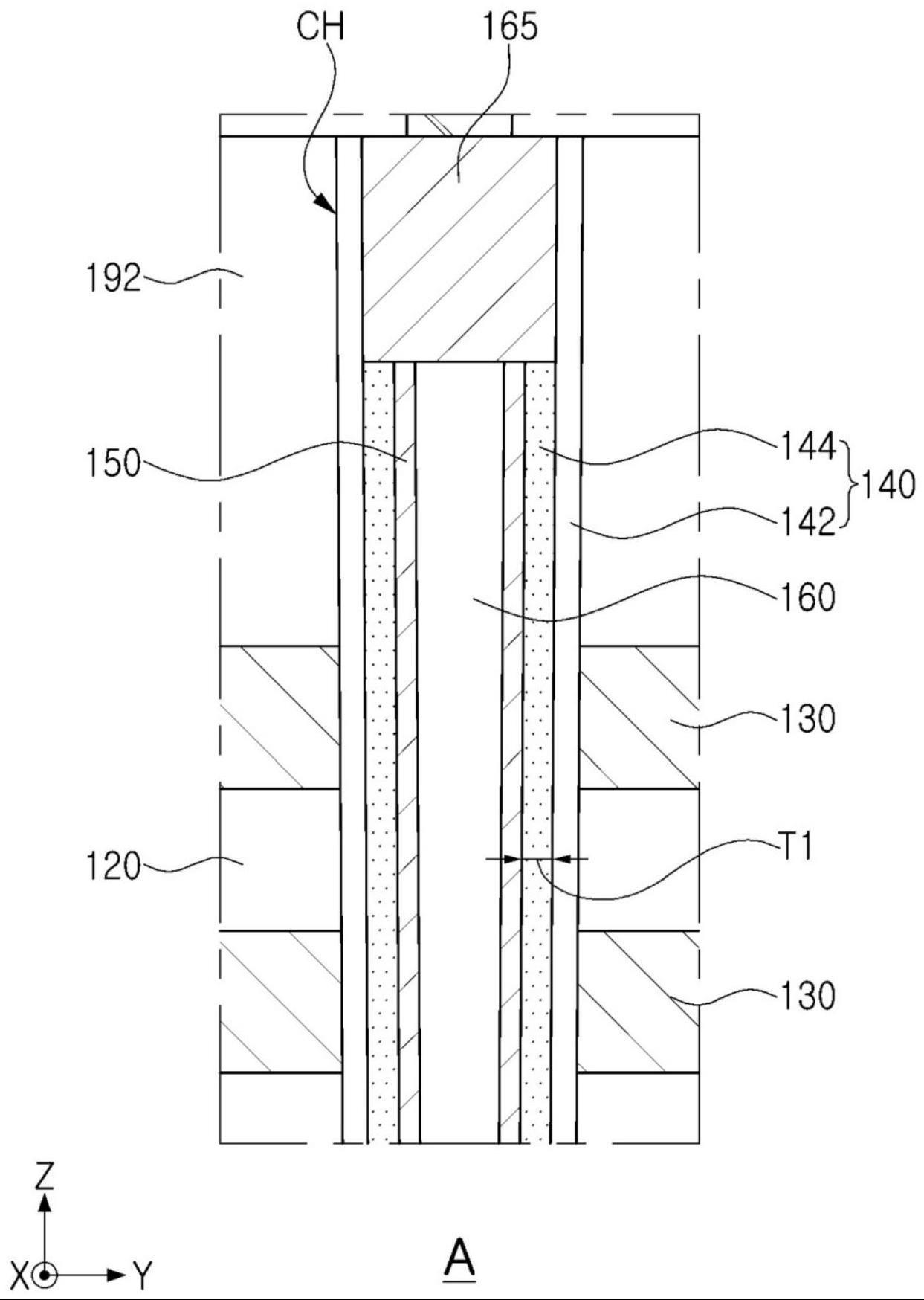

2、根据本公开的示例实施例,一种半导体装置包括源极结构、在源极结构上的多个栅电极。多个栅电极中的栅电极在垂直于源极结构的上表面的第一方向上堆叠并彼此间隔开,并且在垂直于第一方向的第二方向上延伸。沟道结构在穿过多个栅电极并在第一方向上延伸的沟道孔中,该沟道结构包括在沟道孔的侧壁上的第一介电层、在第一介电层的与沟道孔的侧壁相对的内侧表面上的第二介电层、在第二介电层的与沟道孔的侧壁相对的内侧表面上的沟道层以及在沟道层的与沟道孔的侧壁相对的内侧表面上的填充绝缘层,并且还包括在包括沟道孔的上端的区域中的沟道焊盘层,其中,第二介电层包括铁电材料,并且其中,沟道焊盘层与第一介电层的内侧表面接触并且覆盖第二介电层的上表面、沟道层的上表面和填充绝缘层的上表面。

3、根据本公开的示例实施例,一种半导体装置包括源极结构、在源极结构上的多个栅电极。多个栅电极中的栅电极在垂直于源极结构的上表面的竖直方向上堆叠并彼此间隔开,并且沟道结构在穿过栅电极并在竖直方向上延伸的沟道孔中,其中,沟道结构包括在竖直方向上延伸并包括铁电材料或反铁电材料的介电层、在介电层的内侧上的沟道层以及在沟道孔的上端中的沟道焊盘层,其中,介电层的上端在比沟道焊盘层的上表面的水平低的水平上。

4、根据本公开的示例实施例,一种半导体装置包括板层、在板层上的多个栅电极。多个栅电极中的栅电极在垂直于板层的上表面的竖直方向上堆叠并彼此间隔开,并且沟道结构在穿过栅电极延伸并在竖直方向上延伸的沟道孔中,其中,沟道结构包括在竖直方向上延伸并包括铁电材料的介电层、在介电层的内侧上的沟道层以及在沟道孔的上端中并与介电层的上表面接触的沟道焊盘层,并且其中,使用介电层的极化状态来写入数据。

技术特征:

1.一种半导体装置,包括:

2.根据权利要求1所述的半导体装置,其中,所述第一介电层延伸到所述沟道孔的所述上端。

3.根据权利要求1所述的半导体装置,其中,至少所述第二介电层的上端包括氯。

4.根据权利要求1所述的半导体装置,其中,所述第二介电层的上端与所述填充绝缘层的上端实质上共面。

5.根据权利要求1所述的半导体装置,其中,所述第二介电层的上表面、所述沟道层的上表面和所述填充绝缘层的上表面彼此共面。

6.根据权利要求1所述的半导体装置,其中,所述第二介电层包括与所述第一介电层的材料不同的材料。

7.根据权利要求1所述的半导体装置,其中,所述第一介电层具有第一硬度,并且所述第二介电层具有大于所述第一硬度的第二硬度。

8.根据权利要求1所述的半导体装置,其中,所述填充绝缘层具有第一硬度,并且所述第二介电层具有大于所述第一硬度的第二硬度。

9.根据权利要求1所述的半导体装置,其中,所述第二介电层包括铪、锆、硅、钇、铝、钆、锶、镧、钛、钪和它们的氧化物中的至少一种。

10.根据权利要求1所述的半导体装置,其中,所述第二介电层沿着所述沟道孔的周边的厚度在1nm至30nm的范围内。

11.根据权利要求1所述的半导体装置,其中,所述沟道焊盘层的下表面在比所述多个栅电极中的最上面的栅电极的上表面的水平高的水平上。

12.根据权利要求1所述的半导体装置,其中,所述沟道结构还包括插置在所述第二介电层和所述沟道层之间的第三介电层。

13.根据权利要求1所述的半导体装置,其中,所述沟道结构还包括在所述第二介电层和所述沟道层之间的电荷存储层和隧穿层,所述隧穿层与所述第二介电层相对地在电荷存储层上。

14.根据权利要求1所述的半导体装置,还包括:

15.一种半导体装置,包括:

16.根据权利要求15所述的半导体装置,其中,所述沟道层和所述沟道焊盘层中的至少一个在所述介电层的上表面上。

17.根据权利要求15所述的半导体装置,其中,所述介电层在包括所述介电层的上端的第一区域中包括氯,并且在包括所述介电层的下端的第二区域中不包括氯。

18.根据权利要求15所述的半导体装置,其中,所述介电层包括掺杂有锆、硅、钇、铝、钆、锶、镧和钪中的至少一种的氧化铪。

19.一种半导体装置,包括:

20.根据权利要求19所述的半导体装置,其中,所述介电层的上端在比所述沟道焊盘层的上表面的水平低的水平上,并且在比所述多个栅电极中的最上面的栅电极的上表面的水平高的水平上。

技术总结

一种半导体装置包括源极结构、在源极结构上的多个栅电极。多个栅电极在第一方向上堆叠并彼此间隔开并且在垂直于第一方向的第二方向上延伸,并且沟道孔中的沟道结构穿过多个栅电极并在第一方向上延伸,该沟道结构包括沟道孔的侧壁上的第一介电层、与沟道孔的侧壁相对地在第一介电层上的第二介电层、与沟道孔的侧壁相对地在第二介电层上的沟道层以及与沟道孔的侧壁相对地在沟道层上的填充绝缘层,并且沟道结构还包括在包括沟道孔的上端的区域中的沟道焊盘层,其中,第二介电层包括铁电材料,并且其中,沟道焊盘层与第一介电层的内侧表面接触并且覆盖第二介电层的上表面、沟道层的上表面和填充绝缘层的上表面。

技术研发人员:金兑泳,金容锡

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!