三维存储器装置的解码器架构的制作方法

涉及三维存储器装置的解码器架构。

背景技术:

1、存储器装置广泛用于将信息存储在例如计算机、用户装置、无线通信装置、相机、数字显示器等各种电子装置中。通过将存储器装置内的存储器单元编程为各种状态来存储信息。举例来说,二进制存储器单元可编程为两个支持状态中的一个,经常由逻辑1或逻辑0表示。在一些实例中,单个存储器单元可支持多于两个状态,其中的任一状态可被存储。为了存取所存储信息,组件可读取(例如,感测、检测、检索、识别、确定、评估)存储器装置中的所存储状态。为了存储信息,组件可在存储器装置中写入(例如,编程、设置、指定)状态。

2、存在各种类型的存储器装置和存储器单元,包含磁性硬盘、随机存取存储器(ram)、只读存储器(rom)、动态ram(dram)、同步动态ram(sdram)、静态ram(sram)、铁电ram(feram)、磁性ram(mram)、电阻式ram(rram)、快闪存储器、相变存储器(pcm)、自选存储器、硫族化物存储器技术等。可关于易失性配置或非易失性配置描述存储器单元。以非易失性配置进行配置的存储器单元即使在没有外部电源的情况下也可在很长一段时间内维持所存储逻辑状态。以易失性配置进行配置的存储器单元可能在与外部电源断开连接时失去所存储状态。

技术实现思路

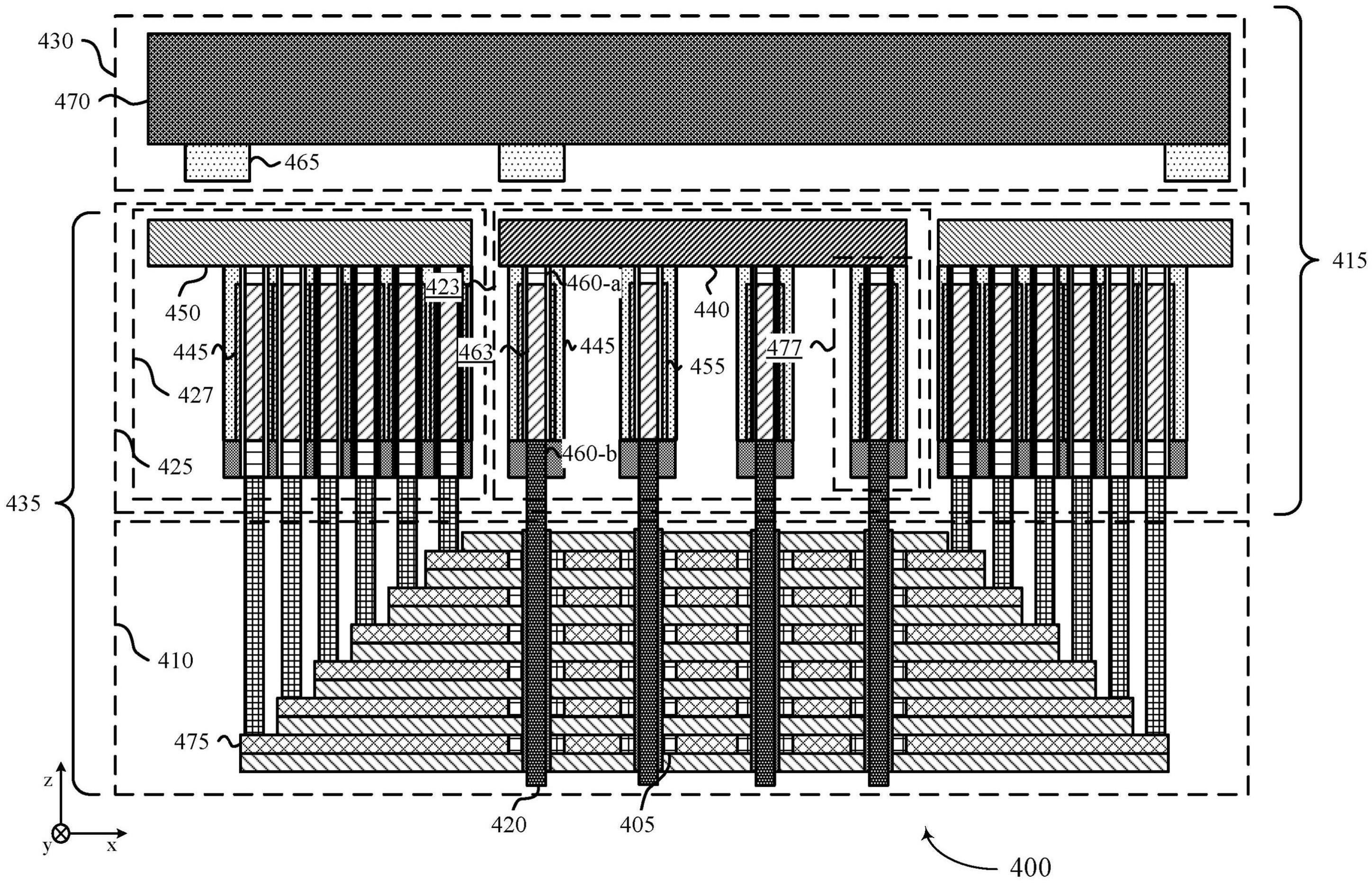

1、描述一种设备。所述设备可包含:第一半导体装置,其包括布置于层级中的多个字线板和延伸穿过多个字线板的多个导电柱,所述第一半导体装置包括:第一多个垂直晶体管,所述第一多个垂直晶体管中的每一垂直晶体管选择性地耦合相应导电柱与多个数字线中的相应数字线;第二多个垂直晶体管,所述第二多个垂直晶体管中的每一垂直晶体管选择性地耦合相应字线板与多个电压源中的相应电压源;及多个第一接点,所述多个第一接点的第一子集与第一多个垂直晶体管耦合,且所述多个第一接点的第二子集与第二多个垂直晶体管耦合;及第二半导体装置,其包括形成于第二半导体装置的半导体衬底内的一或多个逻辑电路,所述第二半导体装置包括:多个第二接点;及第三多个晶体管,所述第三多个晶体管的至少一个子集具有与多个第二接点耦合的端子,第一半导体装置的多个第一接点与第二半导体装置的多个第二接点接合。

2、描述一种设备。所述设备可包含:存储器阵列的多个字线板,其布置于多个层级中,每一字线板包括在第一水平方向上延伸的一或多个字线部件;多个导电柱,其延伸穿过多个字线板,其中,在多个层级的每一字线板处,存储器阵列的一或多个存储器单元与相应导电柱和字线板的相应部件耦合;多个数字线,其在正交于第一水平方向的第二水平方向上延伸;及解码器,其沿着垂直方向从多个层级偏移且配置成对多个导电柱和多个字线板进行偏置,所述解码器包括:第一部分,其包括至少部分地形成于半导体衬底内且与操作存储器阵列相关联的一或多个逻辑电路;及第二部分,其沿着垂直方向定位于解码器的第一部分与存储器阵列之间,解码器的第二部分包括配置成耦合相应导电柱与相应数字线的第一多个解码元件和配置成耦合字线板与多个电压源中的相应电压源的第二多个解码元件。

3、描述一种方法。所述方法可包含:形成分层组合件,所述分层组合件包括存储器阵列的布置于多个层级中的多个字线板,每一字线板包括在第一水平方向上延伸的一或多个字线部件、延伸穿过多个字线板的多个导电柱,和与多个字线板耦合且在正交于第一水平方向的第二水平方向上延伸的多个数字线;在分层组合件上方在第一衬底中形成解码器的第一部分,解码器的第一部分包括配置成耦合相应导电柱与相应数字线的第一多个解码元件,和配置成耦合相应字线板与多个电压源中的相应电压源和多个第一接点的第二多个解码元件,每一第一接点与第一多个解码元件的相应子集或与第二多个解码元件的相应子集耦合;在第二衬底中形成解码器的第二部分,解码器的第二部分包括多个第二接点和多个晶体管,所述多个晶体管的至少一个子集具有与多个第二接点耦合的端子;及接合多个第一接点中的每一第一接点与多个第二接点中的相应第二接点,其中所述接合将解码器的第一部分定位于分层组合件与解码器的第二部分之间。

技术特征:

1.一种设备,其包括:

2.根据权利要求1所述的设备,其中所述第一半导体装置进一步包括:

3.根据权利要求2所述的设备,其中所述第一多个垂直晶体管中的每一垂直晶体管包括与所述多个导电柱中的相应导电柱耦合的第一端子、与所述多个数字线中的相应数字线耦合的第二端子和与所述第一多个栅极线中的相应栅极线耦合的栅极。

4.根据权利要求2所述的设备,其中所述第二多个垂直晶体管中的每一垂直晶体管包括与所述多个字线板中的字线板的相应部分耦合的第一端子、与所述多个电压源中的相应电压源耦合的第二端子和与所述第二多个栅极线中的相应栅极线耦合的栅极。

5.根据权利要求2所述的设备,其中所述第一半导体装置进一步包括第三多个垂直晶体管,所述第三多个垂直晶体管中的每一垂直晶体管选择性地耦合字线板的相应部分与相应接地源。

6.根据权利要求2所述的设备,其中:

7.根据权利要求2所述的设备,其中:

8.根据权利要求7所述的设备,其中所述多个第一接点包括在所述第一水平方向上延伸的第一行接点,所述第一行接点中的每一第一接点耦合所述第一多个栅极线中的相应栅极线与所述多个第二接点中的相应第二接点,所述多个第一接点进一步包括在所述第二水平方向上延伸的第一列接点,所述第一列接点中的每一第一接点耦合所述多个数字线中的相应数字线与所述多个第二接点中的相应第二接点。

9.根据权利要求8所述的设备,其中所述多个第一接点进一步包括在所述第一水平方向上延伸的第二行接点,所述第二行接点中的每一第一接点耦合所述第二多个栅极线中的相应栅极线与所述多个第二接点中的相应第二接点,所述多个第一接点进一步包括在所述第二水平方向上延伸的第二列接点,所述第二列接点中的每一第一接点耦合所述多个电压源中的相应电压源与所述多个第二接点中的相应第二接点。

10.根据权利要求1所述的设备,其中所述多个第一接点的数量小于所述第一多个垂直晶体管的数量与所述第二多个垂直晶体管的数量的总和。

11.根据权利要求1所述的设备,其中所述第一多个垂直晶体管中的每一垂直晶体管和所述第二多个垂直晶体管中的每一晶体管包括相应薄膜晶体管tft。

12.一种设备,其包括:

13.根据权利要求12所述的设备,其中所述解码器进一步包括:

14.根据权利要求13所述的设备,其中所述第一多个解码元件中的每一解码元件包括相应垂直晶体管,所述相应垂直晶体管具有与所述多个导电柱中的相应导电柱耦合的第一端子、与所述多个数字线中的相应数字线耦合的第二端子和与所述第一多个栅极线中的相应栅极线耦合的栅极。

15.根据权利要求13所述的设备,其中所述第二多个解码元件中的每一解码元件包括相应垂直晶体管,所述相应垂直晶体管具有与所述多个字线板中的字线板的相应部分耦合的第一端子、与所述多个电压源中的相应电压源耦合的第二端子和与所述第二多个栅极线中的相应栅极线耦合的栅极。

16.根据权利要求13所述的设备,其中所述第二多个解码元件中的每一解码元件包括相应第一垂直晶体管和相应第二垂直晶体管,所述相应第一垂直晶体管具有与所述多个字线板中的字线板的相应部分耦合的第一端子、与所述多个电压源中的相应电压源耦合的第二端子和与所述第二多个栅极线中的相应栅极线耦合的栅极,且所述相应第二垂直晶体管具有与所述多个字线板中的字线板的相应部分耦合的第一端子、与相应接地源耦合的第二端子和与所述第二多个栅极线中的相应栅极线耦合的栅极。

17.根据权利要求13所述的设备,其中:

18.根据权利要求13所述的设备,其中:

19.根据权利要求18所述的设备,其中:

20.根据权利要求13所述的设备,其中所述第一多个接点的数量小于所述第一多个解码元件的数量。

21.根据权利要求13所述的设备,其中所述第二多个接点的数量小于所述第二多个解码元件的数量。

22.一种方法,其包括:

23.根据权利要求22所述的方法,其中形成所述解码器的所述第一部分包括:

24.根据权利要求23所述的方法,其中形成所述解码器的所述第一部分进一步包括:

25.根据权利要求22所述的方法,其中所述第一多个解码元件布置于第一网格结构中,所述第一网格结构包括在所述第一水平方向上延伸的一或多个行和在正交于所述第一水平方向的所述第二水平方向上延伸的一或多个列;且所述第二多个解码元件布置于第二网格结构中,所述第二网格结构包括在所述第一水平方向上延伸的一或多个行和在所述第二水平方向上延伸的一或多个列。

技术总结

本申请涉及三维存储器装置的解码器架构。在一些情况下,存储器装置的解码器可包含两个部分。所述解码器的第一部分可制造于所述存储器阵列的顶部,且可包含对与所述存储器阵列的导电柱耦合的第一解码元件阵列进行选择性偏置的柱解码部分和对与所述存储器阵列的字线耦合的第二解码元件阵列进行选择性偏置的字线解码部分。所述解码器的第二部分可实施于单独半导体装置中,所述半导体装置可包含配置成将信号驱动到一组接点的一组逻辑电路,所述一组接点接合到所述第一部分的接点以驱动数字线、电压源和栅极线。

技术研发人员:L·弗拉汀,F·佩里兹,P·凡蒂尼

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!