存储器胞元中的介电工程隧道区域的制作方法

本公开的实施例大体来说涉及电子装置及系统,且更具体来说,涉及电子装置及系统的存储器胞元及其形成。

背景技术:

1、存储器装置通常经提供作为计算机或其它电子装置中的内部半导体集成电路。存在许多不同类型的存储器,包含易失性及非易失性存储器。易失性存储器需要电力来维持其数据,且包含随机存取存储器(ram)、动态随机存取存储器(dram)、静态ram(sram)或同步动态随机存取存储器(sdram),以及其它存储器。非易失性存储器在未通电时可保留所存储数据,且包含快闪存储器、只读存储器(rom)、电可擦除可编程rom(eeprom)、可擦除可编程rom(eprom)、电阻可变存储器,例如相变随机存取存储器(pcram)、电阻式随机存取存储器(rram)、磁阻随机存取存储器(mram),或三维(3d)xpointtm存储器,以及其它存储器。

2、快闪存储器用作用于广泛范围的电子应用的非易失性存储器。快闪存储器装置通常包含允许高存储器密度、高可靠性及低功率消耗的一或多个组单晶体管、浮动栅极或电荷俘获存储器胞元。两种常见类型的快闪存储器阵列架构包含“与非”及“或非”架构,以布置每一个的基本存储器胞元配置的逻辑形式命名。存储器阵列的存储器胞元通常布置成矩阵。在实例中,阵列的行中的每一浮动栅极存储器胞元的栅极耦合到接入线(例如,字线)。在“或非”架构中,阵列的列中的每一存储器胞元的漏极耦合到数据线(例如,位线)。在“与非”架构中,阵列的串中的每一存储器胞元的漏极在源极线与数据线之间以源极到漏极串联耦合在一起。对存储器装置或其它装置中的存储器胞元的结构或设计的改进可提供存储器装置的更高质量的操作,例如关于读取、编程及保留。

技术实现思路

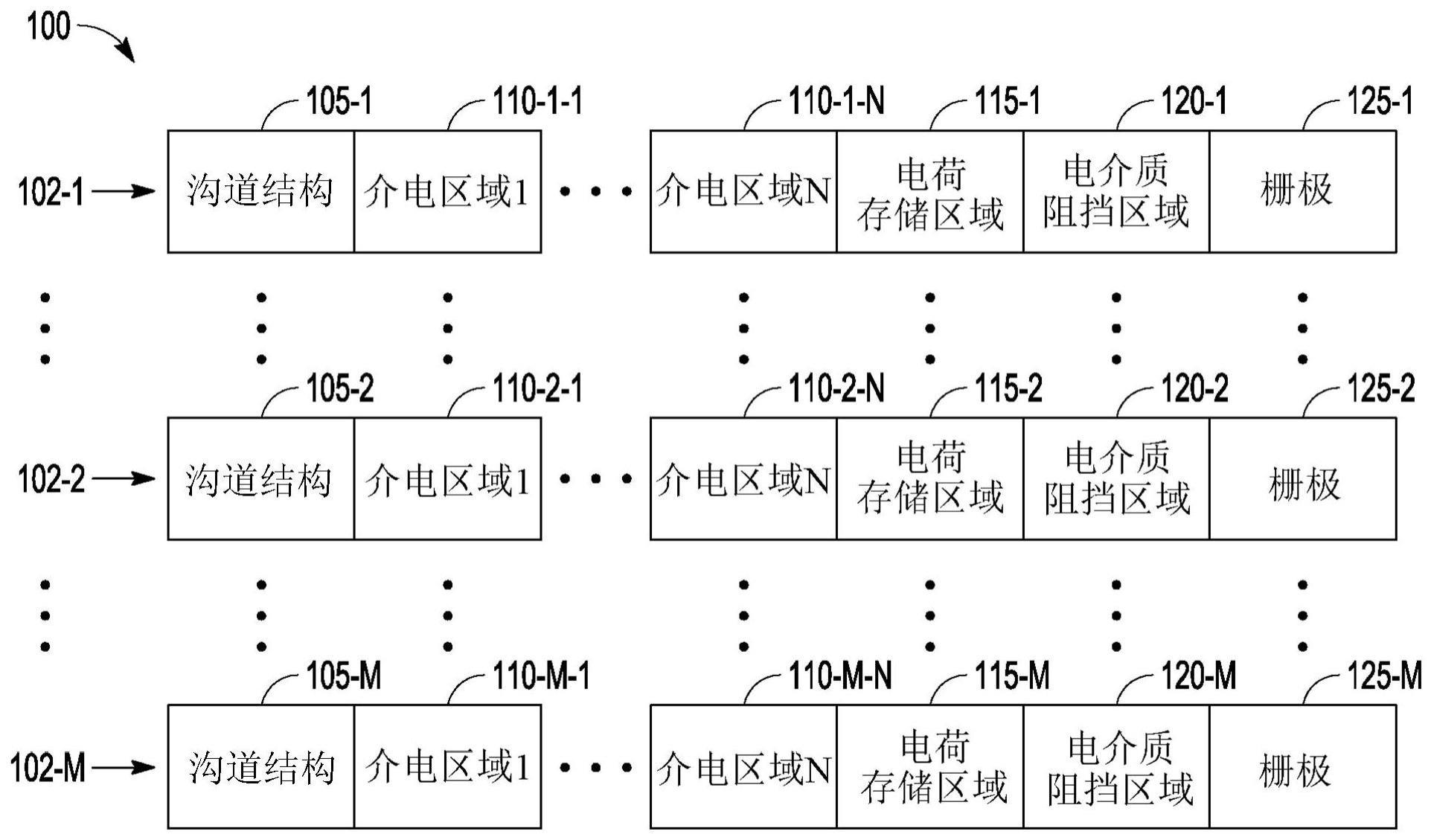

1、本公开的方面是针对一种存储器装置,其包括:存储器胞元阵列,每一存储器胞元具有电荷存储区域,所述电荷存储区域通过隧道区域与沟道结构分离,所述隧道区域具有多个区域,所述多个区域包含:第一介电区域,其邻近并接触所述沟道结构,所述第一介电区域的材料不同于氧化硅且介电常数小于氮化硅的介电常数;一或多个额外介电区域,其位于所述第一介电区域与所述电荷存储区域之间,所述一或多个额外介电区域包含介电常数大于氮化硅的介电常数的第二介电区域。

2、本公开的另一方面是针对一种存储器装置,其包括:存储器胞元阵列,每一存储器胞元具有电荷存储区域,所述电荷存储区域通过隧道区域与沟道结构分离,所述隧道区域具有多个区域,所述多个区域包含:第一介电区域,其具有深电荷陷阱,所述第一介电区域邻近并接触所述电荷存储区域;及一或多个额外介电区域,其位于所述第一介电区域与所述沟道结构之间,所述一或多个额外介电区域包含掺杂介电区域。

3、本公开的又一方面是针对一种存储器装置,其包括:存储器胞元阵列,每一存储器胞元具有电荷存储区域,所述电荷存储区域通过隧道区域与沟道结构分离,所述隧道区域具有多个区域,所述多个区域包含:氮氧化硅区域,其邻近并接触所述电荷存储区域;及氧化硅区域,其邻近并接触所述沟道结构。

技术特征:

1.一种存储器装置,其包括:

2.根据权利要求1所述的存储器装置,其中所述第一介电区域具有所述隧道区域的所述多个区域中的最低介电常数。

3.根据权利要求1所述的存储器装置,其中所述一或多个额外介电区域包含位于所述第一介电区域与所述第二介电区域之间的第三介电区域,所述第三介电区域的材料为成分含量与所述第一介电区域的所述材料不同的掺杂氮氧化硅。

4.根据权利要求3所述的存储器装置,其中所述第一介电区域包含掺杂有碳或硼的氮氧化硅,且所述第三介电区域的所述掺杂氮氧化硅掺杂有碳或硼,所述第三介电区域的氮含量不同于所述第一介电区域。

5.根据权利要求1所述的存储器装置,其中所述第二介电区域邻近并接触所述第一介电区域且所述一或多个额外介电区域包含位于所述第二介电区域与所述电荷存储区域之间的第三介电区域及第四介电区域,所述第三介电区域及所述第四介电区域的介电常数彼此不同且小于氮化硅的介电常数。

6.根据权利要求1所述的存储器装置,其中:

7.根据权利要求1所述的存储器装置,其中所述一或多个额外介电区域包含介电非金属氧化物区域,其中每一介电非金属氧化物区域的材料包含掺杂有碳或硼的氮氧化硅,其中不同介电非金属氧化物区域中的氮氧化硅具有不同氮分布或不同掺杂分布。

8.根据权利要求1所述的存储器装置,其中所述第二介电区域包含金属氧化物。

9.根据权利要求8所述的存储器装置,其中所述第二介电区域的材料包含介电单金属氧化物或介电双金属氧化物。

10.根据权利要求9所述的存储器装置,其中所述单金属氧化物或双金属氧化物中的金属包含铪、锆或铝中的一或多者。

11.一种存储器装置,其包括:

12.根据权利要求11所述的存储器装置,其中所述掺杂介电区域包含具有不同浓度的掺杂剂的电介质。

13.根据权利要求12所述的存储器装置,其中具有不同浓度的掺杂剂的所述电介质包含掺杂有碳的氮氧化硅,所述氮氧化硅在所述掺杂介电区域中具有不同浓度的氮。

14.根据权利要求11所述的存储器装置,其中所述一或多个额外介电区域包含第二掺杂介电区域,所述第二掺杂介电区域的氮含量与所述掺杂介电区域不同。

15.根据权利要求11所述的存储器装置,其中所述一或多个额外介电区域包含第二掺杂介电区域及第三掺杂介电区域,所述第二掺杂介电区域及所述第三掺杂介电区域中的每一者的氮含量与所述掺杂介电区域不同,所述第二掺杂介电区域的氮含量与所述第三掺杂介电区域不同。

16.根据权利要求11所述的存储器装置,其中所述第一介电区域包含具有深电荷陷阱的氮氧化硅。

17.根据权利要求16所述的存储器装置,其中所述深电荷陷阱与以掺杂剂水平掺杂有碳或硼的氮氧化硅相关联以产生所述深电荷陷阱。

18.一种存储器装置,其包括:

19.根据权利要求18所述的存储器装置,其中所述氧化硅区域的厚度等于或小于所述氮氧化硅区域的厚度的二分之一。

20.根据权利要求18所述的存储器装置,其中所述氧化硅区域的厚度等于或小于所述氮氧化硅区域的厚度的三分之一。

21.根据权利要求18所述的存储器装置,其中所述氮氧化硅区域包含具有不同氮浓度的多个氮氧化硅子区域。

22.根据权利要求18所述的存储器装置,其中所述电荷存储区域包含氮化硅且所述沟道结构包含多晶硅。

技术总结

本公开涉及一种存储器胞元中的介电工程隧道区域。多种应用可包含具有存储器胞元的存储器装置,其中每一存储器胞元可具有位于所述存储器胞元的沟道结构与所述存储器胞元的电荷存储区域之间的工程隧道区域。所述工程隧道区域可针对所述存储器区域的经改进读取、编程及保留操作。在各种实施例中,所述工程隧道区域可通过插入介电常数相对于氮化硅较低的材料及介电常数相对于氮化硅较高的材料具有多个具有界定常数调制的介电区域。在各种实施例中,存储器胞元的所述工程隧道区域可具有多个介电区域,其中材料在所述存储器胞元的所述电荷存储区域附近具有深陷阱。公开了其它工程隧道区域。

技术研发人员:安在勇,T·H·金,M·西迪克

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!