一种新型交叉连接双模冗余抗辐照TSPC触发器

本发明涉及电路,具体涉及到一种新型交叉连接双模冗余抗辐照的tspc触发器。

背景技术:

1、特征尺寸的持续减小和节点寄生电容的减小导致了由于空间辐射而在芯片上发生单事件瞬变(set)的更高概率。sets是由宇宙中的高能粒子引起的,当它们穿过硅衬底时,这些粒子可以电离额外的电子-空穴对。这些电子-空穴对将被电路的敏感节点收集,导致敏感节点电压的瞬时突变。当瞬态信号的幅度太大或持续时间太长时,可能会导致单事件翻转(seu)。与仅在敏感节点处生成电压小故障的set不同,seu是一种软错误,它使锁存器反转并锁定,直到下一次电路刷新。虽然seu不会对系统造成灾难性损坏,但也可能导致系统故障。因此,最先进的微处理机必须采取相关保护措施,以避免seu的发生。

2、冗余是设计rhbd类型d触发器时常用的一种技术。三模冗余(tmr)是最著名的冗余拓扑之一,具有较强的冗余鲁棒性。tmr结构将电路分成三个模块,它们同时执行相同的操作,以多数相同的输出作为系统的最终输出,由于两个模块同时出现set或seu事件概率极小,故可以大大提高系统的可信度,tmr的缺点是芯片面积和功耗增加了两倍。另一种常用的冗余技术为双模块冗余(dmr)。dmr复制基本的d触发器,并通过c单元输出结果,消耗的功率只有原始电路的两倍。值得注意的是,冗余方法也适用于d触发器的其他结构,例如真实单相时钟(tspc)结构和时钟cmos(c2mos)

3、在 pll 中,分频器负责将较高频率的 vco 输出信号转换为与基准频率相近的信号,以进行相位比较。分频器通常消耗 pll 中 vco 之后的大部分功率,因此设计出低功耗的分频器有助于降低 pll 的功耗。在高频中,注入锁定分频器 (injection-lockedfrequency divider, ilfd) 和再生分频器 (regenerative dividers) 比较常见。而基于d 触发器 (d flip-flop, dff) 的分频器由于其工作速度的限制通常用于预分频之后的低频率的分频。与高频分频器相比,dff 分频器具有更低的功耗和更高的锁定范围。在 dff中,真单相时钟控寄存器 (true single phaseclock, tspc) 仅使用单相时钟,避免了时钟重叠的影响。基于传输门或c2mos逻辑的传统d触发器往往需要互补时钟信号,而tspc d触发(tspc-dff)由于只与一个单相时钟一起工作,因此,减少了时钟上的负载。

技术实现思路

1、基于上述问题,本了一种新的交叉连接双模冗余d触发器抗发明提出辐照结构,其显著特征是在基础的tspc-d触发器上加入了冗余单元,由于交叉连接使得ccdm-tspc具有良好抗辐射能力,同时,新电路结构在能保证电路整体的抗seu和抗set效果下,具备更小的传输时延和功耗,并且没有过大的版图面积和开销。

2、本发明提供如下技术方案:

3、一种新型交叉连接双模冗余抗辐照的tspc触发器,包括:

4、其所述的新型结构包括;电路输入端口、电路输出端口、一个由真单相时钟控制的的tspc基本触发器,一个由真单相时钟控制的tspc冗余触发器,以及与所述tspc基本触发器和tspc冗余触发器的两个输出端口相连的一个c单元,

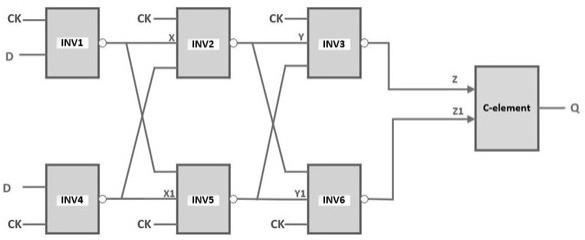

5、其中,第一级时钟控制反相器与第二级和第三级反相器构成第一级基本的tspc触发器,第四级时钟控制反相器与第五级和第六级反相构成第二级冗余的d触发器。其中,所述电路输入端口分为两路,其中一路连接所述的基本tspc触发器第一级反相器的d输入端口,第二级反相器的x输入端与所述第一级反相器的输出端口相连,第三级反相器的y输入端口与第二级反相器的输出端口相连;所述电路输入端口的令一路连接所述的冗余tspc触发器第四级反相器的d输入端口,第五级反相器的x1输入端与所述第四级反相器的输出端口相连,第六级反相器的y1输入端口与第五级反相器的输出端口相连,c单元的两个输入端口分别连接第三级反相器的输出端口和第六级反相器的输出端口,通过交叉连接的第一级反相器的输出端与第五级反向器的输入端,第四级反相器的输出端与第二级反向器的输入端,以及第二级反相器的输出端与第六级反向器的输入端,第五级反相器的输出端与第三级反向器的输入端,使得基础tspc和冗余tspc的输出结果共同决定此结构最终的输出结果。

6、本发明提供一种基于tspc结构的抗辐照d触发器,在tspc结构基础上将输入信号分为两路,其中一路输入信号输入给复刻的tspc冗余单元的输入端口,连接第四级反相器的前端,第二路输入信号送入基本tspcd触发器中第一级反相器的输入端口,冗余触发器单元和基本触发器单元的两路不同输出同步送入c单元判决的输入端口,输入的两路信号在时钟信号的控制下被触发器采样后的结果经c模块判决后共同决定此结构的最终输出,从而使电路各个端口具有了抗set的能力。本发明的电路结构能在保证电路整体具有抗seu和抗set效果上,提高响应速度并减少功耗,版图面积和花费也要优于典型抗辐照结构,大大提高了性能。

技术特征:

1.一种新型交叉连接双模冗余抗辐照的tspc触发器,其特征在于完全抑制set和seu瞬态事件的同时,具有较低的传输延时和较小的面积和花费,其所述的新型结构包括;电路输入端口、电路输出端口、一个由真单相时钟控制的的tspc基本触发器,一个由真单相时钟控制的tspc冗余触发器,以及与所述tspc基本触发器和tspc冗余触发器的两个输出端口相连的一个c单元。

2.根据权利要求1所述的新型交叉耦合tspc结构抗辐照d触发器,其特征在于: 其中一路输入信号输入给复刻的第二tspc冗余单元的输入端口,连接第四级反相器的前端,另一路输入信号送入第一基本tspc触发器中第一级反相器的输入端口,冗余触发器单元和基本触发器单元的两路不同输出同步送入c单元判决的输入端口,输入的两路信号在时钟信号的控制下被触发器采样后的结果经c模块判决后共同决定此结构的最终输出。

3.根据权利要求1所述的新型交叉耦合tspc结构抗辐照d触发器,其中,所述第一tspc触发器包括第一级反相器,由时钟信号和输入信号控制,在clk信号为低时,输入端口信号传输到第一级反向器的输出节点和第五级反相器的输入节点并反向,在clk信号为高时,输入端口信号无法传出到第一级反相器的输出节点,此时节点维持上一传递时刻状态。

4.根据权利要求1所述的新型交叉耦合tspc结构抗辐照d触发器,其中,所述第一tspc触发器包括第二级反相器,由时钟信号和第一级反相器输出信号和第四级反相器输出信号共同控制,在clk信号为低时,第二级反相器输出高电平信号,在 clk信号为高时,当输入端口信号为高,则第二级反相器维持上一状态;当输入端口信号为低时,则第二级反相器传输输入端口信号并输出同相信号。

5.根据权利要求1所述的新型交叉耦合tspc结构抗辐照d触发器,其中,所述第一tspc触发器包括第三级反相器,由时钟信号和第二级反相器输出信号和第五级反相器输出信号共同控制,在clk信号为低时,当输入端口输入高电平信号,则第三级反相器输出维持上一状态;当输入端口输入为低电平信号,则第三级反相器输出传输输入信号并反相,在clk信号为高时,当输入端口输入高电平信号,则第三级反相器传输输入信号并反向;当输入端口输入为低电平信号,则第三级反相器输出维持上一状态。

6.根据权利要求1所述的新型交叉耦合tspc结构抗辐照d触发器,其中,所述c单元判决器中包括两个输入信号,其中一路来自于基本tspc触发器的输出信号,另一路来自复刻的冗余tspc触发器的输出信号,两路信号同步送入c单元的两个输入端口,当两个输出同时为低电平时,输出反向信号即高电平信号;当输入同时为高电平时,输出反向信号即低电平信号,当冗余触发器和基本触发器输入的信号不相同(一个为高电平,另一个为低电平情况)时,输出维持上一个状态的信号。

7.一种新型交叉连接双模冗余抗辐照的tspc触发器,其抗辐照特征在于基本tspc-dff和冗余tspc-dff之间的交叉连接方式,其中,ccdm-tspc的电路包含六个敏感节点,分别是第一级到第六级反相器的六个输出节点。

8.根据权利要求7所述的新型交叉耦合tspc结构的抗辐照特性, 其中,在第一敏感点到第六敏感点中任意发生set或seu事件,在此结构的输出部分,即c单元判决器的输出端口可以传输正确的输入信号而不会被影响,因此结构具有良好的抗辐照特性。

技术总结

本发明涉及一种新型交叉连接双模冗余抗辐照的TSPC触发器(CCDM‑TSPC),其输入阶段包含一个基本的TSPC‑DFF和一个冗余的TSPC‑DFF,此两部分之间交叉连接,两个输出结果送入一个C单元之中,共同决定最终输出结果,保证了在某一路上发生SEU事件或SET事件时,输出节点完全不受影响,相比于传统的D触发器结构,新结构具备更小的传输时延和功耗。

技术研发人员:赵高峰,赵媛,王士鑫,郭敏

受保护的技术使用者:河南大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!