一种集成电路逻辑失效监测电路及隔离电路的制作方法

本发明涉及电路监测,尤其是一种集成电路逻辑失效监测电路及隔离电路。

背景技术:

1、集成电路是一种微型电子设备,包括由许多晶体管和其他电子元件组成的逻辑电路,可以用于实现各种逻辑功能。

2、在逻辑电路中,存在着电路失效的风险,即逻辑电路的工作电压低于逻辑电路的失效电压时,逻辑电路将无法正常工作,因此在实际运行中,通常需要设置一个低电压监测模块来监测逻辑电路的工作电压,并在逻辑电路的工作电压低于一个预设值时进行复位,以避免逻辑电路在低电压下失效。

3、在这种方法中,在设置预设值时,需要考虑到逻辑电路的失效电压的范围,以确保不会出现电路失效的情况,由于逻辑失效电压通常是一个范围,而非一个具体数值,因此预设值需要高于失效电压范围内的最小值,以保证电路的可靠性。

4、然而,由于预设值需要高于失效电压范围内的最小值,可能会导致低电压监测值实际上比所需的更高,从而限制了电路的宽压范围。

技术实现思路

1、本发明的目的在于提供一种集成电路逻辑失效监测电路及隔离电路,旨在解决现有技术中对逻辑电路的失效电压监测会限制电路的宽压范围的问题。

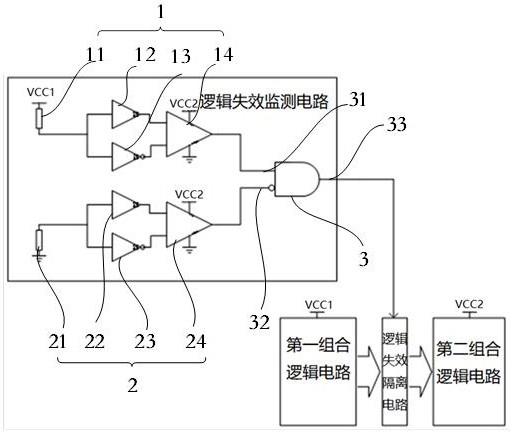

2、本发明是这样实现的,第一方面,本发明提供一种集成电路逻辑失效监测电路,设置在集成电路中,所述集成电路包括第一组合逻辑电路和第二组合逻辑电路,所述集成电路逻辑失效监测电路包括:

3、第一逻辑电平单元、第二逻辑电平单元、与门电路;

4、所述第一逻辑电平单元与所述第一组合逻辑电路电连接,当所述第一组合逻辑电路的工作电压正常时,所述第一逻辑电平单元产生第一逻辑电平,当所述第一组合逻辑电路的工作电压失效时,所述第一逻辑电平单元产生第二逻辑电平;

5、所述第二逻辑电平单元接地,所述第二逻辑电平单元用于产生第二逻辑电平;

6、所述与门电路具有正向输入端、反向输入端以及与门输出端,所述与门电路通过所述正向输入端与所述第一逻辑电平单元电连接,通过所述反向输入端与所述第二逻辑电平单元电连接,通过与门输出端与所述第二组合逻辑电路电连接;

7、当所述与门电路通过所述正向输入端接收到第一逻辑电平并通过所述反向输入端接收到第二逻辑电平时,所述与门电路通过所述与门输出端输出第一监测信号;

8、当所述与门电路通过所述正向输入端接收到第二逻辑电平并通过所述反向输入端接收到第二逻辑电平时,所述与门电路通过所述与门输出端输出第二监测信号。

9、在一些实施例中,所述第一逻辑电平单元包括上拉电阻、第一缓冲器、第一反相器以及第一运算放大器;

10、所述上拉电阻分别与所述第一组合逻辑电路、所述第一缓冲器以及所述第一反相器电连接,所述第一运算放大器具有两个输入端和一个输出端,所述第一运算放大器通过一个输入端与所述第一缓冲器电连接,通过另一个输入端与所述第一反相器电连接,通过输出端与所述与门电路电连接;

11、当所述第一组合逻辑电路的工作电压正常时,所述上拉电阻接收所述第一组合逻辑电路的电压信号并生成高电平信号,所述第一缓冲器和所述第一反相器用于将所述高电平信号转换为差分信号1,所述第一运算放大器用于将所述差分信号1转换为第一逻辑电平;

12、当所述第一组合逻辑电路的工作电压失效时,所述上拉电阻将接收所述第一组合逻辑电路的电压信号并生成低电平信号,所述第一缓冲器和所述第一反相器用于将所述低电平信号转换为差分信号0,所述第一运算放大器用于将所述差分信号0转换为第二逻辑电平。

13、在一些实施例中,所述第二逻辑电平单元包括下拉电阻、第二缓冲器、第二反相器以及第二运算放大器;

14、所述下拉电阻分别与所述第一组合逻辑电路、所述第二缓冲器和所述第二反相器电连接,所述第二运算放大器具有两个输入端和一个输出端,所述第二运算放大器通过一个输入端与所述第一缓冲器电连接,通过另一个输入端与所述第二反相器电连接,通过输出端与所述与门电路电连接;

15、所述下拉电阻用于生成低电平信号,所述第二缓冲器和所述第二反相器用于将所述低电平信号转换为差分信号0,所述第二运算放大器用于将所述差分信号0转换为第二逻辑电平。

16、第二方面,本发明提供一种集成电路逻辑失效隔离电路,设置在集成电路中,所述集成电路逻辑失效隔离电路与第一方面任意一项所述的一种集成电路逻辑失效监测电路、第一组合逻辑电路以及第二组合逻辑电路电连接,所述集成电路逻辑失效隔离电路包括:

17、门电路单元;

18、所述门电路单元具有两个输入端和一个输出端,所述门电路单元通过两个输入端分别与所述一种集成电路逻辑失效监测电路和所述第一组合逻辑电路电连接,通过输出端与第二组合逻辑电路电连接。

19、在一些实施例中,所述门电路单元为与门电路。

20、在一些实施例中,所述门电路单元为或门电路。

21、本发明提供了一种集成电路逻辑失效监测电路,具有以下有益效果:

22、本发明将第一逻辑电平单元与第一组合逻辑电路电连接,第一逻辑电平单元将根据第一组合逻辑电路的工作电压状态输出第一逻辑电平或第二逻辑电平,与门单元会根据接收到的逻辑电平而输出监测信号,当第一组合逻辑电路的工作电压失效时,第一逻辑电平单元输出第二逻辑电平,此时与门单元输出第二监测信号,即可检测到第一组合逻辑电路的工作电压失效,与传统的方法相比,本发明无需设置一个高于实际失效电压的预设值,不会在逻辑电路未失效时就判断逻辑电路的工作电压失效,解决了现有技术中对逻辑电路的失效电压监测会限制电路的宽压范围的问题。

技术特征:

1.一种集成电路逻辑失效监测电路,设置在集成电路中,所述集成电路包括第一组合逻辑电路和第二组合逻辑电路,其特征在于,所述集成电路逻辑失效监测电路包括:

2.如权利要求1所述的一种集成电路逻辑失效监测电路,其特征在于,所述第一逻辑电平单元包括上拉电阻、第一缓冲器、第一反相器以及第一运算放大器;

3.如权利要求1所述的一种集成电路逻辑失效监测电路,其特征在于,所述第二逻辑电平单元包括下拉电阻、第二缓冲器、第二反相器以及第二运算放大器;

4.一种集成电路逻辑失效隔离电路,设置在集成电路中,其特征在于,所述集成电路逻辑失效隔离电路与权利要求1-3任意一项所述的一种集成电路逻辑失效监测电路、第一组合逻辑电路以及第二组合逻辑电路电连接,所述集成电路逻辑失效隔离电路包括:

5.如权利要求4所述的一种集成电路逻辑失效隔离电路,其特征在于,所述门电路单元为与门电路。

6.如权利要求4所述的一种集成电路逻辑失效隔离电路,其特征在于,所述门电路单元为或门电路。

技术总结

本发明涉及电路监测的技术领域,公开了一种集成电路逻辑失效监测电路及隔离电路;本发明将第一逻辑电平单元与第一组合逻辑电路电连接,第一逻辑电平单元将根据第一组合逻辑电路的工作电压状态输出第一逻辑电平或第二逻辑电平,与门单元会根据接收到的逻辑电平而输出监测信号,当第一组合逻辑电路的工作电压失效时,第一逻辑电平单元输出第二逻辑电平,此时与门单元输出第二监测信号,即可检测到第一组合逻辑电路的工作电压失效,与传统的方法相比,本发明无需设置一个高于实际失效电压的预设值,不会在逻辑电路未失效时就判断逻辑电路的工作电压失效,解决了现有技术中对逻辑电路的失效电压监测会限制电路的宽压范围的问题。

技术研发人员:周仲武,程君健,翟冠杰

受保护的技术使用者:深圳市赛元微电子股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!