用于在半导体结构中埋入导体线的方法和半导体结构与流程

本公开涉及半导体技术的领域,具体地,本公开涉及用于在半导体结构中埋入导体线的方法以及使用该方法制造的具有埋入导体线的半导体结构。

背景技术:

1、从二十世纪七十年代英特尔公司(intel corporation)发明动态随机存取存储器(dynamic random access memory,dram)以来,dram被广泛应用于各类计算或控制电子电路系统中。

2、dram单元电路通常由一个用于选通的晶体管和一个用于存储电荷的电容器构成(1t1c结构)。在使用传统的基于平面结构的水平型晶体管,例如金属氧化物半导体场效应晶体管(metal oxide semiconductor field effect transistor,mosfet)实现选通晶体管的dram单元结构中,晶体管的源极、栅极和漏极沿平行于衬底表面的水平方向布置。由于晶体管的源极、栅极和漏极在水平方向上各自占有独立的面积,因此dram单元电路结构的微缩受到栅极长度和接触尺寸的限制,无法满足dram装置持续微缩的需求,进而限制了dram装置的集成度和带宽的进一步增加。

3、因此,近年来提出了竖直型的dram单元结构,其中晶体管的源极、栅极和漏极沿垂直于衬底表面的竖直方向设置,无需额外占用面积,利于dram阵列结构的尺寸微缩。

4、然而,对于竖直型的dram单元结构构成的dram阵列结构,需要在竖直方向上设置位线和字线以在列方向和行方向上将dram单元结构互连成dram阵列结构,因此如何在保证性能和提高密度的前提下在dram阵列结构中设置位线仍是亟需改进的问题。

5、在本背景技术部分中公开的以上信息仅用于理解本发明构思的背景,并且因此可能包含不构成现有技术的信息。

技术实现思路

1、为了解决现有技术中存在的以上问题,本公开提出了新型的用于在半导体结构中埋入导体线的方法。

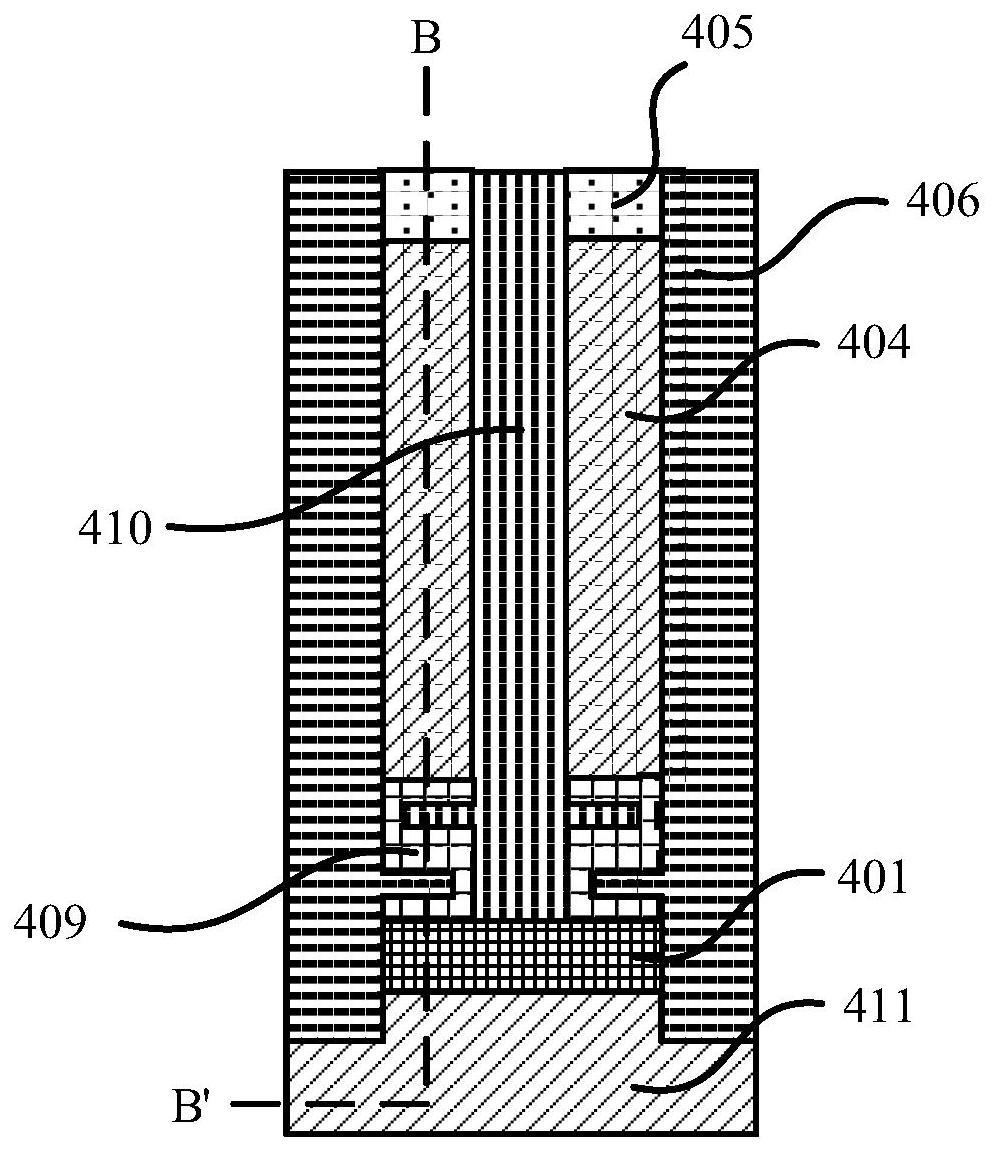

2、根据本公开的一个方面,提供了一种用于在半导体结构中埋入导体线的方法,包括:提供衬底;在衬底上依次设置多个牺牲层、有源层和硬掩模层,其中多个牺牲层具有相对于彼此的刻蚀选择性;对硬掩模层进行构图和刻蚀以形成硬掩模阻挡部,并且在硬掩模阻挡部的两侧形成侧墙;使用硬掩模阻挡部和侧墙自对准刻蚀有源层、多个牺牲层以形成延伸至衬底的第一槽;去除硬掩模阻挡部,并且使用侧墙自对准刻蚀有源层以形成使多个牺牲层暴露的第二槽,第二槽延伸到衬底;通过第一槽和/或第二槽依次去除多个牺牲层以在去除多个牺牲层留下的空间中依次埋入导体线;以及使用隔离介质填充第一槽和第二槽。

3、根据本公开的另一方面,提供了一种使用根据本公开的上述方面的方法制造的具有埋入导体线的半导体结构。

4、根据本公开的用于在半导体结构中埋入导体线的方法,通过两次自对准刻蚀形成彼此隔离的第一槽和第二槽,通过第一槽和/或第二槽依次去除多个牺牲层以在去除多个牺牲层留下的空间中依次埋入导体线,并且在所述导体线下方设置隔离结构,可以形成彼此隔离的多个埋入导体线。

5、然而,本公开的效果不限于上述效果,并且可以在不脱离本公开的精神和范围的情况下进行各种扩展。应当理解,前面的一般描述和下面的详细描述都是示例性和解释性的,并且旨在提供对要求保护的本公开的进一步说明。

技术特征:

1.一种用于在半导体结构中埋入导体线的方法,包括:

2.根据权利要求1所述的方法,还包括:

3.根据权利要求2所述的方法,其中,所述隔离结构包括pn结和/或绝缘层。

4.根据权利要求1所述的方法,还包括:

5.根据权利要求4所述的方法,其中,所述隔离结构包括所述隔离介质。

6.根据权利要求1所述的方法,其中,所述导体线包括金属和/或金属硅化物。

7.根据权利要求1所述的方法,其中,当通过所述多个牺牲层中的叠置的两个牺牲层埋入两层导体线时,所述导体线具有镜像的“s”形和/或“e”形的剖面。

8.根据权利要求1所述的方法,其中,所述导体线具有实心矩形的剖面。

9.根据权利要求7所述的方法,其中,在具有镜像的“s”形和/或“e”形剖面的所述导体线的凹入部分中形成填充有空气的空腔。

10.根据权利要求1所述的方法,其中,填充在所述第一槽中的隔离介质与填充在所述第二槽中的隔离介质相同或不同。

11.根据权利要求1所述的方法,其中,所述多个牺牲层包括锗硅,并且所述多个牺牲层具有彼此不同的锗浓度。

12.根据权利要求1所述的方法,还包括:

13.一种使用根据权利要求1至12中任一项所述的方法制造的具有埋入导体线的半导体结构。

技术总结

本公开提供了用于在半导体结构中埋入导体线的方法和通过该方法制造的半导体结构。根据本公开的方法包括:提供衬底;在衬底上依次设置多个牺牲层、有源层和硬掩模层,其中多个牺牲层具有相对于彼此的刻蚀选择性;对硬掩模层进行构图和刻蚀以形成硬掩模阻挡部,并且在硬掩模阻挡部的两侧形成侧墙;使用硬掩模阻挡部和侧墙自对准刻蚀有源层、多个牺牲层以形成延伸至衬底的第一槽;去除硬掩模阻挡部,并且使用侧墙自对准刻蚀有源层以形成使多个牺牲层暴露的第二槽,第二槽延伸到衬底;通过第一槽和/或第二槽依次去除多个牺牲层以在去除多个牺牲层留下的空间中依次埋入导体线;以及使用隔离介质填充第一槽和第二槽。

技术研发人员:潘立阳,刘子易,张志刚

受保护的技术使用者:北京超弦存储器研究院

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!