一种半导体结构的制作方法及半导体结构与流程

本公开实施例涉及半导体领域,特别涉及一种半导体结构的制作方法及半导体结构。

背景技术:

1、存储器是用来存储程序和各种数据信息的记忆部件。一般计算机系统使用的随机存取内存(random access memory,ram)可分为动态随机存取存储器(dynamicrandomaccess memory,dram)与静态随机存取存储器(static random-access memory,sram)两种,动态随机存取存储器是计算机中常用的半导体存储器件,由许多重复的存储单元组成。

2、目前在形成存储器的时候,图形化处理工艺是必不可少的一步,然而目前存在图形化处理工艺对准精度不够的问题。

技术实现思路

1、本公开实施例提供一种半导体结构的制作方法,至少可以提高图形化处理工艺的对准精度。

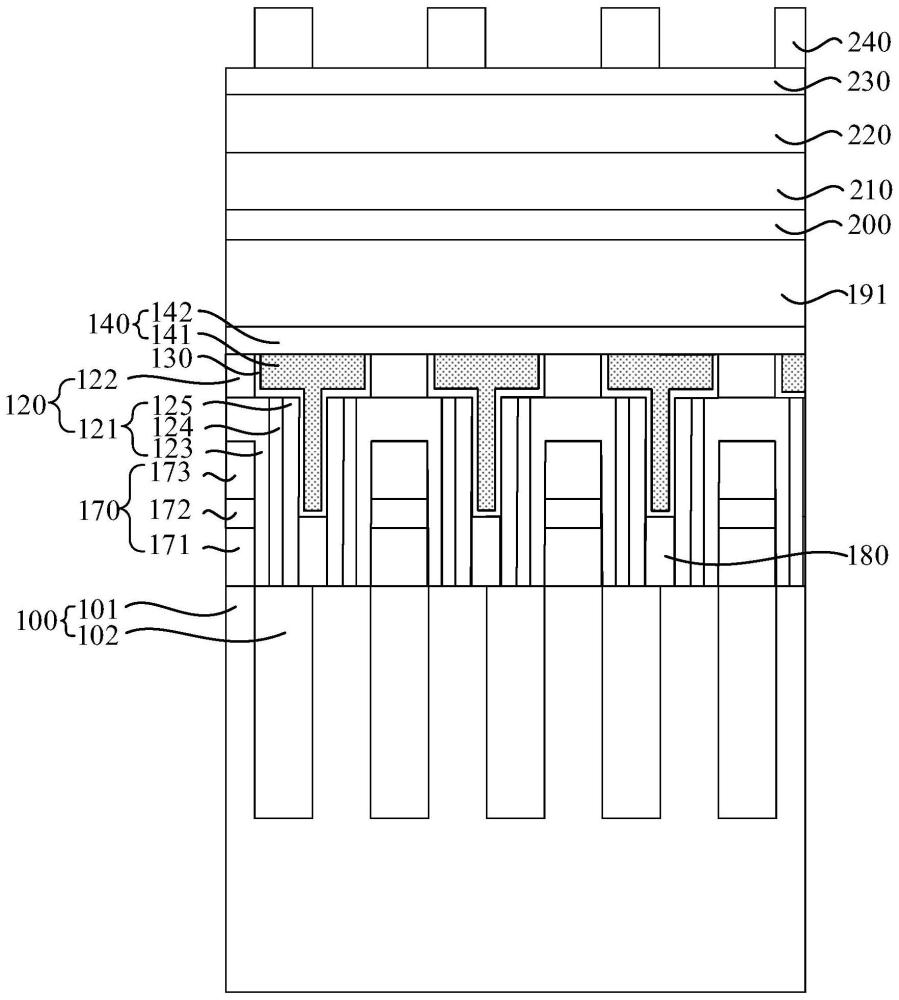

2、根据本公开一些实施例,本公开实施例一方面提供一种半导体结构的制作方法,包括:提供衬底,所述衬底具有多个沿第一方向间隔排布的第一沟槽,相邻的所述第一沟槽之间具有绝缘介质层;在所述衬底上形成覆盖所述第一沟槽表面的第一导电层和填充所述第一沟槽的第二导电层,所述第二导电层还形成在所述绝缘介质层上;对所述第二导电层进行图形化处理工艺,去除部分位于所述第一沟槽内的所述第二导电层,以形成第二沟槽,所述第二沟槽的顶表面高于所述绝缘介质层的顶表面,且所述第二沟槽暴露出部分所述绝缘介质层的侧壁及部分顶面;在所述第二沟槽中形成隔离结构。

3、在一些实施例中,形成所述第一导电层的方法包括:形成第一初始导电层,所述第一初始导电层覆盖所述第一沟槽的表面,且还覆盖所述绝缘介质层的顶面;刻蚀所述第一初始导电层,刻蚀位于所述绝缘介质层顶面的所述第一初始导电层及位于所述第一沟槽底面的所述第一初始导电层,剩余所述第一初始导电层作为所述第一导电层。

4、在一些实施例中,形成所述第二导电层的方法包括:刻蚀所述第一初始导电层之后,填充导电材料以形成所述第二导电层,所述第二导电层填充满所述第一沟槽,且所述第二导电层还覆盖所述绝缘介质层的顶面。

5、在一些实施例中,形成所述第二导电层的方法包括:形成第一子导电层,所述第一子导电层与所述绝缘介质层的顶面齐平;形成第二子导电层,所述第二子导电层覆盖所述第一子导电层的顶面,且还覆盖所述绝缘介质层的顶面,所述第二子导电层与所述第一子导电层构成所述第二导电层。

6、在一些实施例中,形成所述第一子导电层的方法包括:刻蚀所述第一初始导电层之前,形成第一初始子导电层,所述第一初始子导电层填充满所述第一沟槽,且所述第一初始子导电层的顶面高于所述绝缘介质层的顶面;进行第一次刻蚀处理,以形成所述第一子导电层,所述第一子导电层的顶面不高于所述绝缘介质层的顶面。

7、在一些实施例中,所述第一子导电层与所述第二子导电层的材料相同。

8、在一些实施例中,形成所述第二子导电层的方法包括:采用物理气相沉积的方式形成所述第二子导电层。

9、在一些实施例中,进行所述图形化处理工艺的方法包括:在所述第二导电层的顶面依次形成堆叠的初始目标层、第一刻蚀停止层、中间层、掩膜层、第二刻蚀停止层及光刻胶层;以所述光刻胶层为掩膜依次刻蚀所述第二刻蚀停止层、所述掩膜层、所述中间层、所述第一刻蚀停止层及所述初始目标层,以暴露部分所述第二导电层的顶面,剩余所述初始目标层作为所述目标层;以所述目标层为掩膜刻蚀所述第二导电层,以形成所述第二沟槽。

10、在一些实施例中,在形成所述第一沟槽前,还包括在所述衬底表面形成多个沿所述第一方向间隔排布的多条位线结构,所述第一沟槽形成在相邻的所述位线结构之间,所述绝缘介质层覆盖所述位线结构。

11、在一些实施例中,第二导电层的厚度为10-30nm。

12、根据本公开一些实施例,本公开实施例另一方面还提供一种半导体结构,包括:衬底,所述衬底具有多个沿第一方向间隔排布的第一沟槽,相邻的所述第一沟槽之间具有绝缘介质层;第一导电层,所述第一导电层覆盖所述第一沟槽的表面;第二导电层,所述第二导电层位于所述第一沟槽内,且所述第二导电层还覆盖部分所述绝缘介质层的表面及部分顶面,所述第二导电层与所述绝缘介质层围成第二沟槽;隔离结构,所述隔离结构位于所述第二沟槽内。

13、在一些实施例中,所述第二导电层包括:第一子导电层,所述第一子导电层位于所述相邻所述绝缘介质层之间,且部分所述第一子导电层的顶面与所述绝缘介质层的顶面齐平,部分所述第一子导电层的顶面低于所述绝缘介质层的顶面;第二子导电层,所述第二子导电层覆盖所述绝缘介质层的部分顶面,且所述第二子导电层还覆盖所述第一子导电层与所述绝缘介质层的顶面齐平的顶面。

14、在一些实施例中,所述第一子导电层包括:所述第一部分与所述第一沟槽相对两侧的所述第一导电层接触;第二部分,所述第二部分位于所述第一部分顶面,且位于所述第一导电层与所述隔离结构之间。

15、在一些实施例中,所述第一导电层的厚度小于所述第一子导电层,所述第一子导电层的厚度大于所述第二子导电层的厚度。

16、在一些实施例中,还包括位线结构,所述位线结构沿所述第一方向间隔排布,且所述第一沟槽位于相邻的所述位线结构之间。

17、本公开实施例提供的技术方案至少具有以下优点:通过形成仅覆盖第一沟槽表面的第一导电层和填充满第一沟槽的第二导电层,从而可以避免第一导电层影响对第二导电层进行图形化处理工艺造成影响,可以不用担心因为刻蚀的偏移导致后续经过图形化处理工艺之后的第二导电层相互短接,且还可以减少在进行图形化处理工艺时刻蚀第一导电层和第二导电层之间的刻蚀差异,从而可以提高图形化处理工艺的精确性。

技术特征:

1.一种半导体结构的制作方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制作方法,其特征在于,形成所述第一导电层的方法包括:

3.根据权利要求2所述的半导体结构的制作方法,其特征在于,形成所述第二导电层的方法包括:

4.根据权利要求2所述的半导体结构的制作方法,其特征在于,形成所述第二导电层的方法包括:

5.根据权利要求4所述的半导体结构的制作方法,其特征在于,形成所述第一子导电层的方法包括:

6.根据权利要求4所述的半导体结构的制作方法,其特征在于,所述第一子导电层与所述第二子导电层的材料相同。

7.根据权利要求4所述的半导体结构的制作方法,其特征在于,形成所述第二子导电层的方法包括:采用物理气相沉积的方式形成所述第二子导电层。

8.根据权利要求1所述的半导体结构的制作方法,其特征在于,进行所述图形化处理工艺的方法包括:

9.根据权利要求1所述的半导体结构的制作方法,其特征在于,在形成所述第一沟槽前,还包括在所述衬底表面形成多个沿所述第一方向间隔排布的多条位线结构,所述第一沟槽形成在相邻的所述位线结构之间,所述绝缘介质层覆盖所述位线结构。

10.根据权利要求1所述的半导体结构的制作方法,其特征在于,所述第二导电层的厚度为10-30nm。

11.一种半导体结构,其特征在于,包括:

12.根据权利要求11所述的半导体结构,其特征在于,所述第二导电层包括:

13.根据权利要求12所述的半导体结构,其特征在于,所述第一子导电层包括:

14.根据权利要求12所述的半导体结构,其特征在于,所述第一导电层的厚度小于所述第一子导电层,所述第一子导电层的厚度大于所述第二子导电层的厚度。

15.根据权利要求11所述的半导体结构,其特征在于,还包括位线结构,所述位线结构沿所述第一方向间隔排布,且所述第一沟槽位于相邻的所述位线结构之间。

技术总结

本公开实施例涉及半导体领域,提供一种半导体结构的制作方法及半导体结构,其中,半导体结构的制作方法包括:提供衬底,衬底具有多个沿第一方向间隔排布的第一沟槽,相邻的第一沟槽之间具有绝缘介质层;在衬底上形成覆盖第一沟槽表面的第一导电层和填充第一沟槽的第二导电层,第二导电层还形成在绝缘介质层上;对第二导电层进行图形化处理工艺,去除部分位于第一沟槽内的第二导电层,以形成第二沟槽,第二沟槽的顶表面高于绝缘介质层的顶表面,且第二沟槽暴露出部分绝缘介质层的侧壁及部分顶面;在第二沟槽中形成隔离结构。可以提高图形化处理工艺的对准精度。

技术研发人员:李群,马宏

受保护的技术使用者:长鑫科技集团股份有限公司

技术研发日:

技术公布日:2025/1/28

- 还没有人留言评论。精彩留言会获得点赞!