一种半带FIR滤波器电路结构的制作方法

本发明涉及数字信号处理,特别涉及一种半带fir滤波器电路结构。

背景技术:

1、半带滤波器是一种特殊的fir滤波器,其阶数只能为偶数,长度为奇数(即n阶滤波器,n+1个抽头)。滤波器系数除了中间值为0.5外,其余偶数序号的系数都为0,因此也大大节省了滤波时的乘法和加法运算。半带滤波器是一种特殊的低通fir数字滤波器,这种滤波器由于通带和阻带相对于二分之一nyquist(奈奎斯特)频率对称,因而有近一半的滤波器系数精确为零。

2、半带fir滤波器的一般频率响应如图1所示,图中表示通带波纹,表示阻带波纹,表示通带边频,表示阻带边频。半带fir滤波器通常具有如下几种特性:(1)通带波纹和阻带波纹相等,即;(2)通带边频和阻带边频相对于是对称的,即;(3)滤波器的系数具有偶对称特性,且滤波器长度为偶数(滤波器阶数为奇数)。滤波器所有大于0的偶数序号的冲击响应值均为0,半带滤波器的这一特性大大降低了滤波器运算所需的乘法及加法次数;(4)经半带滤波器滤波后,进行2倍抽取时,信号通带内没有频谱混叠,但阻带内有频谱混叠。

3、通带波纹与阻带波纹相等,这些特征反映在滤波器的冲激响应中。例如,对于奇数个抽头系数的滤波器来说,大约有一半的系数为零且交错在非零系数之间,如图2所示,是具有11个抽头的半带滤波器;在设计半带fir滤波器时,基于半带滤波器的特性可以得到如图3所示的电路结构:图中a[2n]表示相应阶数的系数值,其中d表示寄存器,x[n]表示输入信号,y[n]表示输出信号。

4、如图3所示的传统电路结构存在多种问题:(1)无法应用于高速数字电路中,为了追求更高精度的输出以及更陡峭的幅频响应,要求输出为阶数通常会较高,这会存在较长的关键路径和更多的算术单元,很难在一个时钟周期内完成。(2)存在更大的功耗损失以及更大的面积,在相同的时钟约束下会使用更多的lvt晶体管实现更快的速度性能来满足条件,而lvt晶体管的阈值电压低,功耗会更大,在综合以后会占用更大的面积,这就导致成本增加。

技术实现思路

1、本发明的目的在于提供一种半带fir滤波器电路结构,以解决背景技术中的问题。

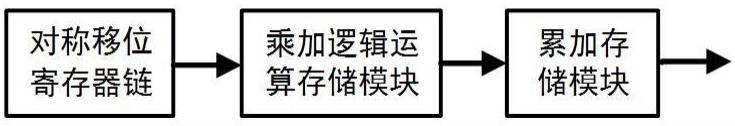

2、为解决上述技术问题,本发明提供了一种半带fir滤波器电路结构,包括:

3、对称移位寄存器链,用于存储滤波器运算所需数据量;

4、乘加逻辑运算存储模块,计算滤波器公式中每一阶的运算结果,将每一阶的运算结果根据位宽大小相近的为一组,两两相加后存储在对应寄存器中;

5、累加存储模块,通过n步累加来得出最终输出结果,即通过流水线结构实现在几个时钟周期内得出最终结果。

6、在一种实施方式中,所述对称移位寄存器链包括(n+1)个依次串联的d触发器和[(n-1)/4]个加法器,符号[]表示向上取整;

7、第一个加法器的一个正输入端接第一个d触发器的输入端,另一个正输入端接第(n+1)个d触发器的输出端;

8、第二个加法器的一个正输入端接第三个d触发器的输入端,另一个正输入端接第(n-1)个d触发器的输出端;

9、...;

10、第[(n-1)/4]个加法器的一个正输入端接第[(n+1)/2]个d触发器的输入端,另一个正输入端接第[(n+1)/2+1]个d触发器的输出端。

11、在一种实施方式中,所述对称移位寄存器链输出[(n-1)/4]+1个输出结果,前[(n-1)/4]个输出结果分别从每个加法器的输出端输出,第[(n-1)/4]+1个输出结果从第[(n+1)/2]个d触发器的输出端输出。

12、在一种实施方式中,所述乘加逻辑运算存储模块包括[(n-1)/4]+1个乘法器、([(n-1)/4]+1)/2个加法器和([(n-1)/4]+1)/2个寄存器,所述对称移位寄存器链输出的每个输出结果分别输入一个乘法器中,每两个乘法器的输出端和一个加法器的输入端相连,每一个加法器的输出端与一个寄存器的输入端相连。

13、在一种实施方式中,所述累加存储模块包括[([(n-1)/4]+1)/4]+1个加法器和[([(n-1)/4]+1)/4]个寄存器,一个加法器和一个寄存器相连,所有的寄存器输入至最后一个加法器中,最后一个加法器输出y[n]。

14、本发明提供的一种半带fir滤波器电路结构,打断原本冗长的加法链,关键路径短,容易在高速电路中实现;并且使用对称fir结构减少硬件消耗,可以只使用rvt工艺库来做综合实现,流水线结构避免了使用lvt的工艺库,使得总体硬件消耗反而比使用rvt综合实现更小。本发明可以在综合约束中禁用lvt工艺库,能有效做到低功耗,低复杂度;使用相同工艺制程节点的基础上,对传统结构和本发明所提出的结构做综合实现,时钟频率约束在400mhz,前者综合实现后网表的面积在8577.156,而后者综合实现的网表面积在6713.000;而且前者使用了大量rvt晶体管使电路能勉强满足在400mhz下的时序关系,而后者只使用了lvt的工艺库即可满足,且能满足更高的时钟频率约束。

技术特征:

1.一种半带fir滤波器电路结构,其特征在于,包括:

2.如权利要求1所述的半带fir滤波器电路结构,其特征在于,所述对称移位寄存器链包括(n+1)个依次串联的d触发器和[(n-1)/4]个加法器,符号[]表示向上取整;

3.如权利要求2所述的半带fir滤波器电路结构,其特征在于,所述对称移位寄存器链输出[(n-1)/4]+1个输出结果,前[(n-1)/4]个输出结果分别从每个加法器的输出端输出,第[(n-1)/4]+1个输出结果从第[(n+1)/2]个d触发器的输出端输出。

4.如权利要求3所述的半带fir滤波器电路结构,其特征在于,所述乘加逻辑运算存储模块包括[(n-1)/4]+1个乘法器、([(n-1)/4]+1)/2个加法器和([(n-1)/4]+1)/2个寄存器,所述对称移位寄存器链输出的每个输出结果分别输入一个乘法器中,每两个乘法器的输出端和一个加法器的输入端相连,每一个加法器的输出端与一个寄存器的输入端相连。

5.如权利要求4所述的半带fir滤波器电路结构,其特征在于,所述累加存储模块包括[([(n-1)/4]+1)/4]+1个加法器和[([(n-1)/4]+1)/4]个寄存器,一个加法器和一个寄存器相连,所有的寄存器输入至最后一个加法器中,最后一个加法器输出y[n]。

技术总结

本发明公开一种半带FIR滤波器电路结构,属于数字信号处理技领域,主要分为对称移位寄存器链、乘加逻辑运算存储模块和累加存储模块三部分。对称移位寄存器链存储滤波器运算所需数据量;乘加逻辑运算存储模块计算滤波器公式中每一阶的运算结果,将每一阶的运算结果根据位宽大小相近的为一组,两两相加后存储在对应寄存器中;累加存储模块将原本在一个时钟周期内将所有阶数的乘加运算结果全部相加得出最终输出,变成通过n步累加来得出最终输出结果,即通过流水线结构实现在几个时钟周期内得出最终结果。

技术研发人员:吴旭凡

受保护的技术使用者:上海芯炽科技集团有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!