小数调制器输出序列重构及小数频率合成器杂散抑制方法与流程

本发明涉及小数频率合成器,具体涉及一种小数调制器输出序列重构方法及一种小数频率合成器杂散抑制方法。

背景技术:

1、小数频率合成器技术广泛应用于无线通信、雷达系统和仪器仪表中产生各种所需要的频率信息。小数分频器采用sigma-delta调制噪声整形技术,对数字信号的量化误差进行量化整形处理,将量化噪声往频率高端搬移,由噪声传递函数ntf进行高通滤波,再通过环路的低通滤波作用加以滤除环路带外噪声,从而降低了量化噪声的影响,有效地抑制了小数杂散,同时又获得了精细的频率分辨率。

2、传统的小数分频频率合成器即一阶sigma-delta调制器通过累加器的进位,控制前置双模分频器在n和n+1两个分频数之间转换,通过环路的低通滤波作用,使vco锁定在参考频率的分数谐波上。由于锁相环使vco的频率只能在在n和n+1倍参考频率之间跳变,这就会引起vco输出信号的相位调制,并产生较大杂散。为了进一步抑制小数杂散,增加重复周期,相继提出了高阶sigma-delta调制器技术,常见的有3阶或4阶,对应环路分频比的变化范围最大达到了-3~+4(三阶调制器)和-7~+8(四阶调制器)。高阶调制器以mash 1-1-1为经典电路结构,以三阶调制器为例,其采用三环结构,每个环路由一个累加器和单比特量化器构成,第1个累加器溢出时,在一个周期内分频比从n变到n+1,然后在下一个周期回到n,余数代表了相位误差,如不对其进行修正就会产生相位抖动。第2个累加器的溢出可进一步控制分频比,当它溢出时,在一个周期内分频比从n变为n+1,然后在第2个时钟周期分频比变为n–1,第3个时钟周期再回到n。第3个累加器依此将分频比从n变为n+1、n-2、n+1,再回到n。以次类推,该序列构成一个pascal三角形。以小数0.625为例,三阶调制器输出序列为+3,-2,+2,+1,+0,+0,+2,+0,+1,+0,+1,+0,+1,+1,+1,-1共16个序列,总和为10,则平均序列值为10/16=0.625。三阶调制器比一阶调制器增加了小数周期序列长度,更好地离散化了小数序列。但是,其缺点是当三个量化器叠加输出序列会从最大正值(+3)跳变到最小负值(-2)最大跳变为5,如此大的突变经低通滤波器滤波后,会直接加到压控振荡器vco控制端,从而vco会产生较大杂散。

技术实现思路

1、有鉴于此,本发明提出了一种小数调制器输出序列重构及小数频率合成器杂散抑制方法,该方法对小数频率调制器序列进行重构,使得每次调制器输出变化最大值以步长1变化,经低通滤波器器滤波后使vco的控制电压得到有效平滑,从而避免vco输出电压的跳变,有效地抑制输出频率杂散。

2、为了实现上述目的,本发明采用的技术方案为:

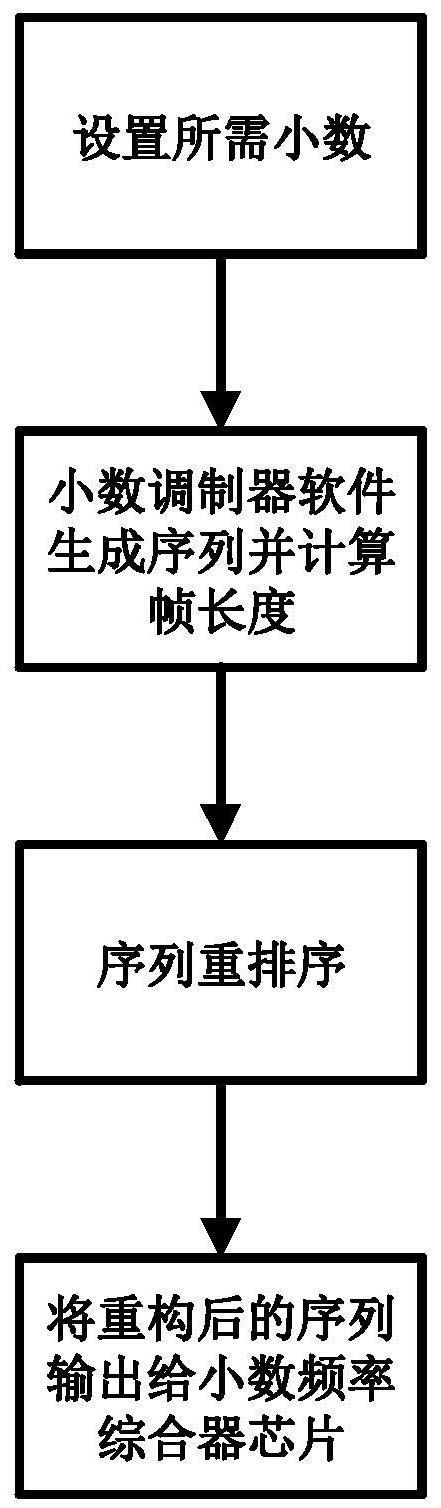

3、一种小数调制器输出序列重构方法,包括以下步骤:

4、步骤1,在小数调制器输出序列中任意寻找6比特数据,随后使用滑窗法再次寻找到该6比特数据,对比两次寻找的6比特数据,如果数据不同则重新寻找,如果数据相同,则判断该序列的平均值是否为目标小数值,如果不是则重新寻找,如果是则记录该序列长度;

5、步骤2,根据序列长度,将一个周期的序列存储在数组中,将序列升序排列,随后正序输出再倒序输出,并使重新排序后相邻序列的最大差值不超过±1,输出重构后的序列。

6、一种小数频率合成器杂散抑制方法,包括以下步骤:

7、步骤1,根据分频比,通过sigma-delta小数调制器生成周期性的输出序列;

8、步骤2,在输出序列中任意寻找6比特数据,随后使用滑窗法再次寻找到该6比特数据,对比两次寻找的6比特数据,如果数据不同则重新寻找,如果数据相同,则判断该序列的平均值是否为目标小数值,如果不是则重新寻找,如果是则记录该序列长度;

9、步骤3,根据序列长度,将一个周期的序列存储在数组中,将序列升序排列,随后正序输出再倒序输出,并使重新排序后相邻序列的最大差值不超过±1,输出重构后的序列;

10、步骤4,将重构后的序列输出给小数频率综合器芯片,实现连续可变的分频比,实现小数分频功能。

11、与现有技术相比,本发明的有益效果如下:

12、1、本发明通过该小数频率合成器的重构技术,将复杂调制器和序列重排功能由计算机软件完成,不占用频率合成器硬件资源和芯片面积。

13、2、本发明将重构后序列最大跳变值控制在±1范围内,有效地减少了压控振荡器vco控制端的电压突变,同时也能有效地对小数频率合成器的杂散起到较好地抑制作用,在减少小数频率合成器杂散指标的同时还大大降低了芯片面积,有效地节约了频率合成器芯片的成本。

技术特征:

1.一种小数调制器输出序列重构方法,其特征在于,包括以下步骤:

2.一种小数频率合成器杂散抑制方法,其特征在于,包括以下步骤:

技术总结

本发明提出了一种小数调制器输出序列重构及小数频率合成器杂散抑制方法,属于小数频率合成器技术领域。本发明由上位机软件计算出Sigma‑Delta调制器的序列值,并由计算机软件将一个周期的序列进行序列重排,把最大值跳变控制在±1范围,再将组成帧结构的序列由串口输入到频率合成器芯片MCU接口单元;当频率合成器芯片读取MCU输出序列后就按接收到的序列对整数分频器进行控制,对整数分频比进行多个周期的平均,从而实现小数功能。本发明通过计算机软件完成复杂调制器和序列重排功能,不占用频率合成器硬件资源和芯片面积,将序列最大跳变值控制在±1范围内,有效地减少了压控振荡器VCO控制端的电压突变,并对小数频率合成器的杂散起到较好地抑制作用。

技术研发人员:曲明,杜明,李斌,徐辉,程理丽,廖春连,冯磊,龚立霖,宋明宇,王尧

受保护的技术使用者:中国电子科技集团公司第五十四研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!