一种叠层结构氧化物忆阻器及制备方法和电子计算机

本申请属于存储器件,尤其涉及一种叠层结构氧化物忆阻器及制备方法和电子计算机。

背景技术:

1、忆阻器通常是以过渡金属氧化物阻变材料为核心,作为一种新兴的存储器件,忆阻器工作机理是在外加电压的条件下,在高电阻状态和低电阻状态之间来回切换。

2、过渡金属氧化物忆阻器在进行操作前需要一个较大电压进行初始化,从而使得阻变材料软击穿形成较粗的氧空位导电细丝,接着在电极两端施加负向操作电压,断裂此较粗的氧空位导电细丝,随后施加正向操作电压会形成较细的氧空位导电细丝,实现了低电阻状态和高电阻状态之间来回切换。然而较大的初始化电压意味着外围驱动电路设计复杂化,复杂化的设置意味着忆阻器失效及良率下降。

技术实现思路

1、有鉴于此,本申请提供了一种叠层结构氧化物忆阻器及制备方法和电子计算机,用于解决现有技术中过渡金属氧化物忆阻器存在的初始化电压较大,导致需要复杂的外围驱动电路的技术问题。

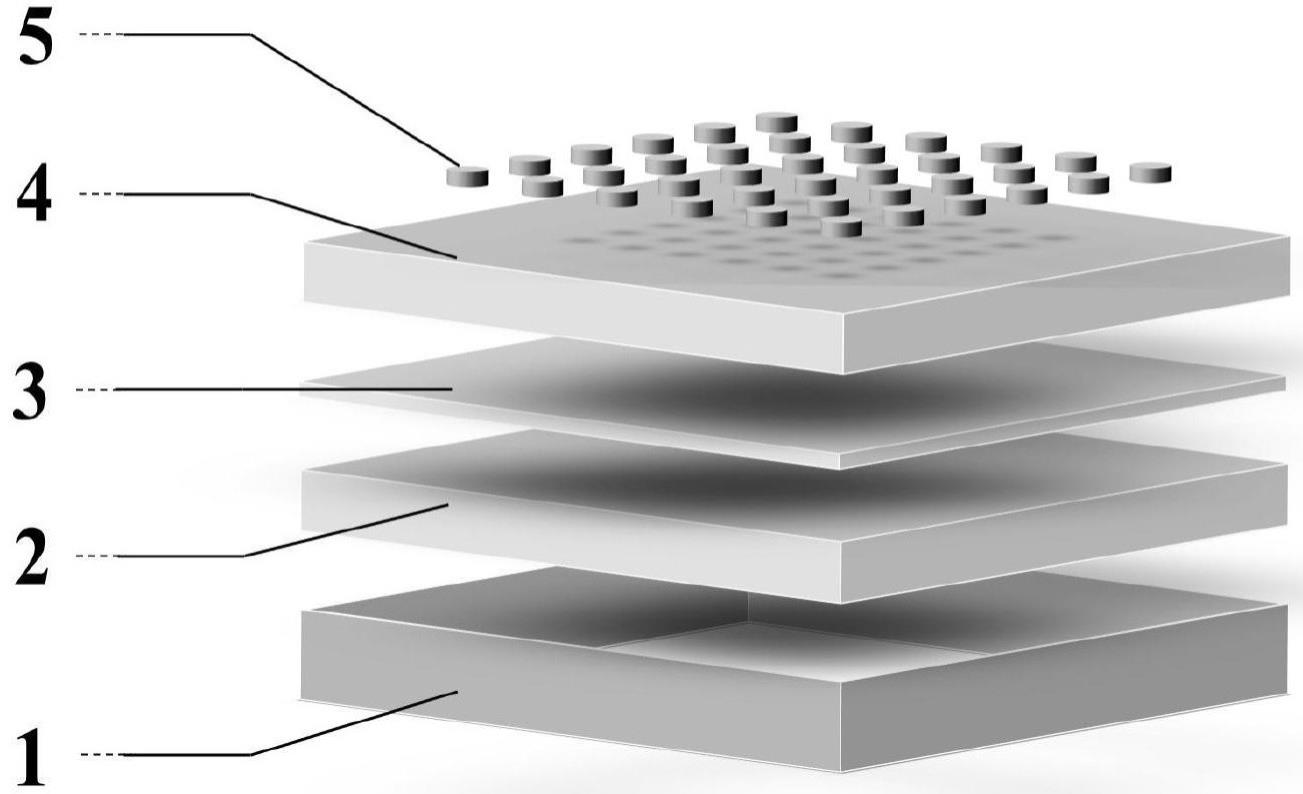

2、本申请第一方面提供了一种叠层结构氧化物忆阻器,包括由下到上依次叠加的导电衬底、阻变复合薄膜以及第二电极;

3、所述阻变复合薄膜为三明治构型的第一氧化铪/掺杂铪的氧化锌/第二氧化铪复合薄膜;

4、所述掺杂铪的氧化锌中铪的掺杂量为5w%~10w%。

5、优选的,阻变复合薄膜中,所述掺杂铪的氧化锌中铪的掺杂量为5w%。

6、优选的,阻变复合薄膜中,所述第一氧化铪的厚度不大于100nm;

7、掺杂铪的氧化锌的厚度不大于50nm;

8、所述第二氧化铪的厚度不大于200nm。

9、优选的,所述导电衬底包括第一电极和基底;

10、所述第一电极覆盖在基底表面。

11、优选的,所述第一电极包括但不限于掺氟氧化锡、掺铟氧化锡、铂金中的至少一种;

12、所述基底包括但不限于导电玻璃、石英玻璃、云母中的至少一种。

13、优选的,所述第二电极包括但不限于金、铂金、氮化钛中的至少一种。

14、优选的,所述基底的厚度为1~2mm;

15、所述第一电极的厚度为200~400nm;

16、所述第二电极的厚度为80~100nm。

17、本申请第二方面提供了一种叠层结构氧化物忆阻器的制备方法,用于制备第一方面所述一种叠层结构氧化物忆阻器,制备方法包括步骤:

18、步骤s1、将第一氧化铪前驱体溶液旋涂在导电衬底表面,烘干后得到叠加氧化铪薄膜的导电衬底;

19、步骤s2、将掺杂铪的氧化锌前驱体溶液旋涂在氧化铪表面,烘干后得到叠加掺杂铪的氧化锌薄膜的导电衬底;

20、步骤s3、将第二氧化铪前驱体溶液旋涂在导电衬底表面,依次烘干、退火后得到叠加阻变复合薄膜的导电衬底;

21、步骤s4、以第二电极为靶材,经磁控溅射得到叠加第二电极的导电衬底。

22、优选的,步骤s1中,第一氧化铪前驱体溶液浓度为0.1~0.2mol/l,旋涂次数为2~3次,烘干温度为100~400℃,时间为10~30min;

23、步骤s2中,掺杂铪的氧化锌溶液浓度为0.1~0.2mol/l,旋涂次数为1~2次,烘干温度为100~400℃,时间为10~30min;

24、步骤s3中,第二氧化铪前驱体溶液浓度为0.1~0.2mol/l,旋涂次数为2~3次,烘干温度为100~400℃,时间为10~30min,退火温度为500~700℃,时间为5~10min。

25、优选的,步骤s1~步骤s3中,所述旋涂的过程包括依次进行低速旋涂和高速旋涂;

26、所述低速旋涂的速度为800~1200r/min,时间为10~15s;

27、所述高速旋涂的速度为2500~3500r/min,时间为15~25s。

28、本申请第三方面提供了一种电子计算机,包括电子计算机硬件和软件,所述电子计算机硬件包括运算器、控制器、输入设备、输出设备以及上述叠层结构氧化物忆阻器。

29、需要说明的是,包括中央处理器等运算器和控制器核心元件、鼠标等输入设备、显卡等输出设备以及叠层结构氧化物忆阻器的计算机硬件,由于以叠层结构氧化物忆阻器作为储存器,叠层结构氧化物忆阻器功耗、读写速度等性能都优于传统的存储器,使得本专利申请提供的电子计算机性能由于常规计算机。

30、综上所述,本申请提供了一种叠层结构氧化物忆阻器及制备方法和电子计算机,叠层结构氧化物忆阻器包括由下到上依次叠加的导电衬底、阻变复合薄膜以及第二电极,阻变复合薄膜为三明治构型的氧化铪/掺杂铪的氧化锌/氧化铪复合薄膜,其中,掺杂铪的氧化锌中铪的掺杂量为5w%~10w%;当对叠层结构氧化物忆阻器施加脉冲电压进行性能测试,测试结果表明在施加1.2v~1.6v脉冲电压后,出现了电流突变,说明掺杂铪的氧化锌与氧化铪复合薄膜复合后,能够增大阻变复合薄膜内的氧空位浓度,促进导电细丝的形成,使忆阻器处于低电阻状态,形成较粗氧空位导电细丝的初始化电压仅为1.2v~1.6v,能够解决现有技术中过渡金属氧化物忆阻器存在的初始化电压较大,导致需要复杂的外围驱动电路的技术问题。

技术特征:

1.一种叠层结构氧化物忆阻器,其特征在于,包括由下到上依次叠加的导电衬底、阻变复合薄膜以及第二电极;

2.根据权利要求1所述的一种叠层结构氧化物忆阻器,其特征在于,阻变复合薄膜中,所述掺杂铪的氧化锌中铪的掺杂量为5w%。

3.根据权利要求1所述的一种叠层结构氧化物忆阻器,其特征在于,阻变复合薄膜中,所述第一氧化铪的厚度不大于100nm;

4.根据权利要求1所述的一种叠层结构氧化物忆阻器,其特征在于,所述导电衬底包括第一电极和基底;

5.根据权利要求1所述的一种叠层结构氧化物忆阻器,其特征在于,所述第二电极包括但不限于金、铂金、氮化钛中的至少一种。

6.根据权利要求4所述的一种叠层结构氧化物忆阻器,其特征在于,所述基底的厚度为1~2mm;

7.权利要求1-6任一项所述的一种叠层结构氧化物忆阻器的制备方法,其特征在于,包括步骤:步骤s1、将第一氧化铪前驱体溶液旋涂在导电衬底表面,烘干后得到叠加氧化铪薄膜的导电衬底;

8.根据权利要求7所述的一种叠层结构氧化物忆阻器的制备方法,其特征在于,步骤s1中,第一氧化铪前驱体溶液浓度为0.1~0.2mol/l,旋涂次数为2~3次,烘干温度为100~400℃,时间为10~30min;

9.根据权利要求7所述的一种叠层结构氧化物忆阻器的制备方法,其特征在于,步骤s1~步骤s3中,所述旋涂的过程包括依次进行低速旋涂和高速旋涂;

10.一种电子计算机,其特征在于,包括电子计算机硬件和软件,所述电子计算机硬件包括运算器、控制器、输入设备、输出设备以及权利要求1-6任一项所述的一种叠层结构氧化物忆阻器。

技术总结

本申请属于存储器件技术领域,尤其涉及一种叠层结构氧化物忆阻器及制备方法和电子计算机;本申请提供的叠层结构氧化物忆阻器包括三明治构型的第一氧化铪/掺杂5w%~10w%铪的氧化锌/第二氧化铪复合薄膜为阻变复合层,掺杂5w%~10w%铪的氧化锌的插入能够增大阻变复合薄膜内的氧空位浓度,促进导电细丝的形成,使忆阻器处于低电阻状态,形成较粗氧空位导电细丝的初始化电压仅为1.2V~1.6V,从而解决现有技术中过渡金属氧化物忆阻器存在的初始化电压较大,导致需要复杂的外围驱动电路的技术问题。

技术研发人员:蒋艳平,冯健豪,白粉蕓,朱建元,唐新桂,刘秋香,唐振华

受保护的技术使用者:广东工业大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!