一种时钟调频系统、方法、设备及存储介质与流程

本申请涉及调频,特别涉及一种时钟调频系统、方法、设备及存储介质。

背景技术:

1、随着asic(application specific integrated circuit,专用集成电路)芯片技术的蓬勃发展,具有密度高、速度快、成本低等优点并且基于risc-v(一个基于精简指令集(risc(reduced instruction set computer,精简指令集计算机))原则的开源指令集架构)架构的芯片得到了广泛的应用。在对基于risc-v架构的芯片进行设计时,系统的时钟设计是重要的一部分。

2、然而,目前针对基于risc-v架构芯片的系统时钟设计方案不够完善,时钟调频设计方案也较少,而好的时钟设计方案,可以保障芯片的正常工作,降低外围电路的emi(electromagnetic interference,电磁干扰)影响,不好的时钟设计方案则可能导致系统的时钟抖动,进而导致芯片不能正常工作,或导致芯片主频必须进行降频操作。

3、因此,如何对基于risc-v架构的芯片进行时钟调频是本领域目前还有待进一步解决的问题。

技术实现思路

1、有鉴于此,本申请的目的在于提供一种时钟调频系统、方法、设备及存储介质,能够对不同场景下的系统总线的时钟频率进行调节,保障基于risc-v架构芯片的正常工作,并降低外围电路的emi的影响。其具体方案如下:

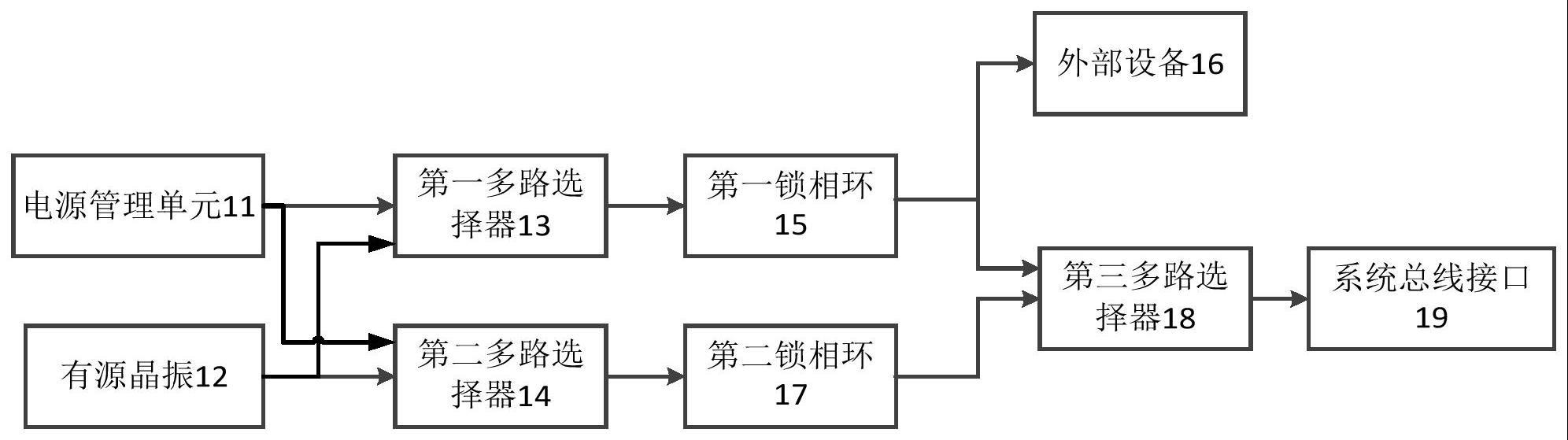

2、第一方面,本申请公开了一种时钟调频系统,包括:

3、用于提供时钟源的电源管理单元和有源晶振;其中,所述有源晶振位于所述基于risc-v架构的目标芯片的外部,所述电源管理单元位于所述目标芯片的内部;

4、与所述电源管理单元和所述有源晶振相连的第一多路选择器和第二多路选择器,用于对所述电源管理单元和所述有源晶振输出的时钟进行选择;

5、与所述第一多路选择器相连的第一锁相环,用于为外部设备提供频率固定的工作时钟;

6、与所述第二多路选择器相连的第二锁相环,用于对所述第二多路选择器选择的时钟进行处理以输出频率可变的时钟;

7、与所述第一锁相环和所述第二锁相环相连的第三多路选择器,用于对所述第一锁相环和所述第二锁相环输出的时钟进行选择,以为系统总线接口提供可调频的工作时钟。

8、可选的,所述电源管理单元,包括:

9、上电复位单元,用于对所述电源管理单元的输出电压进行监控,并在监控到所述输出电压低于预设阈值时,将复位信号置为低电平;

10、用于对所述输出电压的精度进行控制的第一引脚;

11、用于对所述有源晶振的输出频率的调节范围进行控制的第二引脚。

12、可选的,所述系统总线接口为高速总线接口和低速总线接口;其中,所述低速总线接口的时钟通过对所述高速总线接口的时钟进行分频来获取。

13、可选的,所述时钟调频系统,还包括:

14、与所述第三多路选择器、所述高速总线接口和所述低速总线接口相连的分频系数设置单元,用于设置所述低速总线接口的分频系数。

15、可选的,所述第二多路选择器,包括:

16、用于对所述第二锁相环输出的时钟频率进行控制的控制引脚。

17、可选的,所述第一锁相环和所述第二锁相环,包括:

18、鉴频鉴相器,用于对所述第一多路选择器或所述第二多路选择器输出的时钟频率和反馈分频单元反馈的时钟频率进行误差比较;

19、与所述鉴频鉴相器相连的电荷泵,用于进行隔离充电;

20、与所述电荷泵相连的环路滤波器,用于对所述电荷泵输出的电压进行环路滤波处理;

21、与所述环路滤波器相连的压控振荡器,用于将所述环路滤波器输出的电压转换为对应的时钟频率;

22、与所述压控振荡器和所述鉴频鉴相器相连的所述反馈分频单元,用于将所述压控振荡器输出的时钟频率反馈至所述鉴频鉴相器。

23、可选的,所述外部设备包括eflash、spi flash、sd卡。

24、第二方面,本申请公开了一种时钟调频方法,包括:

25、通过电源管理单元和有源晶振为基于risc-v架构的目标芯片提供时钟源;其中,所述有源晶振位于所述目标芯片的外部,所述电源管理单元位于所述目标芯片的内部;

26、通过与所述电源管理单元和所述有源晶振相连的第一多路选择器和第二多路选择器对所述电源管理单元和所述有源晶振输出的时钟进行选择;

27、通过与所述第一多路选择器相连的第一锁相环为外部设备提供频率固定的工作时钟;

28、通过与所述第二多路选择器相连的第二锁相环对所述第二多路选择器选择的时钟进行处理以输出频率可变的时钟;

29、通过与所述第一锁相环和所述第二锁相环相连的第三多路选择器对所述第一锁相环和所述第二锁相环输出的时钟进行选择,以为系统总线接口提供可调频的工作时钟。

30、第三方面,本申请公开了一种电子设备,包括处理器和存储器;其中,所述处理器执行所述存储器中保存的计算机程序时实现前述的时钟调频方法。

31、第四方面,本申请公开了一种计算机可读存储介质,用于存储计算机程序;其中,所述计算机程序被处理器执行时实现前述的时钟调频方法。

32、可见,本申请提出了一种时钟调频系统,包括:用于为基于risc-v架构的目标芯片提供时钟源的电源管理单元和有源晶振;与所述电源管理单元和所述有源晶振相连的第一多路选择器和第二多路选择器,用于对所述电源管理单元和所述有源晶振输出的时钟进行选择;与所述第一多路选择器相连的第一锁相环,用于为外部设备提供频率固定的工作时钟;与所述第二多路选择器相连的第二锁相环,用于对所述第二多路选择器选择的时钟进行处理以输出频率可变的时钟;与所述第一锁相环和所述第二锁相环相连的第三多路选择器,用于对所述第一锁相环和所述第二锁相环输出的时钟进行选择,以为系统总线接口提供可调频的工作时钟。本申请通过创建包含电源管理单元、有源晶振、第一多路选择器、第二多路选择器、第一锁相环第二锁相环相连、第三多路选择器、系统总线接口的时钟调频系统,能够对不同测试环境、不同的输入信号和噪声下的系统总线的时钟频率进行调节,保障基于risc-v架构芯片的正常工作,并降低外围电路的emi的影响。

技术特征:

1.一种时钟调频系统,其特征在于,包括:

2.根据权利要求1所述的时钟调频系统,其特征在于,所述电源管理单元,包括:

3.根据权利要求1所述的时钟调频系统,其特征在于,所述系统总线接口为高速总线接口和低速总线接口;其中,所述低速总线接口的时钟通过对所述高速总线接口的时钟进行分频来获取。

4.根据权利要求3所述的时钟调频系统,其特征在于,还包括:

5.根据权利要求1所述的时钟调频系统,其特征在于,所述第二多路选择器,包括:

6.根据权利要求1所述的时钟调频系统,其特征在于,所述第一锁相环和所述第二锁相环,包括:

7.根据权利要求1至6任一项所述的时钟调频系统,其特征在于,所述外部设备包括eflash、spiflash、sd卡。

8.一种时钟调频方法,其特征在于,应用于权利要求1至7任一项所述的时钟调频系统,包括:

9.一种电子设备,其特征在于,包括处理器和存储器;其中,所述处理器执行所述存储器中保存的计算机程序时实现如权利要求8所述的时钟调频方法。

10.一种计算机可读存储介质,其特征在于,用于存储计算机程序;其中,所述计算机程序被处理器执行时实现如权利要求8所述的时钟调频方法。

技术总结

本申请公开了一种时钟调频系统、方法、设备及存储介质,涉及调频技术领域,包括:用于提供时钟源的电源管理单元和有源晶振;与电源管理单元和有源晶振相连的第一多路选择器和第二多路选择器,用于进行时钟选择;与第一多路选择器相连的第一锁相环,用于为外部设备提供频率固定的工作时钟;与第二多路选择器相连的第二锁相环,用于对第二多路选择器选择的时钟进行处理以输出频率可变的时钟;与第一锁相环和第二锁相环相连的第三多路选择器,用于对第一锁相环和第二锁相环输出的时钟进行选择,以为系统总线接口提供可调频的工作时钟。本申请能够对不同场景下的系统总线的时钟频率进行调节,保障芯片的正常工作,并降低外围电路的EMI的影响。

技术研发人员:赵前程,赵鑫鑫,姜凯,李锐

受保护的技术使用者:山东浪潮科学研究院有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!