基于基本图的并行LDPC译码方法、装置、设备及介质与流程

本发明涉及数据处理,尤其涉及一种基于基本图的并行ldpc译码方法、装置、设备及介质。

背景技术:

1、低密度奇偶校验(low-density parity-check,ldpc)码本质上属于线性分组码的一种,用于纠正传输过程中发生的错误。ldpc码的错误校正能力非常接近香农极限。

2、虽然ldpc码在性能上具有较大的优越性,但是,ldpc码的译码实现方法的复杂度较高,所需要的节点数量较多,导致硬件电路实现成本和难度较高。

技术实现思路

1、本发明实施例提供了一种基于基本图的并行ldpc译码方法、装置、设备及介质,提出了一种软硬件结合实现ldpc译码的方式,代码开发比较灵活,成本低,结合分层调度的节点更新方式,实现高效、高性能的ldpc译码。

2、根据本发明的一方面,提供了一种基于基本图的并行ldpc译码方法,包括:

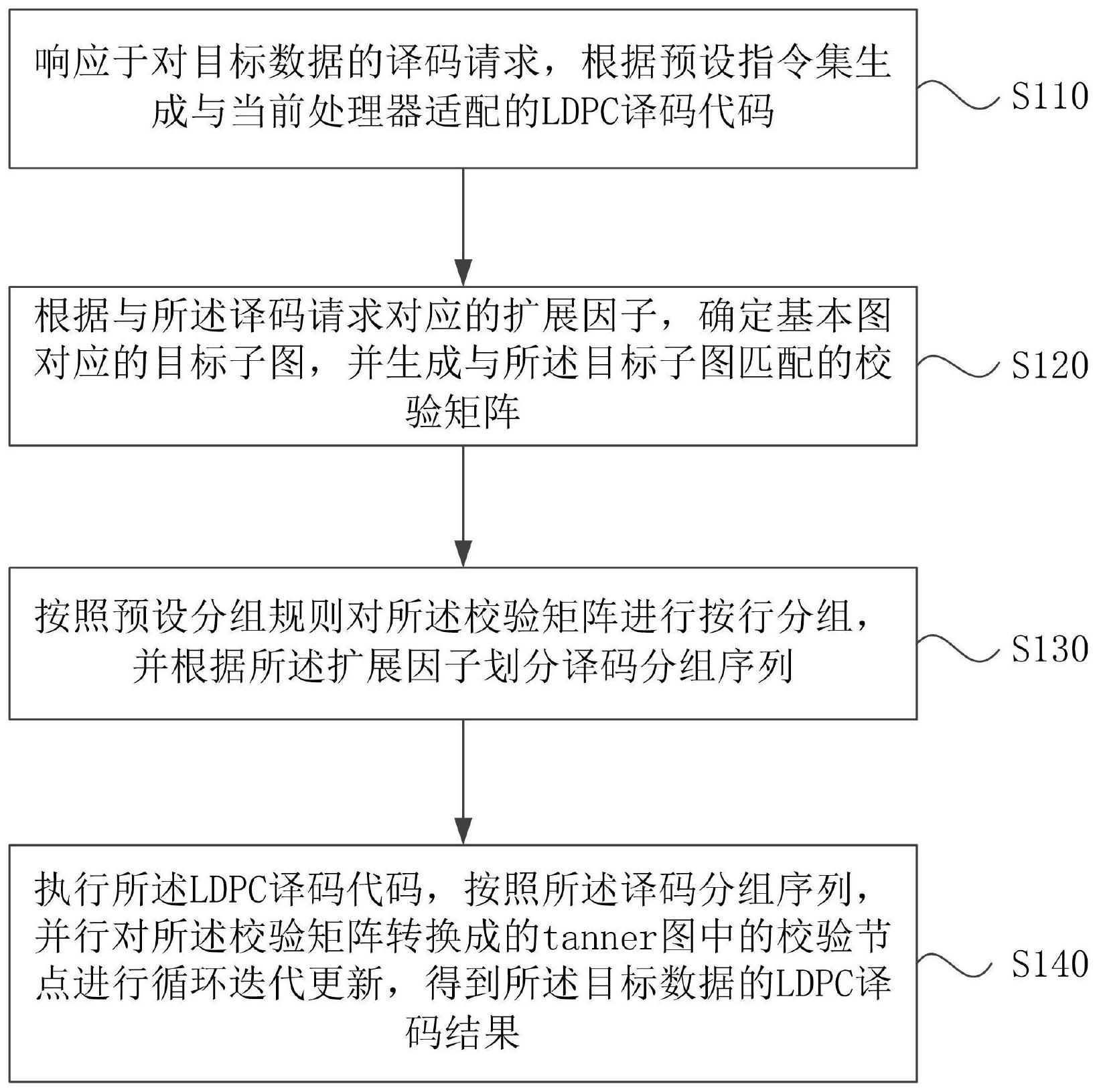

3、响应于对目标数据的译码请求,根据预设指令集生成与当前处理器适配的ldpc译码代码;

4、根据与所述译码请求对应的扩展因子,确定基本图对应的目标子图,并生成与所述目标子图匹配的校验矩阵;

5、按照预设分组规则对所述校验矩阵进行按行分组,并根据所述扩展因子划分译码分组序列;

6、执行所述ldpc译码代码,按照所述译码分组序列,并行对所述校验矩阵转换成的tanner图中的校验节点进行循环迭代更新,得到所述目标数据的ldpc译码结果。

7、根据本发明的另一方面,提供了一种基于基本图的并行ldpc译码装置,包括:

8、译码代码获取模块,用于响应于对目标数据的译码请求,根据预设指令集生成与当前处理器适配的ldpc译码代码;

9、校验矩阵生成模块,用于根据与所述译码请求对应的扩展因子,确定基本图对应的目标子图,并生成与所述目标子图匹配的校验矩阵;

10、矩阵分组模块,用于按照预设分组规则对所述校验矩阵进行按行分组,并根据所述扩展因子划分译码分组序列;

11、节点更新模块,用于执行所述ldpc译码代码,按照所述译码分组序列,并行对所述校验矩阵转换成的tanner图中的校验节点进行循环迭代更新,得到所述目标数据的ldpc译码结果。

12、根据本发明的另一方面,提供了一种电子设备,所述电子设备包括:

13、至少一个处理器;以及

14、与所述至少一个处理器通信连接的存储器;其中,

15、所述存储器存储有可被所述至少一个处理器执行的计算机程序,所述计算机程序被所述至少一个处理器执行,以使所述至少一个处理器能够执行本发明任一实施例所述的基于基本图的并行ldpc译码方法。

16、根据本发明的另一方面,提供了一种计算机可读存储介质,所述计算机可读存储介质存储有计算机指令,所述计算机指令用于使处理器执行时实现本发明任一实施例所述的基于基本图的并行ldpc译码方法。

17、本发明实施例的技术方案,通过响应于对目标数据的译码请求,根据预设指令集生成与当前处理器适配的ldpc译码代码;根据与所述译码请求对应的扩展因子,确定基本图对应的目标子图,并生成与所述目标子图匹配的校验矩阵;按照预设分组规则对所述校验矩阵进行按行分组,并根据所述扩展因子划分译码分组序列;执行所述ldpc译码代码,按照所述译码分组序列,并行对所述校验矩阵转换成的tanner图中的校验节点进行循环迭代更新,得到所述目标数据的ldpc译码结果,解决了相关技术中ldpc译码的硬件电路实现成本和难度较高的问题,提出了一种软硬件结合实现ldpc译码的方式,代码开发比较灵活,成本低,结合分层调度的节点更新方式,实现高效、高性能的ldpc译码。

18、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种基于基本图的并行ldpc译码方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,所述响应于对目标数据的译码请求,根据预设指令集生成与当前处理器适配的ldpc译码代码,包括:

3.根据权利要求1所述的方法,其特征在于,所述根据与所述译码请求对应的扩展因子,确定基本图对应的目标子图,并生成与所述目标子图匹配的校验矩阵,包括:

4.根据权利要求1所述的方法,其特征在于,所述按照预设分组规则对所述校验矩阵进行按行分组,并根据所述扩展因子划分译码分组序列,包括:

5.根据权利要求4所述的方法,其特征在于,所述执行所述ldpc译码代码,按照所述译码分组序列,并行对所述校验矩阵转换成的tanner图中的校验节点进行循环迭代更新,得到所述目标数据的ldpc译码结果,包括:

6.根据权利要求4所述的方法,其特征在于,所述执行所述ldpc译码代码,按照所述译码分组序列,并行对所述校验矩阵转换成的tanner图中的校验节点进行循环迭代更新,得到所述目标数据的ldpc译码结果,包括:

7.根据权利要求6所述的方法,其特征在于,判断j是否满足指令使能判定条件,包括:

8.一种基于基本图的并行ldpc译码装置,其特征在于,包括:

9.一种电子设备,其特征在于,所述电子设备包括:

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质存储有计算机指令,所述计算机指令用于使处理器执行时实现权利要求1-7中任一项所述的基于基本图的并行ldpc译码方法。

技术总结

本发明实施例公开了一种基于基本图的并行LDPC译码方法、装置、设备及介质。该方法包括:响应于对目标数据的译码请求,根据预设指令集生成与当前处理器适配的LDPC译码代码;根据与译码请求对应的扩展因子,确定基本图对应的目标子图,并生成与目标子图匹配的校验矩阵;按照预设分组规则对校验矩阵进行按行分组,并根据扩展因子划分译码分组序列;执行LDPC译码代码,按照译码分组序列,并行对校验矩阵转换成的tanner图中的校验节点进行循环迭代更新,得到目标数据的译码结果。本发明实施例的技术方案,提出了一种软硬件结合实现LDPC译码的方式,结合分层调度的节点更新方式,实现高效、高性能的LDPC译码。

技术研发人员:周康康,张秉耀,张欣瑜

受保护的技术使用者:上海思朗科技有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!