基于忆阻器和晶体管的逻辑门器件、控制方法和电路

本发明涉及信息工程,尤其涉及一种基于忆阻器和晶体管的逻辑门器件、控制方法和电路。

背景技术:

1、集成电路规模的提升得益于不断缩小的晶体管尺寸,但当晶体管尺寸进入原子层级,尺寸缩小也逐渐面临瓶颈。但是,对于固定功能的电路,还有其他方式来缩小电路面积,例如,数字电路通常由一些功能固定的基本单元构成,这些单元由多个晶体管或器件连接实现,但如果能够利用单个器件就能实现这些基本单元的功能,电路面积有望大大减小。

2、目前的研究中,有报道提出了一种基于二维材料的晶体管,可以以单个器件实现门逻辑功能。具体来说,利用二维材料的双表面沟道特性,使晶体管的上极板和下极板能够分别调制沟道的电流,以控制器件的工作状态。相比传统晶体管构成的逻辑门单元,电路面积减半,并且引入光照的变化还可以改变器件的工作方式,实现与或逻辑的变换。但是由于采用的方式是晶体管的双栅结构,电路面积较大。

技术实现思路

1、本发明提供一种基于忆阻器和晶体管的逻辑门器件、控制方法和电路,用以解决现有技术中电路面积较大的缺陷,在能够实现基本的逻辑功能的基础上,减小电路面积。

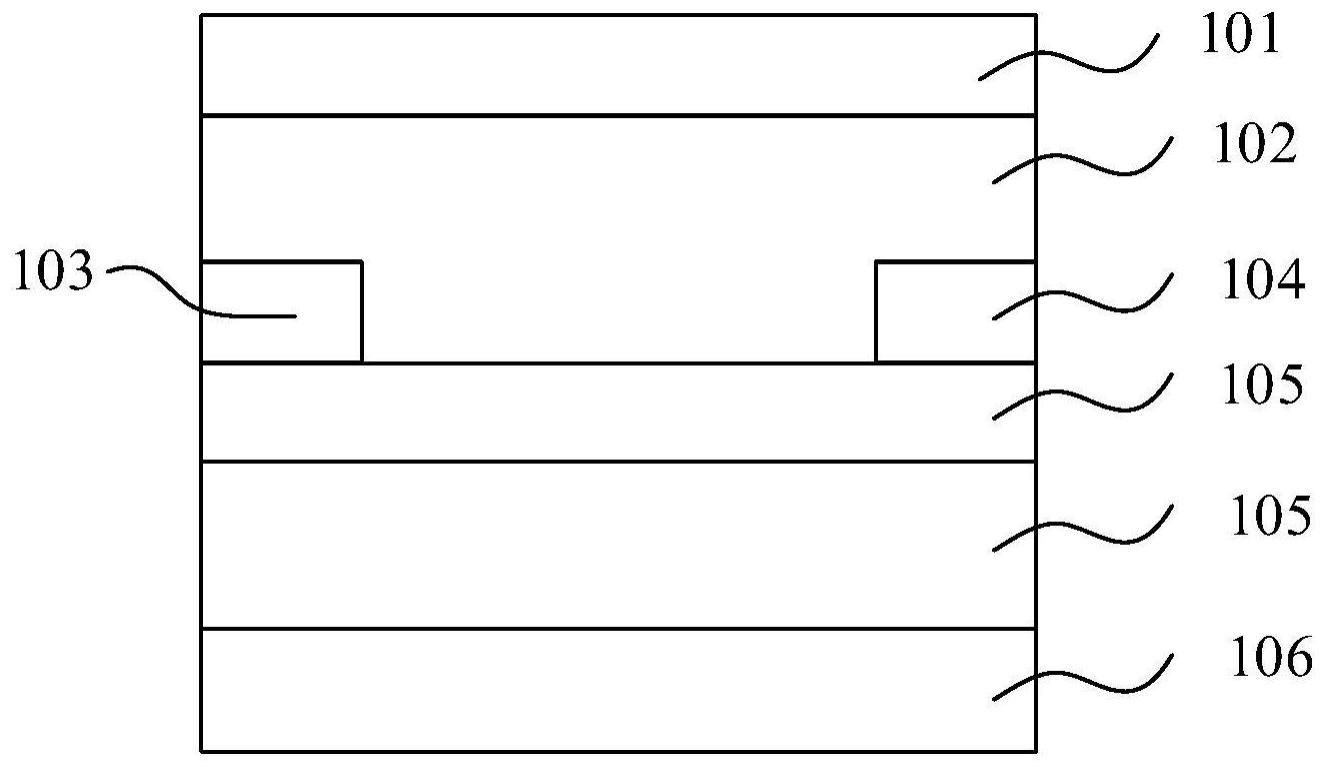

2、本发明提供一种基于忆阻器和晶体管的逻辑门器件,包括:顶电极、阻变层、第一底电极、第二底电极、沟道、栅介质层和栅电极;

3、所述栅介质层形成于所述栅电极上;

4、所述沟道形成于所述栅介质层上;

5、所述第一底电极和所述第二底电极形成于所述沟道上,所述第一底电极和所述第二底电极间隔设置;

6、所述阻变层形成于所述第一底电极、所述第二底电极以及所述间隔上;

7、所述顶电极形成于所述阻变层上;

8、所述顶电极、阻变层、第一底电极和第二底电极构成忆阻器模块,所述第一底电极、第二底电极、沟道、栅介质层和栅电极构成晶体管模块;

9、所述顶电极作为所述逻辑门器件的第一输入端;所述栅电极作为所述逻辑门器件的第二输入端;所述第一底电极和所述第二底电极均作为所述逻辑门器件的输出端。

10、根据本发明提供的一种基于忆阻器和晶体管的逻辑门器件,所述顶电极,用于输入第一脉冲信号;所述第一脉冲信号包括高电平脉冲信号或低电平脉冲信号;

11、所述栅电极,用于输入第二脉冲信号;所述第二脉冲信号包括高电平脉冲信号或低电平脉冲信号;其中,所述高电平脉冲信号作为所述逻辑门器件的逻辑值1;所述低电平脉冲信号作为所述逻辑门器件的逻辑值0;

12、所述第一底电极和所述第二底电极用于输出电流;所述电流用于确定逻辑计算的结果。

13、根据本发明提供的一种基于忆阻器和晶体管的逻辑门器件,所述顶电极由活性金属制成,所述活性金属包括ag、tin和ti中的至少一种。

14、根据本发明提供的一种基于忆阻器和晶体管的逻辑门器件,所述阻变层由具有阻变性质的绝缘材料制成,所述绝缘材料包括hfox、zrox和al2o3中的至少一种。

15、根据本发明提供的一种基于忆阻器和晶体管的逻辑门器件,所述第一底电极和第二底电极由金属制成,所述金属包括pt、ti和pd中的至少一种。

16、根据本发明提供的一种基于忆阻器和晶体管的逻辑门器件,所述沟道由单层或多层二维材料制成,所述二维材料包括二硫化钼。

17、根据本发明提供的一种基于忆阻器和晶体管的逻辑门器件,所述栅介质层由sio2制成。

18、根据本发明提供的一种基于忆阻器和晶体管的逻辑门器件,所述栅电极由si制成。

19、本发明还提供一种基于忆阻器和晶体管的逻辑门器件的控制方法,包括:

20、将所述忆阻器模块中的忆阻器设置为高阻态;

21、向所述顶电极输入第一脉冲信号,向所述栅电极输入第二脉冲信号,以改变所述忆阻器模块中的忆阻器的阻值状态和所述晶体管模块中晶体管的沟道开关状态;

22、向所述第一底电极和所述第二底电极输入预先设置的测算电压;

23、读取所述逻辑门器件的所述第一底电极或第二底电极的输出电流;

24、根据所述输出电流确定所述逻辑门器件的输出电平,以得到逻辑计算的结果。

25、本发明还提供一种逻辑门电路,包括上述任一所述的基于忆阻器和晶体管的逻辑门器件。

26、本发明还提供一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现如上述任一种所述基于忆阻器和晶体管的逻辑门器件的控制方法。

27、本发明还提供一种非暂态计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现如上述任一种所述基于忆阻器和晶体管的逻辑门器件的控制方法。

28、本发明还提供一种计算机程序产品,包括计算机程序,所述计算机程序被处理器执行时实现如上述任一种所述基于忆阻器和晶体管的逻辑门器件的控制方法。

29、本发明提供的一种基于忆阻器和晶体管的逻辑门器件、控制方法和电路,基于忆阻器和晶体管的逻辑门器件包括:顶电极、阻变层、第一底电极、第二底电极、沟道、栅介质层和栅电极;所述栅介质层形成于所述栅电极上;所述沟道形成于所述栅介质层上;所述第一底电极和所述第二底电极形成于所述沟道上,所述第一底电极和所述第二底电极间隔设置;所述阻变层形成于所述第一底电极、所述第二底电极以及所述间隔上;所述顶电极形成于所述阻变层上;所述顶电极、阻变层、第一底电极和第二底电极构成忆阻器模块,所述第一底电极、第二底电极、沟道、栅介质层和栅电极构成晶体管模块;所述顶电极作为所述逻辑门器件的第一输入端;所述栅电极作为所述逻辑门器件的第二输入端;所述第一底电极和所述第二底电极均作为所述逻辑门器件的输出端。本发明利用忆阻器垂直堆叠的方式,自下而上分别由一个二维材料晶体管模块和忆阻器模块组成,使单个逻辑门器件即可实现基本的逻辑功能,减小电路面积。

技术特征:

1.一种基于忆阻器和晶体管的逻辑门器件,其特征在于,包括:顶电极、阻变层、第一底电极、第二底电极、沟道、栅介质层和栅电极;

2.根据权利要求1所述的基于忆阻器和晶体管的逻辑门器件,其特征在于,所述顶电极,用于输入第一脉冲信号;所述第一脉冲信号包括高电平脉冲信号或低电平脉冲信号;

3.根据权利要求1所述的基于忆阻器和晶体管的逻辑门器件,其特征在于,所述顶电极由活性金属制成,所述活性金属包括ag、tin和ti中的至少一种。

4.根据权利要求1所述的基于忆阻器和晶体管的逻辑门器件,其特征在于,所述阻变层由具有阻变性质的绝缘材料制成,所述绝缘材料包括hfox、zrox和al2o3中的至少一种。

5.根据权利要求1所述的基于忆阻器和晶体管的逻辑门器件,其特征在于,所述第一底电极和第二底电极由金属制成,所述金属包括pt、ti和pd中的至少一种。

6.根据权利要求1所述的基于忆阻器和晶体管的逻辑门器件,其特征在于,所述沟道由单层或多层二维材料制成,所述二维材料包括二硫化钼。

7.根据权利要求1所述的基于忆阻器和晶体管的逻辑门器件,其特征在于,所述栅介质层由sio2制成。

8.根据权利要求1所述的基于忆阻器和晶体管的逻辑门器件,其特征在于,所述栅电极由si制成。

9.一种基于忆阻器和晶体管的逻辑门器件的控制方法,采用如权利要求1-8任一所述的基于忆阻器和晶体管的逻辑门器件,其特征在于,包括:

10.一种逻辑门电路,其特征在于,包括权利要求1-8任一所述的基于忆阻器和晶体管的逻辑门器件。

技术总结

本发明提供一种基于忆阻器和晶体管的逻辑门器件、控制方法和电路,逻辑门器件包括:顶电极、阻变层、第一底电极、第二底电极、沟道、栅介质层和栅电极;栅介质层形成于栅电极上;沟道形成于栅介质层上;第一底电极和第二底电极形成于沟道上,第一底电极和第二底电极间隔设置;阻变层形成于第一底电极、第二底电极以及间隔上;顶电极形成于阻变层上;顶电极、阻变层、第一底电极和第二底电极构成忆阻器模块,第一底电极、第二底电极、沟道、栅介质层和栅电极构成晶体管模块;顶电极作为逻辑门器件的第一输入端;栅电极作为逻辑门器件的第二输入端;第一底电极和第二底电极均作为逻辑门器件的输出端。本发明能够实现基本的逻辑功能,减小电路面积。

技术研发人员:田禾,沈阳,高金天

受保护的技术使用者:清华大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!