半导体结构及其形成方法与流程

本申请涉及半导体,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、传统的可变电阻式随机存取存储器元器件为单晶体管单可变电阻(1t1r)结构,其可变电阻结构透过底垫极板与晶体管之源极相连接,并堆叠高介电常数材料为绝缘层以及金属上电极板,在透过上电极板与金属连线连接至位线(bit line,bl)。因此需要对可变电阻元件与结构之相关制程进行开发并需要于cmos制程工艺中添加至少2个额外的光罩,制程上将较为复杂,成本也将有所提升。

2、因此,有必要提供一种更有效、更可靠的技术方案,微缩器件面积,提升器件积集度。

技术实现思路

1、本申请提供一种半导体结构及其形成方法,可以微缩器件面积,提升器件积集度。

2、本申请的一个方面提供一种半导体结构的形成方法,包括:提供半导体衬底,所述半导体衬底中形成有交替分布的阱区以及隔离结构,所述隔离结构在所述半导体衬底中沿x方向延伸,所述半导体衬底表面还形成有沿y方向延伸的栅极结构,所述x方向和所述y方向垂直,所述栅极结构两侧的阱区中形成有掺杂区;在部分所述掺杂区表面依次形成第一外延层和第二外延层,所述第一外延层的掺杂类型与所述掺杂区相反,所述第二外延层的掺杂类型与所述第一外延层相反;在所述第二外延层上方形成阻变式存储器结构。

3、在本申请的一些实施例中,所述掺杂区的掺杂类型为n型,所述第一外延层的掺杂类型为p型,所述第二外延层的掺杂类型为n型,所述掺杂区、第一外延层和第二外延层构成npn选择器结构。

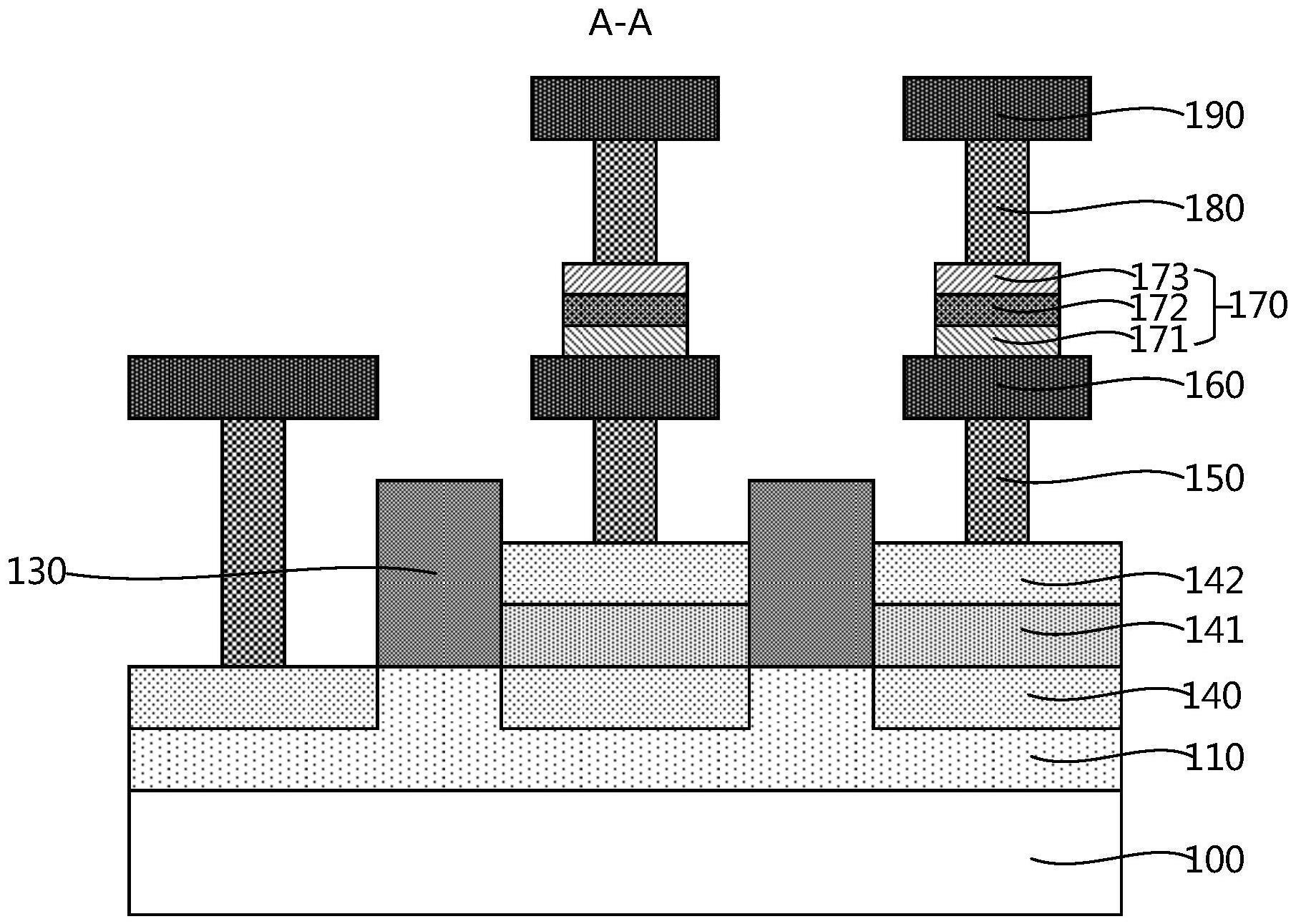

4、在本申请的一些实施例中,所述阻变式存储器结构包括下电极、位于所述下电极表面的阻变层和位于所述阻变层表面的上电极。

5、在本申请的一些实施例中,所述半导体结构的形成方法还包括:在所述第二外延层表面以及未形成所述第一外延层和第二外延层的其余掺杂层表面形成第一接触结构以及位于所述第一接触结构表面的第一金属层,所述阻变式存储器结构形成于所述第一金属层表面。

6、在本申请的一些实施例中,未形成所述第一外延层和第二外延层的其余掺杂层位于所述半导体衬底的外侧。

7、在本申请的一些实施例中,所述半导体结构的形成方法还包括:在所述阻变式存储器结构表面形成第二接触结构以及位于所述第二接触结构表面的第二金属层。

8、在本申请的一些实施例中,在部分所述掺杂区表面依次形成第一外延层和第二外延层的方法包括:选择性磊晶工艺和自掺杂工艺。

9、本申请的另一个方面还提供一种半导体结构,包括:半导体衬底,所述半导体衬底中形成有交替分布的阱区以及隔离结构,所述隔离结构在所述半导体衬底中沿x方向延伸,所述半导体衬底表面还形成有沿y方向延伸的栅极结构,所述x方向和所述y方向垂直,所述栅极结构两侧的阱区中形成有掺杂区;第一外延层和第二外延层,依次位于部分所述掺杂区表面,所述第一外延层的掺杂类型与所述掺杂区相反,所述第二外延层的掺杂类型与所述第一外延层相反;阻变式存储器结构,位于所述第二外延层上方。

10、在本申请的一些实施例中,所述掺杂区的掺杂类型为n型,所述第一外延层的掺杂类型为p型,所述第二外延层的掺杂类型为n型,所述掺杂区、第一外延层和第二外延层构成npn选择器结构。

11、在本申请的一些实施例中,所述阻变式存储器结构包括下电极、位于所述下电极表面的阻变层和位于所述阻变层表面的上电极。

12、在本申请的一些实施例中,所述半导体结构还包括:位于所述第二外延层表面以及未形成所述第一外延层和第二外延层的其余掺杂层表面的第一接触结构以及位于所述第一接触结构表面的第一金属层,所述阻变式存储器结构位于所述第一金属层表面。

13、在本申请的一些实施例中,未形成所述第一外延层和第二外延层的其余掺杂层位于所述半导体衬底的外侧。

14、在本申请的一些实施例中,所述半导体结构还包括:位于所述阻变式存储器结构表面的第二接触结构以及位于所述第二接触结构表面的第二金属层。

15、本申请提供一种半导体结构及其形成方法,在源极和漏极与阻变式存储器结构之间形成pnp选择器,可以微缩器件面积,提升器件积集度。

技术特征:

1.一种半导体结构的形成方法,其特征在于,包括:

2.如权利要求1所述的半导体结构的形成方法,其特征在于,所述掺杂区的掺杂类型为n型,所述第一外延层的掺杂类型为p型,所述第二外延层的掺杂类型为n型,所述掺杂区、第一外延层和第二外延层构成npn选择器结构。

3.如权利要求1所述的半导体结构的形成方法,其特征在于,所述阻变式存储器结构包括下电极、位于所述下电极表面的阻变层和位于所述阻变层表面的上电极。

4.如权利要求1所述的半导体结构的形成方法,其特征在于,还包括:在所述第二外延层表面以及未形成所述第一外延层和第二外延层的其余掺杂层表面形成第一接触结构以及位于所述第一接触结构表面的第一金属层,所述阻变式存储器结构形成于所述第一金属层表面。

5.如权利要求4所述的半导体结构的形成方法,其特征在于,未形成所述第一外延层和第二外延层的其余掺杂层位于所述半导体衬底的外侧。

6.如权利要求1所述的半导体结构的形成方法,其特征在于,还包括:在所述阻变式存储器结构表面形成第二接触结构以及位于所述第二接触结构表面的第二金属层。

7.如权利要求1所述的半导体结构的形成方法,其特征在于,在部分所述掺杂区表面依次形成第一外延层和第二外延层的方法包括:选择性磊晶工艺和自掺杂工艺。

8.一种半导体结构,其特征在于,包括:

9.如权利要求8所述的半导体结构,其特征在于,所述掺杂区的掺杂类型为n型,所述第一外延层的掺杂类型为p型,所述第二外延层的掺杂类型为n型,所述掺杂区、第一外延层和第二外延层构成npn选择器结构。

10.如权利要求8所述的半导体结构,其特征在于,所述阻变式存储器结构包括下电极、位于所述下电极表面的阻变层和位于所述阻变层表面的上电极。

11.如权利要求8所述的半导体结构,其特征在于,还包括:位于所述第二外延层表面以及未形成所述第一外延层和第二外延层的其余掺杂层表面的第一接触结构以及位于所述第一接触结构表面的第一金属层,所述阻变式存储器结构位于所述第一金属层表面。

12.如权利要求11所述的半导体结构,其特征在于,未形成所述第一外延层和第二外延层的其余掺杂层位于所述半导体衬底的外侧。

13.如权利要求8所述的半导体结构,其特征在于,还包括:位于所述阻变式存储器结构表面的第二接触结构以及位于所述第二接触结构表面的第二金属层。

技术总结

本申请提供半导体结构及其形成方法,所述半导体结构包括:半导体衬底,所述半导体衬底中形成有交替分布的阱区以及隔离结构,所述隔离结构在所述半导体衬底中沿X方向延伸,所述半导体衬底表面还形成有沿Y方向延伸的栅极结构,所述X方向和所述Y方向垂直,所述栅极结构两侧的阱区中形成有掺杂区;第一外延层和第二外延层,依次位于部分所述掺杂区表面,所述第一外延层的掺杂类型与所述掺杂区相反,所述第二外延层的掺杂类型与所述第一外延层相反;阻变式存储器结构,位于所述第二外延层上方。本申请提供一种半导体结构及其形成方法,在源极和漏极与阻变式存储器结构之间形成PNP选择器,可以微缩器件面积,提升器件积集度。

技术研发人员:章纬,卜伟海

受保护的技术使用者:北方集成电路技术创新中心(北京)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!