赝电阻电路及放大器电路的制作方法

本申请涉及电路设计,特别是涉及一种赝电阻电路及放大器电路。

背景技术:

1、随着科学技术的发展,电子设备在生物医学领域被广泛利用,然而生物医学领域的电信号通常非常微弱,例如对人体生理信号进行检测时,电极与皮肤的接触经常会使生理信号引入较大的直流成分或超低频率成分的干扰信号,在人体运动时,生理信号中也会叠加运动伪影噪声干扰信号,这些干扰信号都是极低频率的信号,因此生物医学领域来说,需要设计噪声效率因子低的电路,这样的电路需要极低截止频率的滤波器去滤除干扰信号,即需要特别大的电阻和电容来构建超大的时间常数。而在集成电路工艺中,多晶硅电阻或扩散电阻等电阻率较低,所以使用多晶硅电阻制作大电阻或制作大电容都需要占用特别大的面积,而且会引入特别大的寄生参数。

2、传统技术中,通过晶体管构成伪电阻电路结构,能够提供大电阻,然而,传统技术中的伪电阻电路的线性度较差。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种能够具备较好的线性度,使得信号的传输更为准确的赝电阻电路及放大器电路。

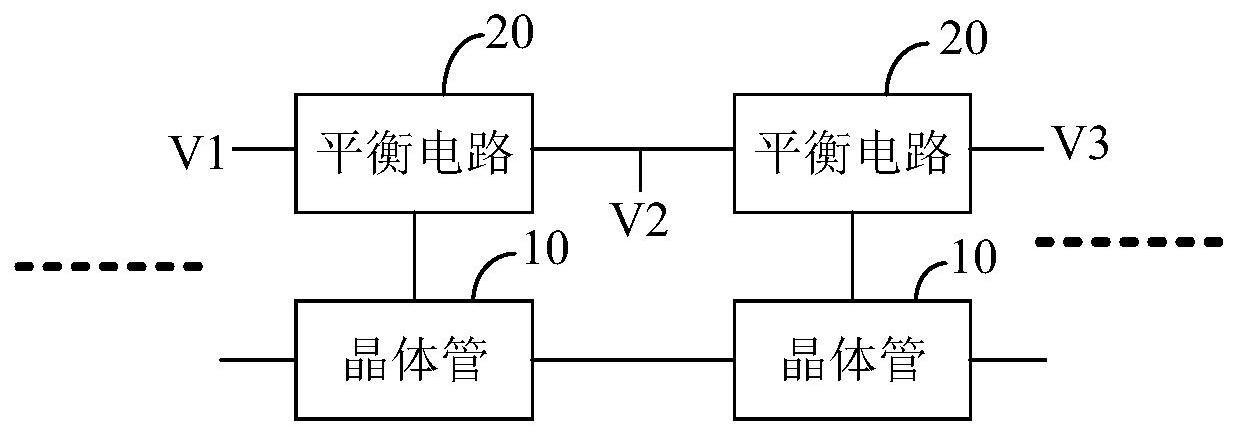

2、一种赝电阻电路,包括:多个晶体管,相邻两个所述晶体管中,其中一个晶体管的第一端与另一个晶体管的第二端连接;多个平衡电路,每一所述平衡电路分别对应与一所述晶体管的目标端对应连接,其中,所述多个平衡电路连接的目标端包括所述晶体管的控制端和衬底端中的至少一个,所述平衡电路用于平衡所述目标端分别与所述平衡电路的第一端和第二端之间的电压,所述平衡电路的第一端的第一端点电压和所述平衡电路的第二端的第二端点电压之和小于阈值电压,其中,所述阈值电压与所述平衡电路连接的目标端相关。

3、在其中一个实施例中,所述多个平衡电路包括多个第一平衡电路,其中,每一所述第一平衡电路分别对应与一所述晶体管的控制端连接。

4、在其中一个实施例中,所述多个平衡电路包括多个第二平衡电路,其中,每一所述第二平衡电路分别对应与一所述晶体管的衬底端连接。

5、在其中一个实施例中,所述多个平衡电路包括多个所述第一平衡电路和多个所述第二平衡电路。

6、在其中一个实施例中,所述平衡电路包括第一平衡单元和第二平衡单元,所述第一平衡单元的第一端作为所述平衡电路的第一端,所述第一平衡单元的第二端分别与所述目标端、所述第二平衡单元的第一端连接,所述第二平衡单元的第二端作为所述平衡电路的第二端,其中,所述第一平衡单元的电容值和所述第二平衡单元的电容值相等。

7、在其中一个实施例中,所述第一平衡单元包括第一电容,所述第二平衡单元包括第二电容。

8、在其中一个实施例中,所述第一平衡单元包括多个第一电容,所述第二平衡单元包括多个第二电容,其中,多个所述第一电容依次串联连接,多个所述第二电容依次串联连接。

9、在其中一个实施例中,所述第一平衡单元包括多个第一电容,所述第二平衡单元包括多个第二电容,其中,多个所述第一电容并联连接,多个所述第二电容并联连接。

10、在其中一个实施例中,所述第一平衡单元包括多个第一电容,所述第二平衡单元包括多个第二电容,其中,所述多个第一电容中的至少部分并联连接,至少部分所述第一电容串联连接,所述多个第二电容中的至少部分并联连接,至少部分所述第二电容串联连接。

11、在其中一个实施例中,所述平衡电路的第一端和第二端中的一个与所述晶体管的第一端连接,和/或,所述平衡电路的第一端和第二端中的另一个与所述晶体管的第二端连接。

12、在其中一个实施例中,所述晶体管包括mos管、bjt寄生晶体管、pn结寄生晶体管中的一种。

13、一种放大器电路,包括前述的赝电阻电路和运算放大器,其中,所述赝电阻电路分别与所述运算放大器的输入端和输出端连接。

14、上述赝电阻电路及放大器电路,该赝电阻电路,通过设置多个晶体管,每相邻两个晶体管中,其中一个晶体管的第一端与另一个晶体管的第二端连接,从而多个晶体管依次串联连接,且多个晶体管都保持关断的状态,从而构成了一个具备较大的电阻值的赝电阻电路。通过设置多个平衡电路,每一平衡电路分别对应与一晶体管的目标端对应连接,而每一个平衡电路连接的目标端包括晶体管的控制端或衬底端,平衡电路能够平衡晶体管的目标端分别与平衡电路的第一端和第二端之间的电压,也就是说平衡电路能够将晶体管的目标端上存在的电荷均匀的导向平衡电路的两端,从而使得晶体管的目标端的电位不受额外电荷的影响。一般而言,晶体管在工艺制造过程中目标端会存在电荷,例如静电电荷,而这个电荷没有回路释放,就会累积在晶体管的目标端上,从而导致晶体管的目标端的电位不稳定,而晶体管的目标端的电位会影响晶体管的第一端和第二端之间的电阻,其晶体管的电阻值不稳定,进而使得晶体管的第一端和第二端之间的电阻率不稳定,这样,由多个晶体管构成的赝电阻电路的线性度会受晶体管的目标端上累积的电荷的影响,导致赝电阻电路的线性度较差。本申请实施例提供的赝电阻电路中通过设置平衡电路,使得晶体管的目标端的电压(或电位)能够保持平衡,进而使得晶体管的电阻值保持稳定,且晶体管的目标端的电位稳定后,晶体管的第一端和第二端之间的电阻率也就稳定了,在各个晶体管的电阻率都稳定的情况下,由多个晶体管构成的赝电阻电路的线性度会更好。当将本申请中的赝电阻电路应用于采集微弱的电信号的电子电路中时,能够提高该电子电路,例如放大器电路,采集信号的准确性。

技术特征:

1.一种赝电阻电路,其特征在于,包括:

2.根据权利要求1所述的赝电阻电路,其特征在于,所述多个平衡电路包括多个第一平衡电路,其中,每一所述第一平衡电路分别对应与一所述晶体管的控制端连接;或,

3.根据权利要求1所述的赝电阻电路,其特征在于,所述平衡电路包括第一平衡单元和第二平衡单元,所述第一平衡单元的第一端作为所述平衡电路的第一端,所述第一平衡单元的第二端分别与所述目标端、所述第二平衡单元的第一端连接,所述第二平衡单元的第二端作为所述平衡电路的第二端,其中,所述第一平衡单元的电容值和所述第二平衡单元的电容值相等。

4.根据权利要求3所述的赝电阻电路,其特征在于,所述第一平衡单元包括第一电容,所述第二平衡单元包括第二电容。

5.根据权利要求3所述的赝电阻电路,其特征在于,所述第一平衡单元包括多个第一电容,所述第二平衡单元包括多个第二电容,其中,多个所述第一电容依次串联连接,多个所述第二电容依次串联连接。

6.根据权利要求3所述的赝电阻电路,其特征在于,所述第一平衡单元包括多个第一电容,所述第二平衡单元包括多个第二电容,其中,多个所述第一电容并联连接,多个所述第二电容并联连接。

7.根据权利要求3所述的赝电阻电路,其特征在于,所述第一平衡单元包括多个第一电容,所述第二平衡单元包括多个第二电容,其中,所述多个第一电容中的至少部分并联连接,至少部分所述第一电容串联连接,所述多个第二电容中的至少部分并联连接,至少部分所述第二电容串联连接。

8.根据权利要求1所述的赝电阻电路,其特征在于,所述平衡电路的第一端和第二端中的一个与所述晶体管的第一端连接,和/或,所述平衡电路的第一端和第二端中的另一个与所述晶体管的第二端连接。

9.根据权利要求1所述的赝电阻电路,其特征在于,所述晶体管包括mos管、bjt寄生晶体管、pn结寄生晶体管中的一种。

10.一种放大器电路,其特征在于,包括如权利要求1-9任一项所述的赝电阻电路和运算放大器,其中,所述赝电阻电路分别与所述运算放大器的输入端和输出端连接。

技术总结

本申请涉及一种赝电阻电路及放大器电路。赝电阻电路包括:多个晶体管,相邻两个晶体管中,其中一个晶体管的第一端与另一个晶体管的第二端连接;多个平衡电路,每一平衡电路分别对应与一晶体管的目标端对应连接,其中,多个平衡电路连接的目标端包括晶体管的控制端和衬底端中的至少一个,平衡电路用于平衡目标端分别与平衡电路的第一端和第二端之间的电压,平衡电路的第一端的第一端点电压和平衡电路的第二端的第二端点电压之和小于阈值电压,其中,阈值电压与平衡电路连接的目标端相关。本申请中的赝电阻电路的线性度较好。

技术研发人员:马亚奇,徐忠,简汎宇,廖明亮,郑君华

受保护的技术使用者:合芯科技(苏州)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!