半导体器件及其制备方法、电子设备与流程

本申请涉及半导体,特别是涉及一种半导体器件及其制备方法、电子设备。

背景技术:

1、随着集成电路技术的发展,器件的关键尺寸日益缩小,单个芯片所包含的器件种类及数量随之增加,使得工艺生产中的任何微小差异都可能对器件性能造成影响。

2、为了尽可能降低产品的成本,人们希望在有限的衬底上做出尽可能多的器件单元。自从摩尔定律问世以来,业界提出了各种半导体结构设计和工艺优化,以满足人们对当前产品的需求。

技术实现思路

1、基于此,本申请实施例提供了一种半导体器件及其制备方法、电子设备,可以避免源/漏极的表面氧化,同时工艺形成简单,成本低。

2、提供一种半导体器件的制备方法,包括:

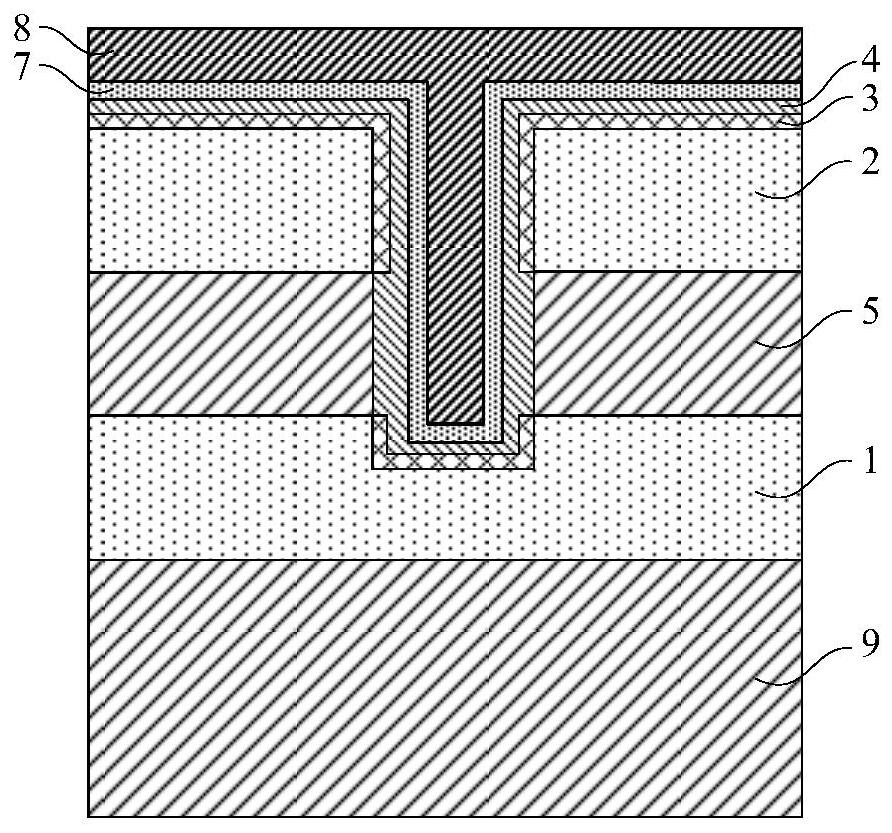

3、提供在垂直于衬底的方向上依次形成的至少包含第一源/漏极、层间介质层和第二源/漏极的堆叠结构;

4、在所述堆叠结构形成通孔,所述通孔沿垂直于所述衬底的方向贯穿所述第二源/漏极及所述层间介质层,且至少延伸至所述第一源/漏极;

5、至少于所述层间介质层暴露于所述通孔的侧壁,在所述侧壁形成与所述层间介质层为吸附关系的自组装单分子层,使得通孔内露出自组装单分子层未覆盖的第一源/漏极和第二源/漏极;

6、以所述自组装单分子层作为掩膜,于所述第一源/漏极及所述第二源/漏极上形成接触层;

7、去除所述自组装单分子层;所述第一源/漏极上的接触层和第二源/漏极上的接触层通过所述层间介质层隔离;

8、于所述通孔内的侧壁形成半导体层,半导体层与第一源/漏极和第二源/漏极上的所述接触层连接。

9、一些实施例中,所述接触层为抗氧化导电层和/或降低肖特基势垒的膜层。

10、一些实施例中,所述自组装单分子层包括长链有机分子;所述长链有机分子与所述层间介质层的分子通过化学吸附结合。

11、一些实施例中,所述长链有机分子至少含有氟链烷基,所述氟链烷基为所述长链有机分子的尾基;

12、采用原子层沉积工艺形成所述接触层;所述层间介质层包括非金属氧化物层。

13、一些实施例中,所述层间介质层表面至少具有羟基;

14、所述长链有机分子中的所述氟链烷基与所述层间介质层表面的所述羟基通过化学吸附结合。

15、一些实施例中,所述层间介质层包括:表面具有羟基的氧化硅膜层。

16、一些实施例中,所述自组装单分子层的组成成分包括1h,1h,2h,2h-全氟辛基三氯硅烷和/或(十七氟-1,1,2,2-四氢癸基)三乙氧基硅烷;

17、形成与所述层间介质层为吸附关系的所述自组装单分子层的过程中,第一反应气体至少包括氨气。

18、一些实施例中,以所述自组装单分子层作为掩膜,于所述通孔内形成所述接触层的过程中,反应前驱体至少包括五甲基二胺钽配合物,第二反应气体至少包括氨气,反应温度为225℃~300℃。

19、一些实施例中,采用水蒸气水解工艺或硅烷热解工艺去除所述自组装单分子层。

20、一些实施例中,所述接触层包含钽金属氮化物层。

21、提供一种半导体器件,由上述任一实施例所述的制备方法制备获得。

22、一些实施例中,所述半导体层各区域的厚度相同。

23、一些实施例中,所述第一源/漏极上的所述接触层的图案与所述第一源/漏极的图案重叠;

24、所述第二源/漏极上的接触层的图案与所述第二源/漏极的图案重叠。

25、一些实施例中,所述接触层包括钽金属氮化物层。

26、一些实施例中,所述层间介质层包含氧化硅膜层。

27、提供一种电子设备,包含上述任一实施例所述的半导体器件。

28、本申请提供的半导体器件及其制备方法、半导体器件,可以/至少具有以下优点:

29、本申请实施例中,通过选择性地在层间介质层暴露于通孔的侧壁形成吸附于层间介质层的自组装单分子层,并以自组装单分子层作为掩膜,在第一源/漏极及第二源/漏极暴露于通孔的侧壁上形成接触层。因此,采用本申请实施例在半导体层和源电极或漏电极之间形成接触层,工艺简单,成本低。

技术特征:

1.一种半导体器件的制备方法,其特征在于,包括:

2.根据权利要求1所述的半导体器件的制备方法,其特征在于,所述接触层包含抗氧化导电层,和/或,降低肖特基势垒的膜层。

3.根据权利要求1所述的半导体器件的制备方法,其特征在于,

4.根据权利要求3所述的半导体器件的制备方法,其特征在于,所述长链有机分子至少含有氟链烷基,所述氟链烷基为所述长链有机分子的尾基;

5.根据权利要求4所述的半导体器件的制备方法,其特征在于,所述层间介质层的表面至少具有羟基;

6.根据权利要求5所述的半导体器件的制备方法,其特征在于,所述层间介质层包括:表面具有羟基的氧化硅膜层。

7.根据权利要求1所述的半导体器件的制备方法,其特征在于,所述自组装单分子层的组成成分包括1h,1h,2h,2h-全氟辛基三氯硅烷,和/或,(十七氟-1,1,2,2-四氢癸基)三乙氧基硅烷;

8.根据权利要求1所述的半导体器件的制备方法,其特征在于,以所述自组装单分子层作为掩膜,于所述通孔内形成所述接触层的过程中,反应前驱体至少包括五甲基二胺钽配合物,第二反应气体至少包括氨气,反应温度为225℃~300℃。

9.根据权利要求1所述的半导体器件的制备方法,其特征在于,采用水蒸气水解工艺或硅烷热解工艺去除所述自组装单分子层。

10.根据权利要求2所述的半导体器件的制备方法,其特征在于,所述接触层包含钽金属氮化物层。

11.一种半导体器件,其特征在于,所述半导体器件采用如权利要求1至10中任一项所述的制备方法制备获得。

12.根据权利要求11所述的半导体器件,其特征在于,所述半导体层各区域的厚度相同。

13.根据权利要求11所述的半导体器件,其特征在于,所述第一源/漏极上的所述接触层的图案与所述第一源/漏极的图案重叠;

14.根据权利要求11所述的半导体器件,其特征在于,所述接触层包括钽金属氮化物层。

15.根据权利要求11所述的半导体器件,其特征在于,所述层间介质层包含氧化硅膜层。

16.一种电子设备,其特征在于,包括如权利要求11至15中任一项所述的半导体器件。

技术总结

本申请涉及一种半导体器件及其制备方法、电子设备。所述半导体器件的制备方法包括:在堆叠结构形成通孔,通孔沿垂直于衬底的方向贯穿第二源/漏极及层间介质层,且至少延伸至第一源/漏极;至少于层间介质层暴露于通孔的侧壁,在侧壁形成与层间介质层为吸附关系的自组装单分子层,使得通孔内露出自组装单分子层未覆盖的第一源/漏极和第二源/漏极;以自组装单分子层作为掩膜,于第一源/漏极及第二源/漏极上形成接触层;去除自组装单分子层;第一源/漏极上的接触层和第二源/漏极上的接触层通过层间介质层隔离;于通孔内的侧壁形成半导体层,半导体层与第一源/漏极和第二源/漏极上的接触层连接。工艺简单,成本低。

技术研发人员:栾庆洁,段新绿,项金娟,王桂磊,赵超

受保护的技术使用者:北京超弦存储器研究院

技术研发日:

技术公布日:2025/3/3

- 还没有人留言评论。精彩留言会获得点赞!