一种逐次逼近式模拟数字转换器及设备的制作方法

本发明涉及集成电路领域,特别是涉及一种逐次逼近式模拟数字转换器及设备。

背景技术:

1、sar adc(successive approximation register adc,逐次逼近式模拟数字转换器)因其具备的高精度及低功耗的特点在各类设备中得到广泛应用。sar adc的前端通常需要设置采样保持电路来对输入信号进行采样,相关技术中的采样保持电路通常为nmos与pmos构成的传输门电路,在实际应用中当过压输入至传输门电路时,传输门电路中的pmos会产生亚阈值导通的情况,导致过压输入通过pmos管为电容矩阵进行反向充电,进而影响sar adc输出结果的准确性。因此,如何避免过压输入对sar adc的输出结果的影响是至关重要的。

技术实现思路

1、本发明的目的是提供一种逐次逼近式模拟数字转换器及设备,在过压输入时采样保持模块中的第二晶体管不会工作在亚阈值状态,保证电容阵列的第一端的电压的稳定,进而保证逐次逼近式模拟数字转换器的精度。

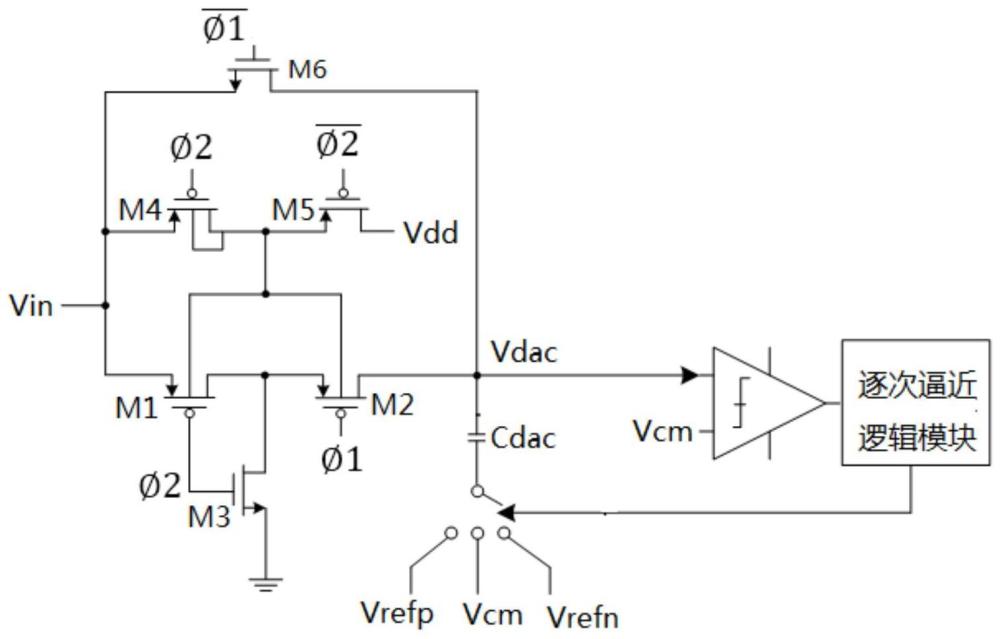

2、为解决上述技术问题,本发明提供了一种逐次逼近式模拟数字转换器,包括采样保持模块、比较模块、逐次逼近逻辑模块以及电容阵列,其中,所述采样保持模块包括第一晶体管、第二晶体管以及第三晶体管;

3、所述比较模块用于将所述采样保持模块基于输入信号输出的采样电压与参考电压进行比较并输出比较结果,所述逐次逼近逻辑模块用于基于所述比较结果生成用于调节所述电容阵列的第一端上的电压的逻辑信号,所述电容阵列的第二端与所述采样保持模块的输出端连接;

4、所述第一晶体管的控制端和所述第三晶体管的控制端均用于输入所述逻辑信号,所述第二晶体管的控制端用于输入采样控制信号,所述第一晶体管的输入端用于输入所述输入信号,所述第一晶体管的输出端与所述第二晶体管的输入端连接且连接的公共端与所述第三晶体管的输出端连接,所述第三晶体管的输入端接地,所述第二晶体管的输出端用于输出所述采样电压。

5、优选的,还包括用于防止所述第一晶体管的体端以及所述第二晶体管的体端漏电的体端防漏电模块。

6、优选的,所述体端防漏电模块包括第四晶体管和第五晶体管;

7、所述第四晶体管的输入端用于接收所述输入信号,所述第四晶体管的输出端与自身的体端以及所述第五晶体管的输入端连接,所述第四晶体管的输出端与所述第五晶体管的输入端连接的公共端与所述第一晶体管的体端以及所述第二晶体管的体端连接;

8、所述第四晶体管的控制端用于输入所述逻辑信号,所述第五晶体管的控制端用于输入与所述逻辑信号反相的信号,所述第五晶体管的输出端用于输入电源电压。

9、优选的,所述第四晶体管和所述第五晶体管均为pmos。

10、优选的,所述电容阵列包括电容以及切换开关;

11、所述电容的上极板作为所述电容阵列的第一端与所述采样保持模块的输出端连接,所述电容的下极板与所述切换开关的不动端连接,所述切换开关的第一动端用于输入第一预设固定电压,所述切换开关的第二动端用于输入所述参考电压,所述切换开关的第二动端用于输入第二预设固定电压。

12、优选的,所述第一晶体管和所述第二晶体管均为pmos,所述第三晶体管为nmos。

13、优选的,还包括采样扩展模块;

14、所述采样扩展模块的输入端与所述采样保持模块的输入端均用于接收输入信号,所述采样扩展模块的输出端与所述采样保持模块的输出端均用于向所述比较模块输出所述采样电压,且所述采样扩展模块导通所需的导通电压与所述采样保持模块导通所需的导通电压不同。

15、优选的,所述采样扩展模块为第六晶体管;

16、所述第六晶体管的输出端与所述第一晶体管的输入端连接,所述第六晶体管的输出端与所述第二晶体管的输出端连接,所述第六晶体管的控制端用于接收与所述采样电压的电平相反的电压。

17、优选的,所述第六晶体管为nmos。

18、为解决上述技术问题本申请还提供了一种设备,包括上述任一逐次逼近式模拟数字转换器。

19、本发明的有益效果在于提供了一种逐次逼近式模拟数字转换器及设备,包括采样保持模块、比较模块、逐次逼近逻辑模块以及电容阵列,采样保持模块包括第一晶体管、第二晶体管以及第三晶体管。第一晶体管至第三晶体管组成动态开关结构,能够在进行参考电压与采样电压逐次比较的转换阶段将电容阵列的第一端的电压与输入信号进行隔离,即使在过压输入时采样保持模块中的第二晶体管也不会工作在亚阈值状态,从而保证电容阵列的第一端的电压的稳定性,进而保证逐次逼近式模拟数字转换器的精度。

技术特征:

1.一种逐次逼近式模拟数字转换器,其特征在于,包括采样保持模块、比较模块、逐次逼近逻辑模块以及电容阵列,其中,所述采样保持模块包括第一晶体管、第二晶体管以及第三晶体管;

2.如权利要求1所述的逐次逼近式模拟数字转换器,其特征在于,还包括用于防止所述第一晶体管的体端以及所述第二晶体管的体端漏电的体端防漏电模块。

3.如权利要求2所述的逐次逼近式模拟数字转换器,其特征在于,所述体端防漏电模块包括第四晶体管和第五晶体管;

4.如权利要求3所述的逐次逼近式模拟数字转换器,其特征在于,所述第四晶体管和所述第五晶体管均为pmos。

5.如权利要求1所述的逐次逼近式模拟数字转换器,其特征在于,所述电容阵列包括电容以及切换开关;

6.如权利要求1所述的逐次逼近式模拟数字转换器,其特征在于,所述第一晶体管和所述第二晶体管均为pmos,所述第三晶体管为nmos。

7.如权利要求1至6任一项所述的逐次逼近式模拟数字转换器,其特征在于,还包括采样扩展模块;

8.如权利要求7所述的逐次逼近式模拟数字转换器,其特征在于,所述采样扩展模块为第六晶体管;

9.如权利要求8所述的逐次逼近式模拟数字转换器,其特征在于,所述第六晶体管为nmos。

10.一种设备,其特征在于,包括如权利要求1至9任一项所述的逐次逼近式模拟数字转换器。

技术总结

本发明公开了一种逐次逼近式模拟数字转换器及设备,涉及集成电路领域,包括采样保持模块、比较模块、逐次逼近逻辑模块以及电容阵列,采样保持模块包括第一晶体管、第二晶体管以及第三晶体管。第一晶体管至第三晶体管组成动态开关结构,能够在进行参考电压与采样电压逐次比较的转换阶段将电容阵列的第一端的电压与输入信号进行隔离,即使在过压输入时采样保持模块中的第二晶体管也不会工作在亚阈值状态,从而保证电容阵列的第一端的电压的稳定性,进而保证逐次逼近式模拟数字转换器的精度。

技术研发人员:王承尧,马婉秋

受保护的技术使用者:上海集成电路研发中心有限公司

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!